# MITIGATION OF FAILURES IN HIGH PERFORMANCE COMPUTING VIA RUNTIME TECHNIQUES

#### BY

#### XIANG NI

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

#### Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor Nitin Vaidya Professor William Kramer Doctor Franck Cappello, Argonne National Laboratory

# Abstract

As machines increase in scale, it is predicted that failure rates of supercomputers will correspondingly increase. Even though the mean time to failure (MTTF) of individual component is high, the large number of components significantly decreases the system MTTF. Meanwhile, the decreasing size of transistors has been critical to the increase in capacity of supercomputers. The smaller the transistors are, silent data corruptions (SDC) are likely to occur more frequently. SDCs do not inhibit execution, but may silently lead to incorrect results.

In this thesis, we leverage runtime system and compiler techniques to mitigate a significant fraction of failures automatically with low overhead. The main goals of various system-level fault tolerance strategies designed in this thesis are: reducing the extra cost added to application execution while improving system reliability; automatically adjusting fault tolerance decisions without user intervention based on environmental changes; protecting applications not only from fail-stop failures but also from silent data corruptions.

The main contributions of this thesis are development of a semi-blocking checkpoint protocol that overlaps application execution with fault tolerance operation to reduce the overhead of checkpointing, a runtime system technique for automatic checkpoint and restart without user intervention, a holistic framework (ACR) for automatically detecting and recovering from silent data corruptions and a framework called FLIPBACK that provides targeted protection against silent data corruption with low cost.

# Table of Contents

| List of           | Figures                                                                     | V    |

|-------------------|-----------------------------------------------------------------------------|------|

| List of           | Tables                                                                      | viii |

| СНАРТ             | ΓER 1 Overview                                                              | 1    |

| 1.1               | Thesis Organization                                                         | 4    |

| CHAPT             | ΓER 2 Background                                                            | 6    |

| 2.1               | Terminology                                                                 | 6    |

| 2.2               | Study of System Logs from Supercomputers                                    | 8    |

| 2.3               | System Model: Charm++                                                       | 14   |

| 2.4               |                                                                             | 16   |

| 2.5               |                                                                             | 24   |

| CHAPT             | ΓER 3 Semi-Blocking Checkpointing                                           | 27   |

| 3.1               | 9 1 9                                                                       | 28   |

| 3.2               |                                                                             | 29   |

| 3.3               |                                                                             | 31   |

| 3.4               | -                                                                           | 36   |

| 3.5               | 1                                                                           | 40   |

| 3.6               |                                                                             | 41   |

| 3.7               | · ·                                                                         | 46   |

| CHAPT             | ΓER 4 Replication Enhanced Checkpointing for Soft and Hard Error Protection | 47   |

| 4.1               |                                                                             | 47   |

| 4.2               |                                                                             | 49   |

| 4.3               | <del>-</del>                                                                | 55   |

| 4.4               | <u> </u>                                                                    | 57   |

| 4.5               | <u> </u>                                                                    | 60   |

| $\frac{4.5}{4.6}$ | · · · · · · · · · · · · · · · · · · ·                                       | 63   |

| $\frac{4.0}{4.7}$ |                                                                             | 71   |

| 4.1               | Summary                                                                     | (1   |

| CHAPT | TER 5 Automatic Targeted Protection Against Silent Data Corruption | 72  |

|-------|--------------------------------------------------------------------|-----|

| 5.1   | Related Work                                                       | 73  |

| 5.2   | Runtime Guided Replication                                         | 75  |

| 5.3   | Selective Instruction Duplication                                  | 81  |

| 5.4   | Adaptive Protection for Field Data                                 | 82  |

| 5.5   | Evaluation                                                         | 84  |

| 5.6   | Discussion                                                         | 93  |

| 5.7   | Summary                                                            | 95  |

| СНАРТ | TER 6 Relieving Memory Pressure                                    | 96  |

| 6.1   | Related Work                                                       | 98  |

| 6.2   | Design and Implementation                                          | 99  |

| 6.3   | Case Studies                                                       | 107 |

| 6.4   | Conclusion                                                         | 116 |

| СНАРТ | TER 7 Conclusion                                                   | 118 |

| 7.1   | Contributions                                                      | 118 |

| 7.2   | Future Work                                                        | 119 |

| REFER | ENCES                                                              | 121 |

# List of Figures

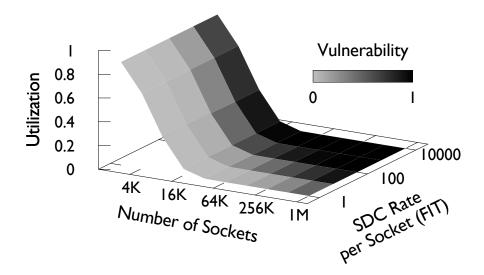

| 1.1  | Overall system utilization and vulnerability to SDC without fault-tolerance protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

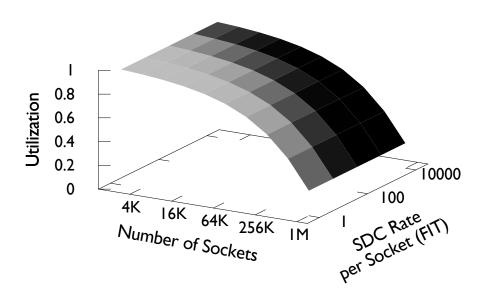

| 1.2  | Overall system utilization and vulnerability to SDC with slow checkpoint-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 1.2  | ing to file system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2  |

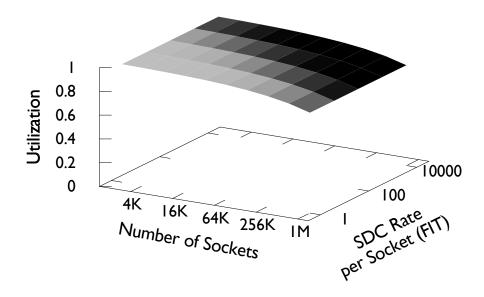

| 1.3  | Overall system utilization and vulnerability to SDC with faster checkpointing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3  |

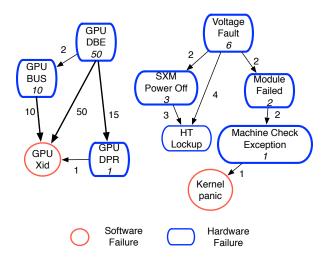

| 2.1  | Failure propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9  |

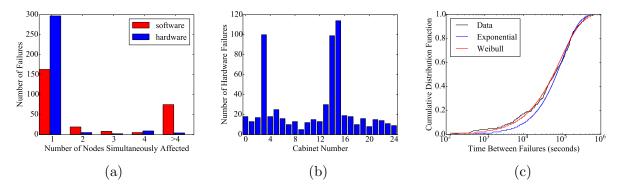

| 2.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

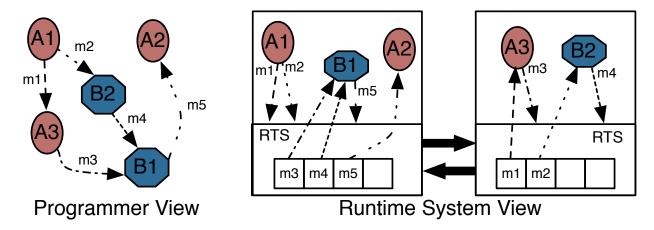

| 2.3  | Charm++ execution model: applications are written using chares (C++ objects, e.g. A1, A2, B1) that communicate via possibly remote invocation of entry methods (member functions, e.g. m1, m2, m3). The Charm++ RTS mediates both communication of messages and scheduling of compu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 2.4  | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

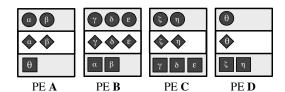

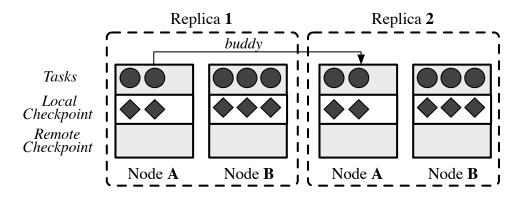

| 2.5  | Memory footprint and failure recovery in double in-memory checkpoint/restart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | Circles represent objects in application, rhombi are local checkpoints and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

| 2.6  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19 |

| 2.7  | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22 |

| 2.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24 |

| 2.9  | 9 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

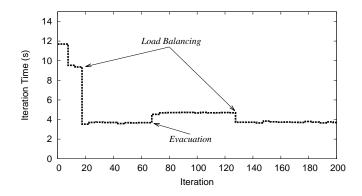

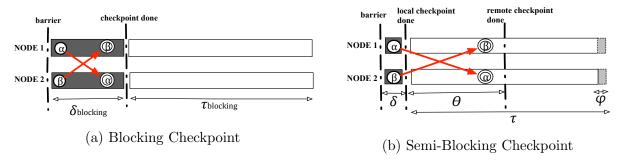

| 3.1  | ı v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

| 3.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

| 3.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

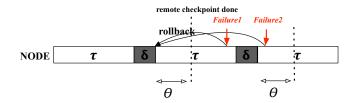

| 3.4  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

| 3.5  | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

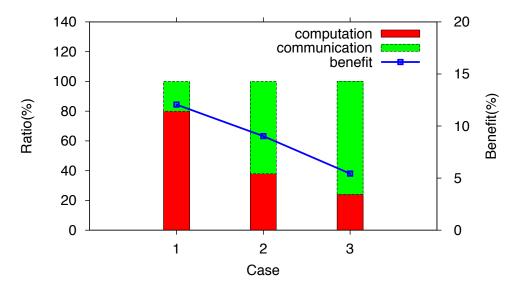

| 3.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

| 3.7  | * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

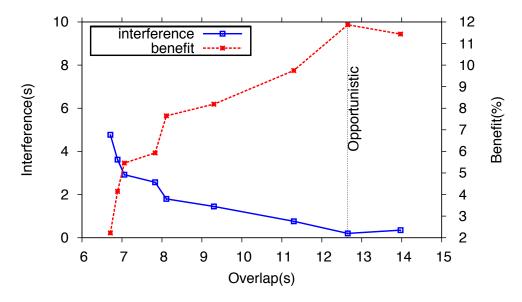

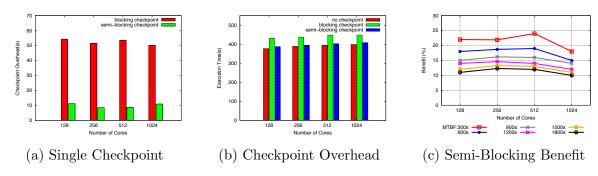

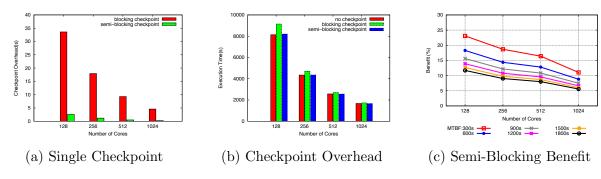

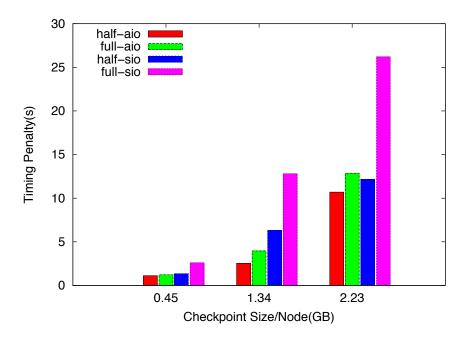

| 3.8  | O Company of the comp | 41 |

| 3.9  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42 |

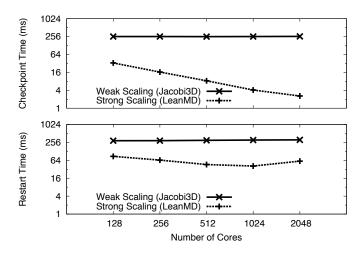

| 3.10 | V I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43 |

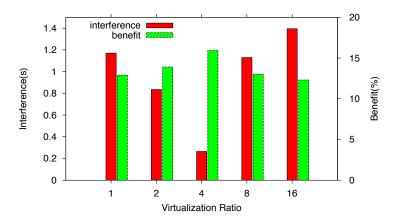

| 3.11 | Effect of virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

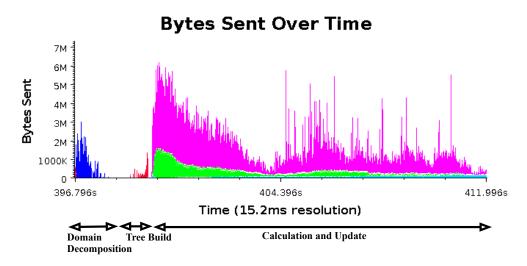

|      | v 1 C                                                                                                                                                                                                                                                            | 45<br>45 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

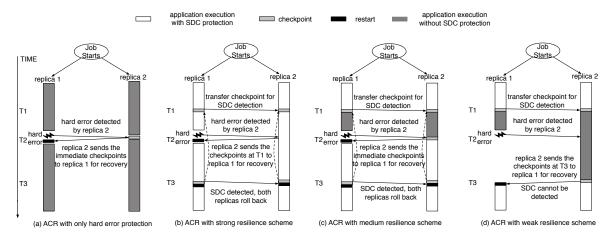

| 4.1  | Overall system utilization and vulnerability to SDC with different fault tolerance alternatives (for a job running 120 hours). ACR offers holistic                                                                                                               | 10       |

| 4.2  | protection using scalable mechanisms against SDC and hard errors Replication enhanced checkpointing. The buddy of a node is the corre-                                                                                                                           | 48       |

| 7.2  | - •                                                                                                                                                                                                                                                              | 50       |

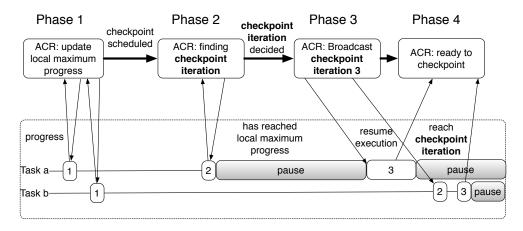

| 4.3  | 1                                                                                                                                                                                                                                                                | 52       |

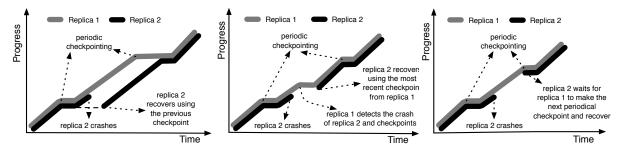

| 4.4  | Recovery in different resilience levels of ACR. Strong resilience rolls back immediately after a hard error. Medium resilience forces an additional checkpoint and restarts from there. Weak resilience waits until the next checkpoint to restore               | 53       |

| 4.5  | •                                                                                                                                                                                                                                                                | 55       |

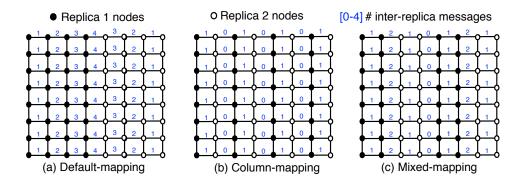

| 4.6  | Mapping schemes and their impact on inter-replica communication: the number on the links is the number of checkpoint messages that will traverse                                                                                                                 |          |

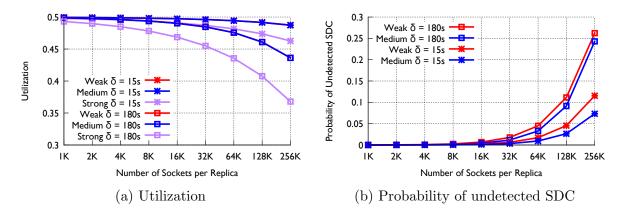

| 4.7  | through those links                                                                                                                                                                                                                                              | 59       |

|      | lization but is more likely to have undetected SDC for a large $\delta$ . Medium resilience scheme reduces the likelihood of undetected SDC with little per-                                                                                                     |          |

|      | -                                                                                                                                                                                                                                                                | 61       |

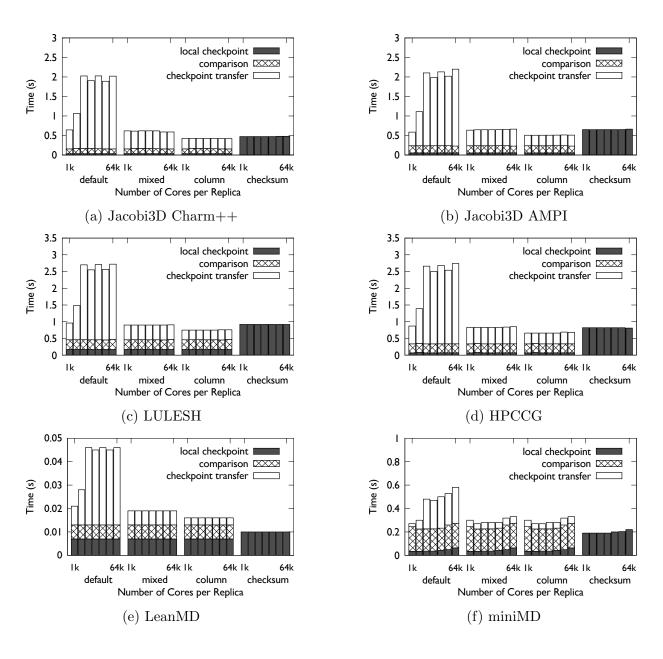

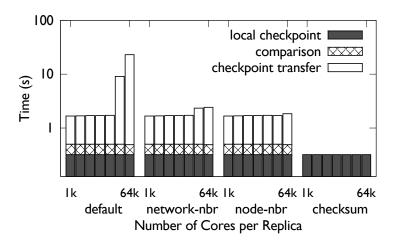

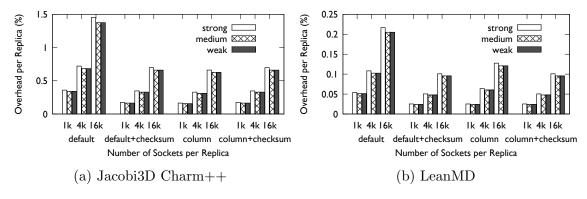

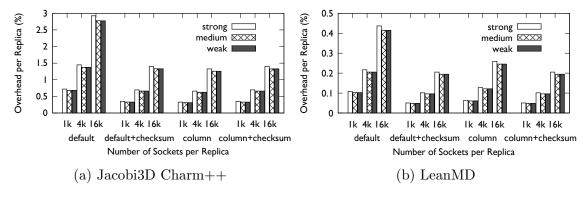

| 4.8  | Single checkpointing overhead on BGP. Our framework incurs minimal                                                                                                                                                                                               | 65       |

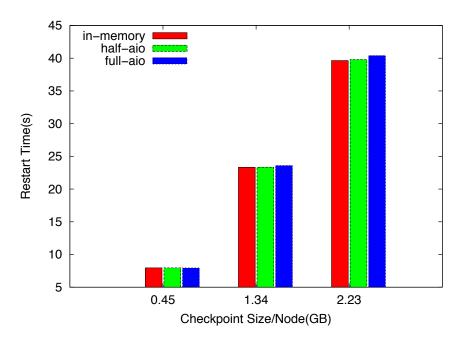

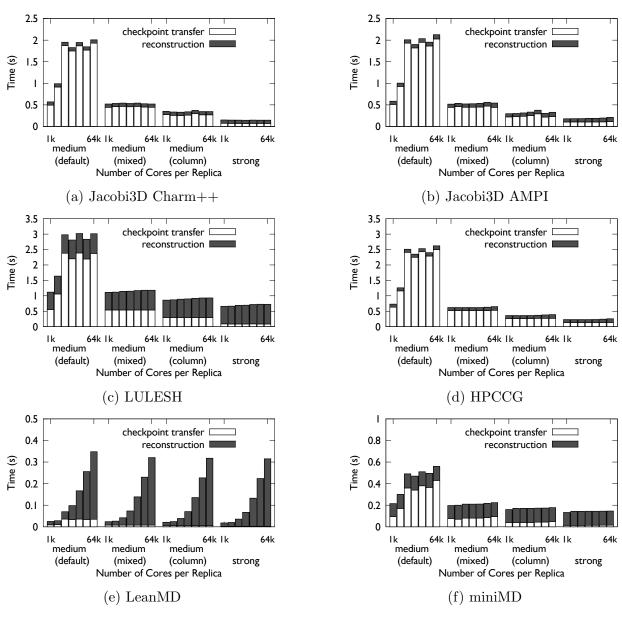

| 4.9  | •                                                                                                                                                                                                                                                                | 66       |

| 4.10 |                                                                                                                                                                                                                                                                  | 67       |

| 4.11 |                                                                                                                                                                                                                                                                  | 69       |

| 4.12 | ACR overall overhead                                                                                                                                                                                                                                             | 70       |

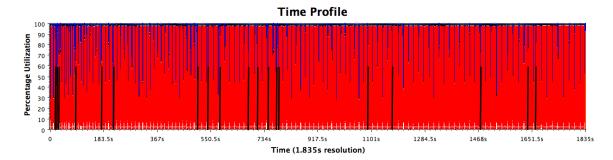

| 4.13 | Adaptivity of ACR to changing failure rate. Black lines show when failures are injected. White lines indicate when checkpoints are performed. ACR schedules more checkpoints when there are more failures at the beginning and fewer checkpoints towards the end | 71       |

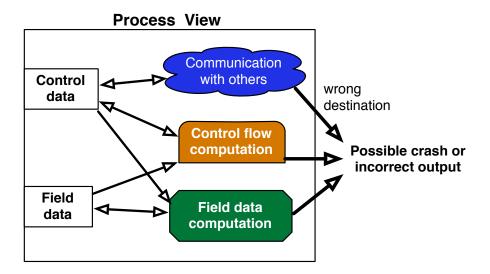

| 5.1  | Different types of data and their effect on reliability                                                                                                                                                                                                          | 73       |

| 5.2  | Code snippets from scientific applications                                                                                                                                                                                                                       | 76       |

| 5.3  |                                                                                                                                                                                                                                                                  | 79       |

| 5.4  | Illustration of the LLVM IR code after selective instruction duplication pass.                                                                                                                                                                                   | 82       |

| 5.5  | ·                                                                                                                                                                                                                                                                | 82       |

| 5.6  | •                                                                                                                                                                                                                                                                | 83       |

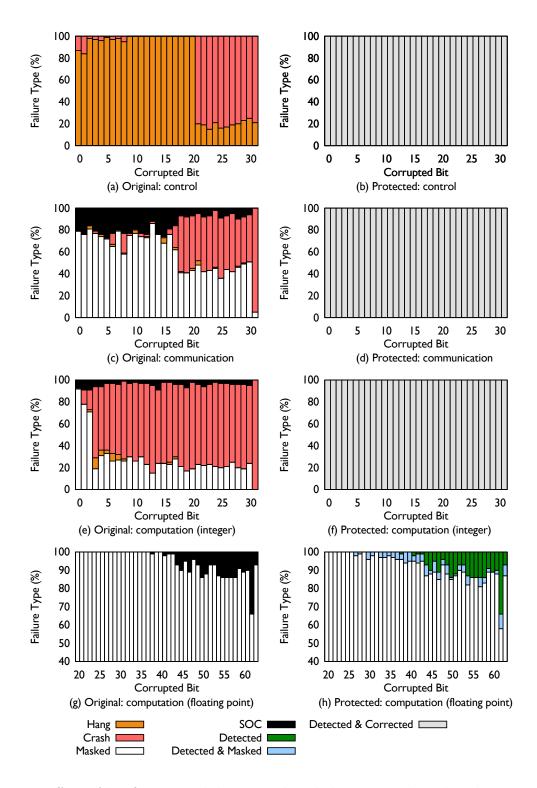

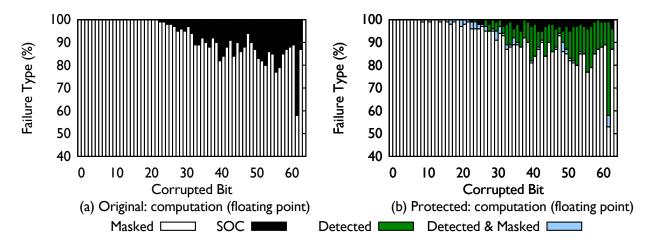

| 5.7  | Effect of bit flips on Miniaero: 3d-sod dataset with and without FLIP-                                                                                                                                                                                           |          |

|      | 1                                                                                                                                                                                                                                                                | 85       |

| 5.8  | Effects of bit flips on Miniaero: flat-plate dataset with and without                                                                                                                                                                                            |          |

|      | FLIPBACK protection                                                                                                                                                                                                                                              | 88       |

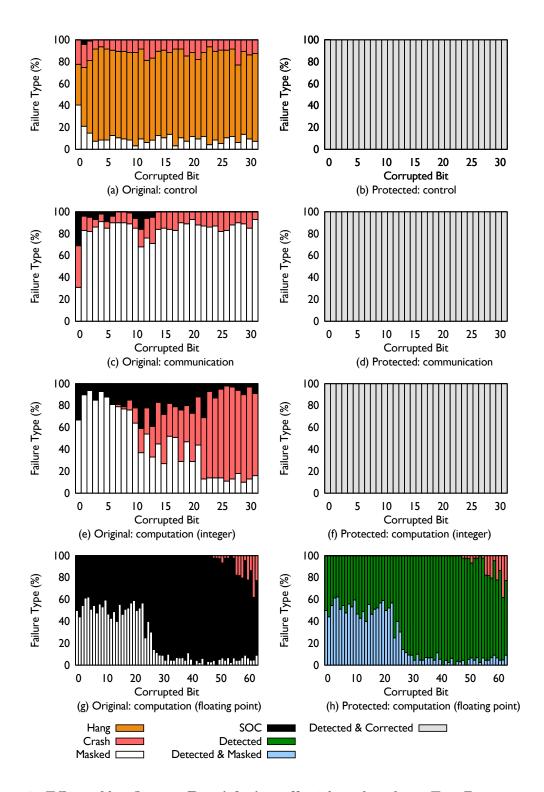

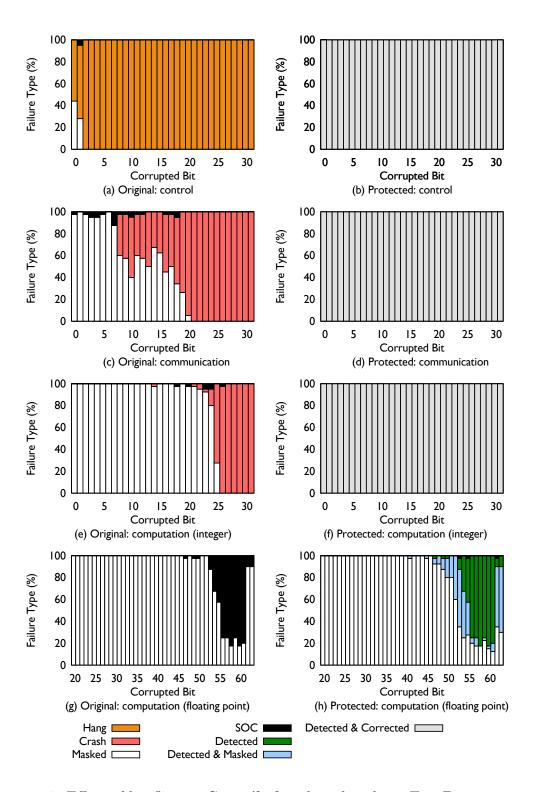

| 5.9  | Effect of bit flips on Particle-in-cell with and without FLIPBACK protection. | 89  |

|------|-------------------------------------------------------------------------------|-----|

| 5.10 | Effect of bit flips on <b>Stencil3d</b> with and without FLIPBACK protection  | 91  |

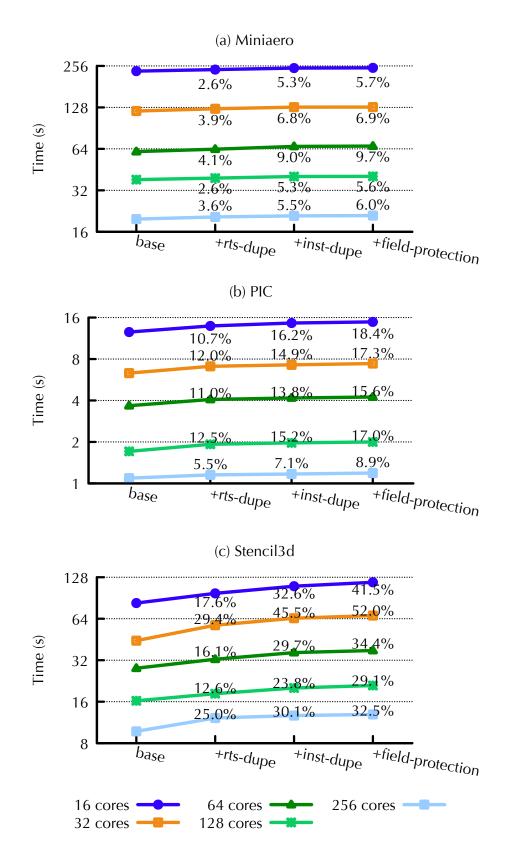

| 5.11 | Performance with different levels of protection: x-axis is functionality ag-  |     |

|      | gregated from left to right                                                   | 92  |

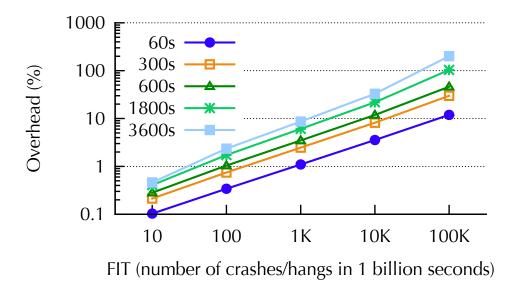

| 5.12 | Modeling the overhead of checkpoint/restart strategy for different crash/hang |     |

|      | rates and time to checkpoint                                                  | 94  |

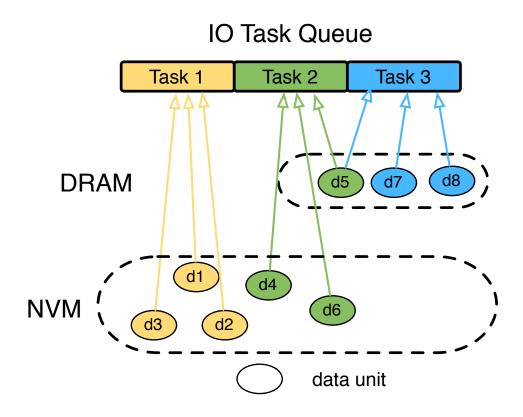

| 6.1  | Example state of data objects and computation tasks                           | 102 |

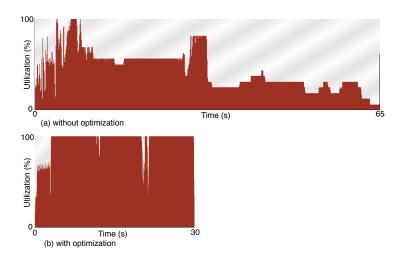

| 6.2  | Processor utilization before and after the use of shared queue                | 104 |

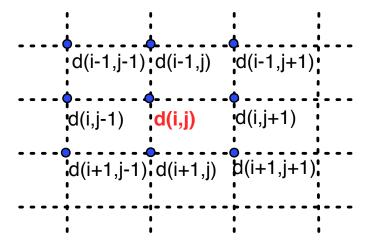

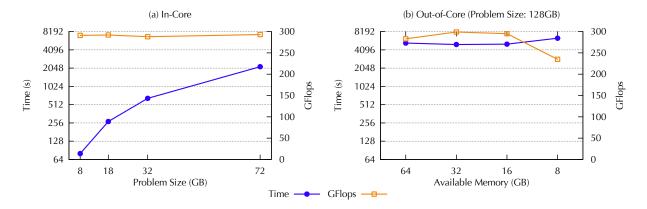

| 6.3  | Modifications in stencil program for out-of-core computation                  | 106 |

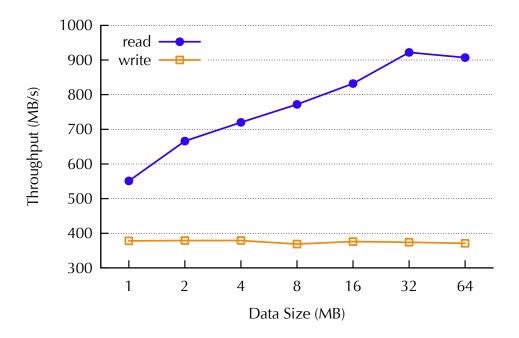

| 6.4  | Read and write performance of Comet SSD with direct IO                        | 107 |

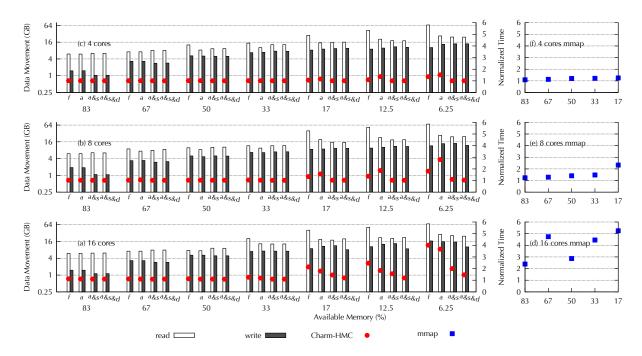

| 6.5  | Performance and data movement of using Charm-HMC for out-of-core              |     |

|      | computation using matrix matrix multiplication program (2 GB/ma-              |     |

|      | trix). The base time used to calculate the normalized time is the execution   |     |

|      | time when all the memory required is available                                | 109 |

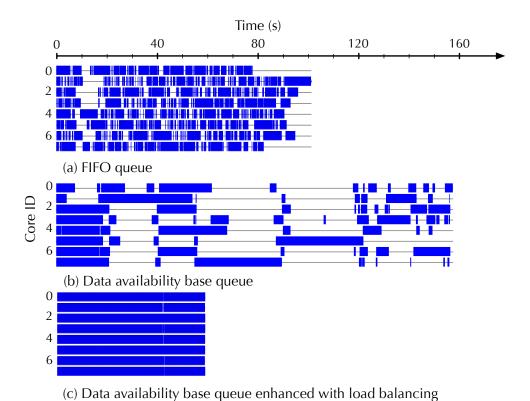

| 6.6  | Timeline profile of various optimizations using Charm-HMC on 8 cores          |     |

|      | with $6.25\%$ available memory for matrix multiplication program              | 110 |

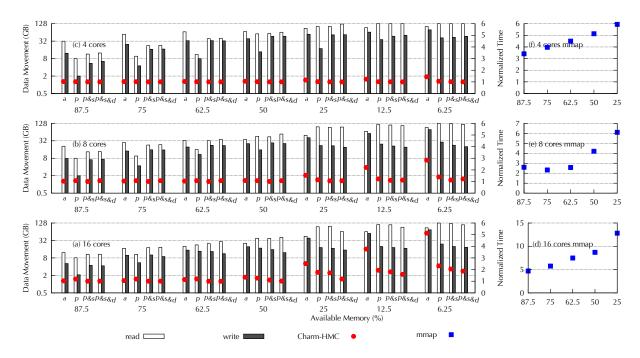

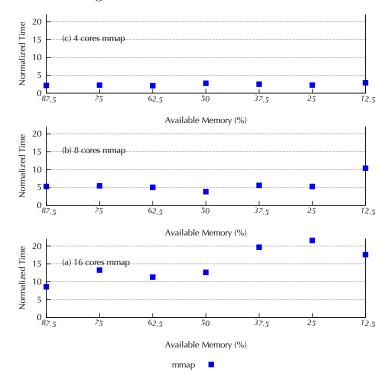

| 6.7  | Performance comparison of the runtime support for out-of-core computa-        |     |

|      | tion with mmap using LU factorization program (8 GB/matrix). The              |     |

|      | base time used to calculate the normalized time is the execution time when    |     |

|      | all the memory required is available                                          | 111 |

| 6.8  | Comparison of the out-of-core computation enabled by Charm-HMC                |     |

|      | <u>.</u>                                                                      | 113 |

| 6.9  | Performance and data movement using Charm-HMC for out-of-core sten-           |     |

|      | cil computation with one internal gauss-seidel iteration                      | 114 |

| 6.10 | Performance and data movement using Charm-HMC for out-of-core sten-           |     |

|      | cil computation with 20 internal gauss-seidel iteration                       | 114 |

| 6.11 | Performance and data movement using Charm-HMC for out-of-core sten-           |     |

|      | 1                                                                             | 115 |

| 6.12 | Performance using mmap for out-of-core <b>stencil</b> computation with 40 in- |     |

|      | ternal gauss-seidel iteration                                                 | 115 |

# List of Tables

| 2.1 | Hardware-rooted failures                                                    | 10  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | Software-rooted failures                                                    | 11  |

| 2.3 | Fast evacuation time with different data sizes                              | 23  |

|     | Parameters of checkpoint model                                              |     |

|     | putation ratios                                                             | 37  |

| 4.1 | Parameters of the performance model                                         | 60  |

| 4.2 | Mini-application configuration                                              | 63  |

| 6.1 | Explanations of the short forms of the runtime options used in experiments. | 108 |

CHAPTER 1

# Overview

Reliability is one of the most important characteristics expected from computer systems. Effectively utilizing hardware resources is difficult if faults are frequently encountered. In high performance computing (HPC), where the system comprises hundreds of thousands of components, even making sure that all components are functional at all the times is a daunting task. This is because although the mean time to failure (MTTF) of individual components is high, the aggregate MTTF of the full system is low due to the large number of system components. As a result, hardware vendors and software designers have made significant effort to enable a smooth user experience even in the presence of fail-stop failures [1].

Besides fail-stop failures, the major deterrent to achieving reliability is presence of soft errors. A soft error typically results from transient faults caused by electronic noise or high-energy particle strikes. For example, silent data corruption (SDC) may occur due to transient bit-flips [2]. SDCs are becoming more prevalent in HPC as lower power chips with smaller feature sizes are being developed. Research has shown that there exists a strong correlation between an increase in soft error rate and a decrease in device sizes and operating voltages [3]. Even recent and current systems face a modest number of soft errors. For example, ASC Q system at Los Alamos National Laboratory experienced on average 26.1 CPU failures induced by cosmic rays per week [4]. On Jaguar, double-bit errors were observed once every 24 hours in Jaguar's 360 TB memory [5].

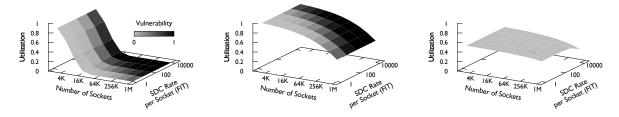

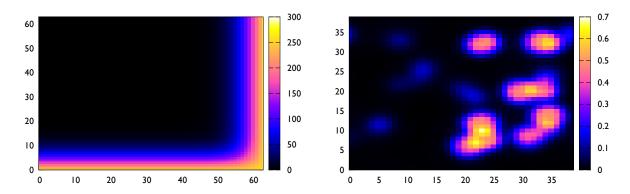

In Figure 1.1, we model the system utilization and vulnerability to fail-stop failures and silent data corruptions with different sizes of machines as well as different SDC rates using a heatmap. The underlying assumption used in Figure 1.1 is that the application runs on the whole machine and takes 120 hours to complete. The mean time between fail-stop failures for each socket is assumed to be 50 years. Since the application is running without any fault tolerance support, it needs to restart from the beginning of the execution whenever a fail-

Figure 1.1: Overall system utilization and vulnerability to SDC without fault-tolerance protection.

Figure 1.2: Overall system utilization and vulnerability to SDC with slow checkpointing to file system.

Figure 1.3: Overall system utilization and vulnerability to SDC with faster checkpointing.

stop failure occurs. Hence, as can be seen in Figure 1.1, the system utilization decreases very fast as the socket count increases. This is because the increase in socket count leads to high probability of fail-stop failures. Another trend that can be observed from Figure 1.1 is that as the socket count and the SDC rate increase, the vulnerability shown by the application becomes close to one (represented by darker color). This means that the probability of getting incorrect result is higher for these scenarios.

With all the aforementioned uncertainties, it becomes harder to ensure smooth execution of high performance computing applications. The common practice to protect applications from failures in HPC community is to periodically store the application state as checkpoints in a relatively reliable file system. However, writing the entire application state to the file system is time-consuming. As the failure rate increases, the application may easily end up spending more time on checkpoint and restart rather than performing useful computation. Also this approach fails to protect applications from silent data corruptions. In Figure 1.2, we model the system utilization and vulnerability when application performs periodical checkpoint to the file system. As can be seen from Figure 1.2, this fault tolerance strategy helps improve the system utilization compared to the case when no fault tolerance strategy is used. However, as the number of socket count increases, the utilization decreases significantly. The color pattern in Figure 1.2 is the same with Figure 1.1, which indicates that checkpointing to file system cannot help protect applications from silent data corruptions.

Thesis statement: We explore the hypothesis that runtime system and compiler techniques

can be leveraged to mitigate a significant fraction of failures automatically with low overhead. We believe that scientists, especially users of HPC applications, should mainly focus on the scientific experiments being conducted and leave it to the runtime system to mitigate failures. Specifically, we strive to solve the following research challenges in this thesis:

- Cost: How do we reduce the overhead of runtime system based failure mitigation strategies so that the performance and progress rate of applications are high with and without the occurrence of failures?