© 2016 by Nikhil Jain. All rights reserved.

# OPTIMIZATION OF COMMUNICATION INTENSIVE APPLICATIONS ON HPC NETWORKS

ΒY

NIKHIL JAIN

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor William D. Gropp Professor Josep Torrellas Professor D. K. Panda, The Ohio State University

## Abstract

Communication is a necessary but overhead inducing component of parallel programming. Its impact on application design and performance is due to several related aspects of a parallel job execution: network topology, routing protocol, suitability of algorithm being used to the network, job placement, etc. This thesis is aimed at developing an understanding of how communication plays out on networks of high performance computing systems and exploring methods that can be used to improve communication performance of large scale applications.

Broadly speaking, three topics have been studied in detail in this thesis. The first of these topics is task mapping and job placement on practical installations of torus and dragonfly networks. Next, use of supervised learning algorithms for conducting diagnostic studies of how communication evolves on networks is explored. Finally, efficacy of packet-level simulations for prediction-based studies of communication performance on different networks using different network parameters is analyzed.

The primary contribution of this thesis is development of scalable diagnostic and prediction methods that can assist in the process of network designing, adapting applications to future systems, and optimizing execution of applications on existing systems. These methods include a supervised learning approach, a functional modeling tool (called *Damselfly*), and a PDES-based packet level simulator (called *TraceR*), all of which are described in this thesis.

# Acknowledgments

First and foremost, I would like to thank my labmates and colleagues without whom it would have been impossible to keep my sanity while working for all these years. Xiang and Jonathan have played an incredibly important role in my life in last four years. All my co-authors, Bilge, Ehsan, Eric B, Eric M, Harshitha, Michael, and Ronak have helped me in more ways than I can count. Words of wisdom from the more experienced Esteban, Osman, Phil, Gengbin, Celso, Lukasz, and Abhishek have guided me well through uncertain times. Interaction with all other PPLers, Akhil, Chao, Pritish, Ram, Sam, and Yanhua has left me with a positive frame of mind more often than not.

Next, I have no words to express my gratitude towards my mentors. Prof. Kale is an amazing person, probably the most kind and positive person I have met. This thesis, and my impending research career, would not exist if not for his supervision and guidance. Abhinav's role in my growth as a researcher and in completion of this thesis is critical. He has spent countless hours discussing and developing ideas that are at the heart of this thesis. Todd has always been approachable and provided extremely valuable suggestions/feedback. Finally, I thank Yogish Sabharwal and Manish Gupta - my mentors at IBM Research India - if not for their nurturing and guidance, I may have never pursued higher studies in the US.

I would like to thank the members of my thesis committee - Prof Gropp, Prof Panda, and Prof Torrellas - for their time and feedback. I would also like to thank many other researchers who have helped me in one way or another during my thesis - Jim Phillips, Glenn Martyna, Sohrab Ismail-Beigi, Minjung Kim, Subashish Mandal, Fabrizio Petrini, Nicholas J. Wright, Kalyan Kumaran, Francesco Miniati, Mark F. Adams, Timo Bremer, Jayaraman Thiagarajan, Yarden Livnat, Misbah Mubarak, Chris Carothers, Jae-Seung Yeom, Andrew Titus, and Steven H. Langer.

Last, but not the least, I am forever indebted to my family in India for their unconditional love and encouragement.

# Grants

This work was partially supported by many funding sources and made use of resources from several supercomputing centers and projection allocations. I would like to thank all of the following sources that contributed towards completion of this work:

**Fellowship sources**: Department of Computer Science, UIUC (Andrew and Shana Laursen Fellowship, 2011-2012); IBM (IBM Ph.D. Fellowship, 2014-2015).

Assistantship sources: NSF Award 1339715; NSF Award OCI 07-25070; NSF Award OCI-0832673; Project tracking code 13-ERD-055 under US DOE Contract DE-AC52-07NA27344.

**Supercomputing centers**: Argonne Leadership Computing Facility, Argonne National Laboratory; CSCS, Swiss National Supercomputing Centre, ETH Zurich; Livermore Computing Center, Lawrence Livermore National Laboratory; National Center for Supercomputing Applications, University of Illinois at Urbana-Champaign; National Energy Research Scientific Computing Center, Lawrence Berkeley National Laboratory; Oak Ridge Leadership Computing Facility, Oak Ridge National Laboratory; Pittsburg Supercomputing Center, Carnegie Mellon University and University of Pittsburgh; Texas Advanced Computing Center, University of Texas at Austin.

Machine allocations: PEACEndStation, PARTS, HPC\_PAMS, CharmRTS (ALCF, ANL systems); PEACEndStation, ALCC (ORNL systems); DD\_jtg, ILL\_jrc, namd, PRAC\_jnk (Blue Waters, NCSA); XSEDE (PSC and TACC systems).

# Table of Contents

| 5.6   | Performance comparison                                                                                                                        | 97 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.7   | Summary                                                                                                                                       | 99 |

| CHAPT | FER 6    Comparison of Networks    1                                                                                                          | 00 |

| 6.1   | Network prototypes                                                                                                                            | 00 |

| 6.2   | Communication performance comparison                                                                                                          | 04 |

| 6.3   | Network cost comparison                                                                                                                       | 11 |

| 6.4   | Performance Per Dollar                                                                                                                        | 16 |

| 6.5   | Summary 1                                                                                                                                     | 19 |

| CHAPT | TER 7       Impact of Configuration on Performance       1                                                                                    | 21 |

| 7.1   | Stencil with unbounded resources                                                                                                              | 21 |

| 7.2   | Stencil with practical resources                                                                                                              | 25 |

| 7.3   | Spread with unbounded resources                                                                                                               | 29 |

| 7.4   | Spread with practical resources                                                                                                               | 32 |

| 7.5   | Summary and discussion                                                                                                                        | 36 |

| CHAPT | ΓER 8 Communication Algorithms                                                                                                                | 37 |

| 8.1   | Analysis of collectives on dragonfly networks                                                                                                 | 37 |

| 8.2   | Charm-FFT                                                                                                                                     | 45 |

| 8.3   | Summary 1                                                                                                                                     | 51 |

| CHAPT | $\Gamma ER 9  Conclusion  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                    | 52 |

| REFER | RENCES $\ldots \ldots \ldots$ | 54 |

# List of Figures

| 1.1        | Motivating examples for research on communication optimization                                                                                    | 2   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1        | Example hypercubes of various dimensions: note the recursive construc-                                                                            |     |

|            | tion of an <i>n</i> -dimensional hypercube using two $n - 1$ -dimensional hypercubes.                                                             | 6   |

| 2.2        | Variations of fat-tree/folded Clos topology.                                                                                                      | 6   |

| 2.3        | Torus are constructed by wrapping the corresponding grids at all boundaries.                                                                      | 7   |

| 2.4        | Dragonfly: A two-tier network with dense all-to-all connections among                                                                             |     |

|            | logical routers at each level.                                                                                                                    | 8   |

| 2.5        | Mapping of a $6 \times 5$ grid to a $10 \times 3$ mesh using different mapping strategies.                                                        |     |

|            | (source $[34]$ )                                                                                                                                  | 10  |

| 2.6        | Two stages of recursive bisection topology-adapted partition mapping.                                                                             |     |

|            | The dark lines represent the sorted node traversal order for bisection. Grid                                                                      |     |

|            | element color represents recursive bisection domains after each stage                                                                             | 11  |

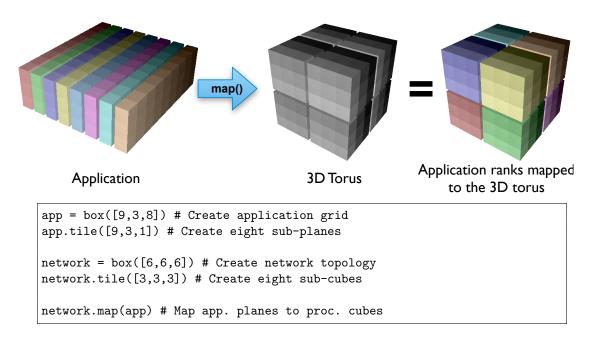

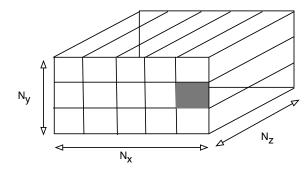

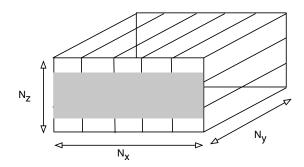

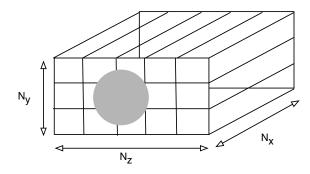

| 3.1        | Mapping 2D sub-partitions to 3D shapes in Rubik.                                                                                                  | 17  |

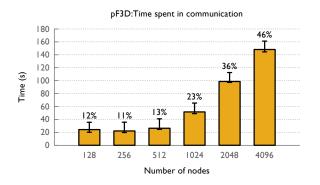

| 3.2        | Average, minimum, and maximum time spent in communication by pF3D                                                                                 |     |

|            | for weak scaling.                                                                                                                                 | 21  |

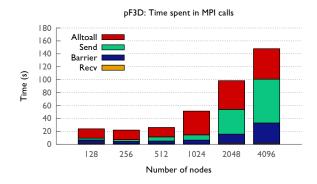

| 3.3        | Average time spent in different MPI routines by pF3D for weak scaling                                                                             | 21  |

| 3.4        | A Rubik script to generate tiled mappings for pF3D                                                                                                | 22  |

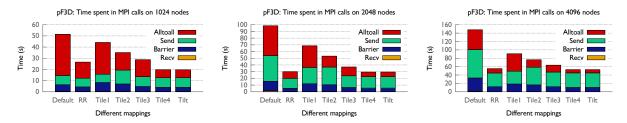

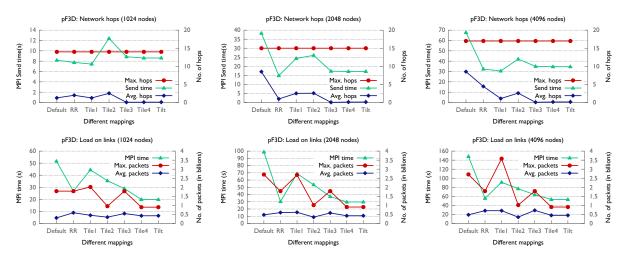

| 3.5        | Reduction of time spent in different MPI routines by using various task                                                                           |     |

|            | mappings for pF3D running on 1,024, 2,048 and 4,096 nodes of Blue                                                                                 |     |

| 2.6        | Gene/Q (Note: y-axis has a different range in each plot)                                                                                          | 23  |

| 3.6        | pF3D plots comparing the time spent in point-to-point operations to av-                                                                           |     |

|            | erage and maximum hops (top) and comparing the MPI time to average                                                                                |     |

|            | and maximum load on network links (bottom) (Note: y-axis has a different                                                                          | 0.4 |

| 0.7        | range in each plot).                                                                                                                              | 24  |

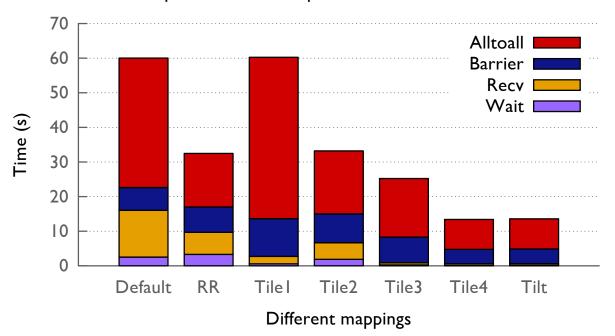

| 3.7        | Average time spent by pF3D in different MPI routines on 4096 nodes                                                                                | 25  |

| <b>n</b> 0 | (includes MPI_Isend optimization).                                                                                                                | 25  |

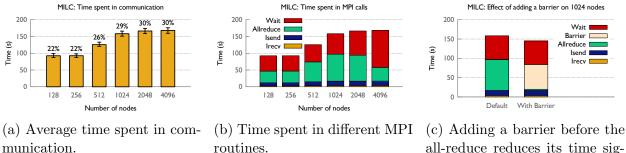

| 3.8        | Evaluation of the baseline performance of MILC with the default mapping.                                                                          | 27  |

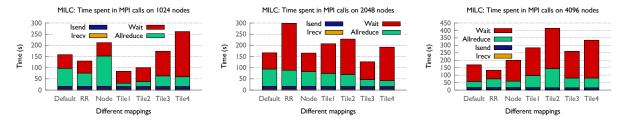

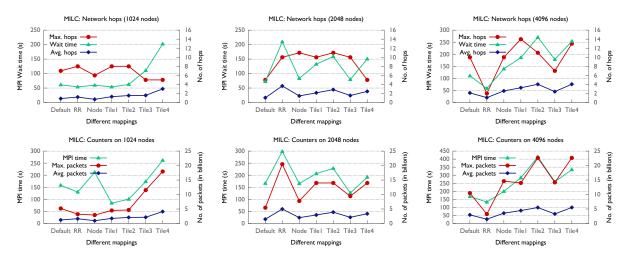

| 3.9        | Reduction of time spent in different MPI routines by using various task mappings for MILC suppings on $1024$ , 2048 and 4006 nodes of PC/O (Note: |     |

|            | mappings for MILC running on 1024, 2048 and 4096 nodes of $BG/Q$ (Note:                                                                           | 27  |

|            | y-axis has a different range in each plot).                                                                                                       | 2(  |

| 3.10 | MILC plots comparing the time spent in point-to-point operations with                                                                            |     |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|

|      | average and maximum hops (top) and the MPI time with average and                                                                                 |     |          |

|      | maximum load on network links (bottom) (Note: y-axis has a different                                                                             |     |          |

|      | range in each plot)                                                                                                                              |     | 28       |

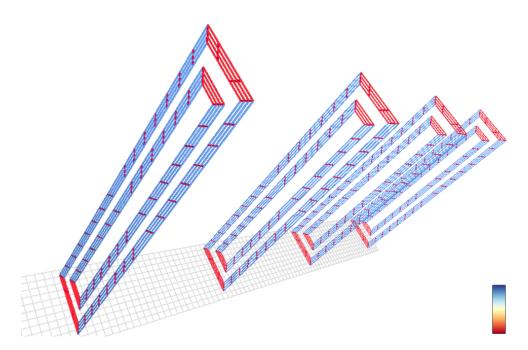

| 3.11 | Four sub-tori showing the D (blue), C (red, long), and B (red, short,                                                                            |     |          |

|      | diagonal) links for the same E. The colors represent the number of packets                                                                       |     |          |

|      | passing through individual links.                                                                                                                |     | 30       |

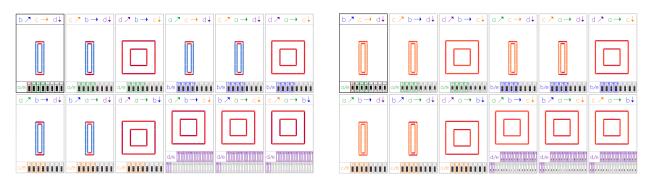

| 3.12 | Minimaps showing aggregated network traffic along various directions for                                                                         |     | 0.1      |

| 0 10 | the TABCDE (left) and the <i>Tile3</i> mappings (right)                                                                                          | ••• | 31       |

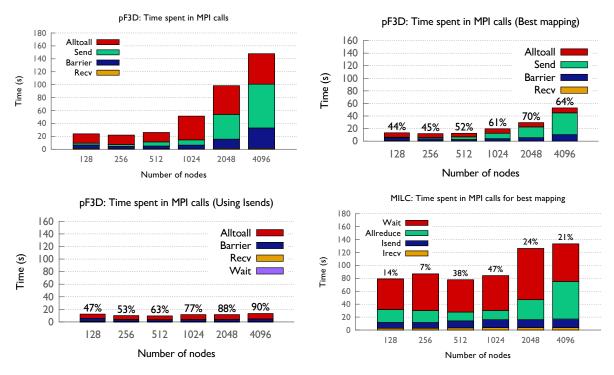

| 3.13 | pF3D: A scaling comparison of the time spent in different MPI routines<br>with the default mapping (top-left), best mapping discovered, and with |     |          |

|      | the best mapping using the Isend optimization. A scaling comparison of                                                                           |     |          |

|      | the benefits of task mapping for MILC is also shown (bottom-right). The                                                                          |     |          |

|      | percentage values shown are improvement over the default mapping                                                                                 |     | 32       |

| 3.14 | The structure of a dragonfly network.                                                                                                            |     | 34       |

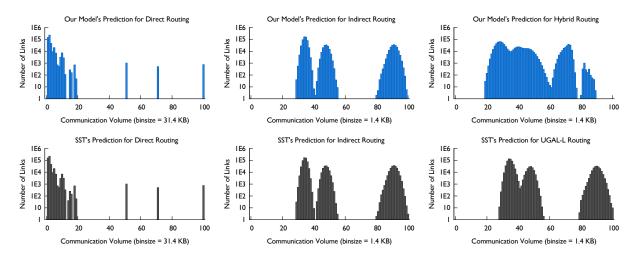

|      | Comparison of the predictions by the presented model with predictions                                                                            |     | -        |

|      | by SST/macro, a packet-level simulator, for a 4D Stencil simulated on a                                                                          |     |          |

|      | 36,864 router system.                                                                                                                            |     | 41       |

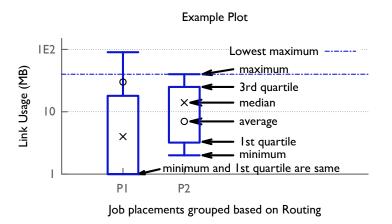

| 3.16 | Example to explain the data displayed in the plots.                                                                                              |     | 42       |

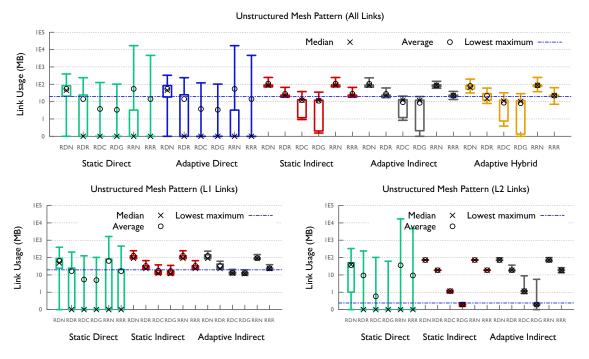

| 3.17 | Unstructured Mesh Pattern (UMesh): blocking helps in improving the                                                                               |     |          |

|      | traffic distribution.                                                                                                                            |     | 43       |

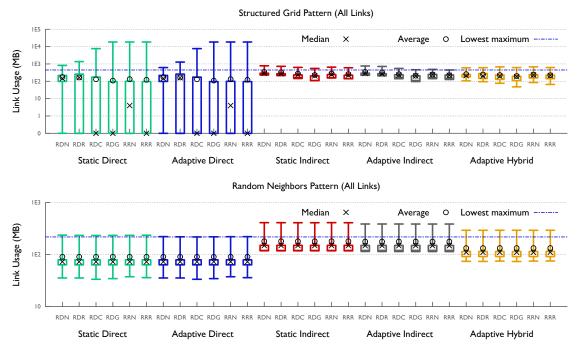

|      | Structured Grid Pattern (4D Stencil) and Random Neighbors Pattern (Spre                                                                          |     |          |

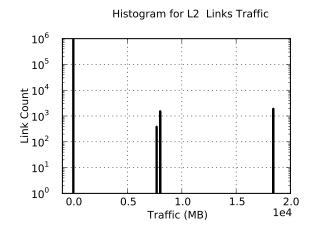

|      | 4D Stencil: distribution of traffic on L2 links for RDG                                                                                          |     | 46       |

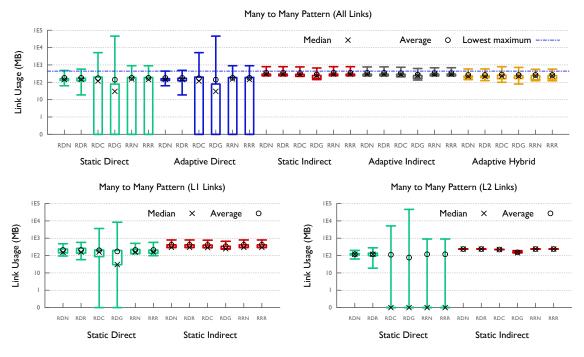

| 3.20 | Many to many pattern (M2M): direct routing with randomized placement                                                                             |     |          |

|      | has lower average and maximum traffic                                                                                                            |     | 47       |

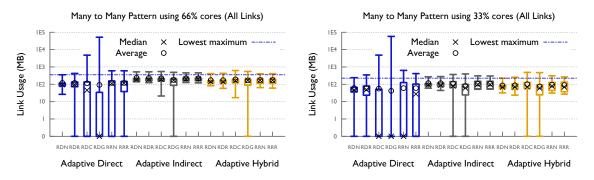

|      | Traffic distribution for M2M on 66% and 33% cores                                                                                                |     | 49       |

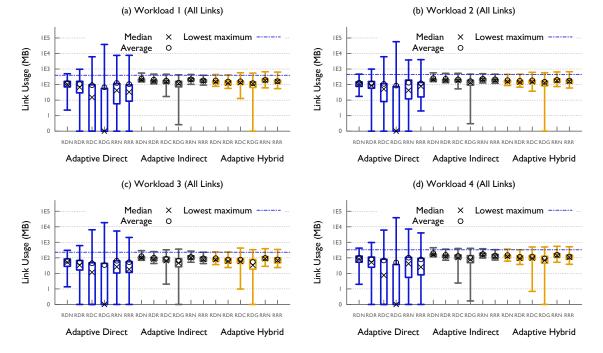

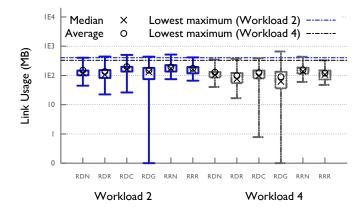

|      | Parallel workloads traffic distribution.                                                                                                         |     | 51       |

| 3.23 | Job-specific routing traffic distribution (All Links).                                                                                           |     | 53       |

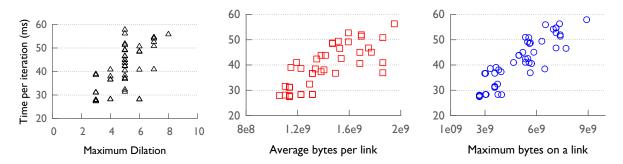

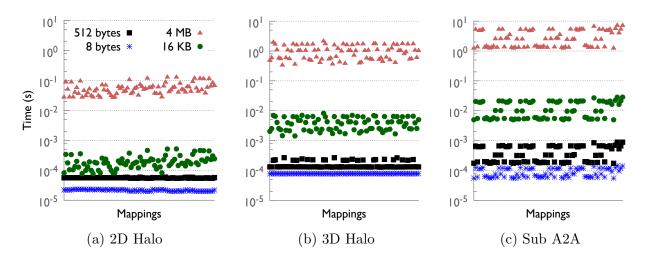

| 4.1  | Performance variation with prior metrics for five-point halo exchange on                                                                         |     |          |

|      | 16,384 cores of Blue Gene/Q. Points represent observed performance with                                                                          |     |          |

|      | various task mappings. A large variation in performance is observed for                                                                          |     |          |

|      | the same value of the metric in all three cases                                                                                                  |     | 56       |

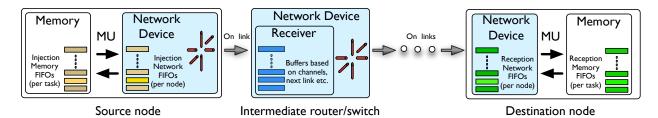

| 4.2  | Message flow on Blue Gene/Q - a task initiates a message send by putting a                                                                       |     |          |

|      | descriptor in one of its memory injection FIFOs; the messaging unit (MU)                                                                         |     |          |

|      | processes these descriptors and injects packets into the injection network                                                                       |     |          |

|      | FIFOs from which the packets leave the node via links. On intermedi-                                                                             |     |          |

|      | ate switches, the next link is decided based on the destination and the                                                                          |     |          |

|      | routing protocol; if the forward path is blocked, the message is stored in                                                                       |     |          |

|      | buffers. Finally on reaching the destination, packets are placed in network                                                                      |     |          |

|      | reception FIFOs from where the MU copies them to either the application                                                                          |     | 57       |

| 4.3  | memory or memory reception FIFOs                                                                                                                 |     | $57\\63$ |

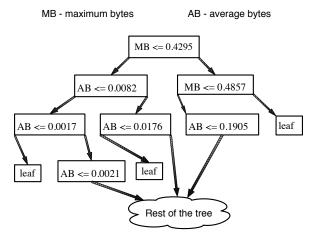

| 4.0  | Example decision tree and random forests generated using scikit                                                                                  | ••• | 05       |

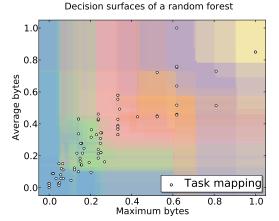

| 4.4  | Parameterized loss functions for gradient tree boosting: Huber loss func-                                                                     | 05 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4 5  | tion with the cutting-edge parameter $\delta$ (left), quantile loss function (right).                                                         | 65 |

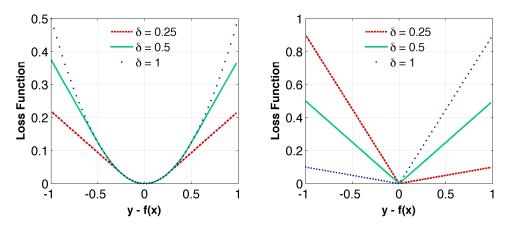

| 4.5  | Performance variations with different task mappings on $16,384$ cores of $PC/Q$ . As hereformer because more communication intensive over for |    |

|      | BG/Q. As benchmarks become more communication intensive, even for                                                                             | 67 |

| 1 C  | small message sizes, mapping impacts performance. $\dots \dots \dots \dots \dots \dots \dots$                                                 | 07 |

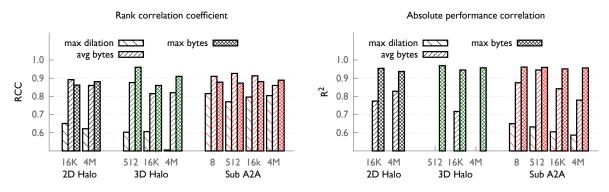

| 4.6  | Prediction success based on prior features on $16,384$ cores of BG/Q. The                                                                     | co |

| 4 7  | best RCC score is 0.91 for most cases - 38 mispredictions out of 378                                                                          | 68 |

| 4.7  | Prediction success based on new features on 16,384 cores of $BG/Q$ . We                                                                       |    |

|      | observe a general increase in RCC, but $R^2$ values are low in most cases                                                                     |    |

| 4.0  | resulting in empty columns.                                                                                                                   | 69 |

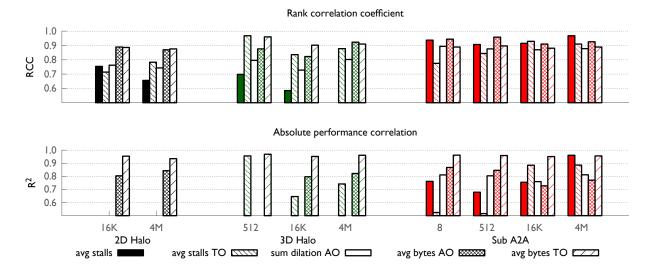

| 4.8  | Prediction success based on hybrid features from Table 4.5 on 16,384 cores                                                                    |    |

|      | of BG/Q. We obtain RCC and $\mathbb{R}^2$ values exceeding 0.99 for 3D Halo and                                                               |    |

|      | Sub A2A. Prediction success improves significantly for 2D Halo also                                                                           | 71 |

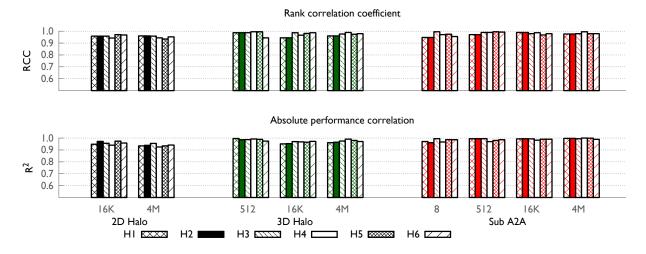

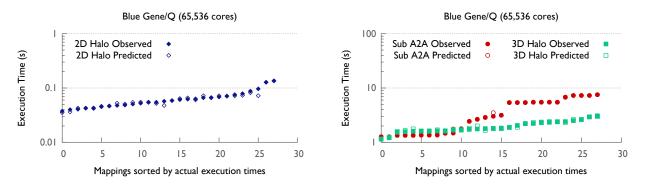

| 4.9  | Prediction success: summary for all benchmarks on $65,536$ cores of BG/Q.                                                                     |    |

|      | Hybrid metrics show high correlation with application performance                                                                             | 72 |

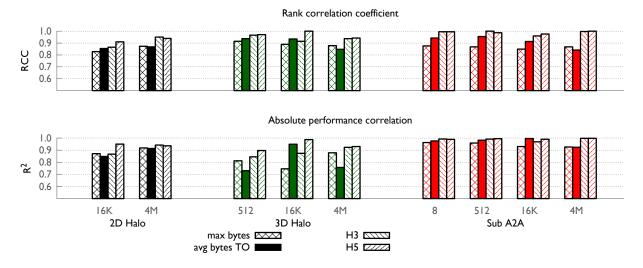

| 4.10 | Summary of prediction results on 65,536 cores using 4 MB messages. For                                                                        |    |

|      | all benchmarks, prediction is highly accurate both in terms of ordering                                                                       |    |

|      | and absolute values.                                                                                                                          | 73 |

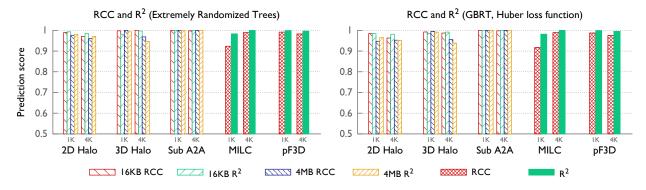

| 4.11 | Highest prediction scores obtained for the individual datasets using Ex-                                                                      |    |

|      | tremely Randomized Trees (left) and Gradient Boosted Regression Tree                                                                          |    |

|      | (right). Adjoining pairs of vertical bars represent the RCC and $\mathbb{R}^2$ values                                                         |    |

|      | for each of the sixteen datasets.                                                                                                             | 73 |

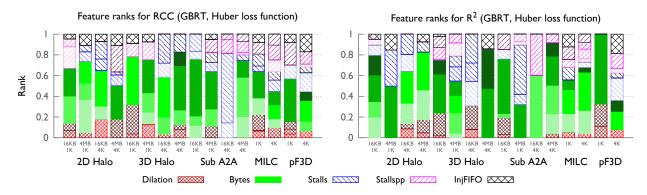

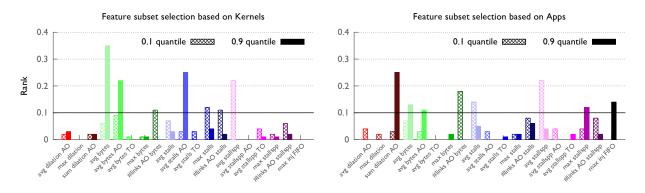

| 4.12 | Ranks of different features in the models that yield the highest RCC (left                                                                    |    |

|      | plot) and $R^2$ scores (right plot) for individual datasets using Gradient Tree                                                               |    |

|      | Boosting (loss function = 'Huber'). Each stacked bar represents the ranks                                                                     |    |

|      | of the nineteen features (colored by categories) for one of the sixteen datasets.                                                             | 74 |

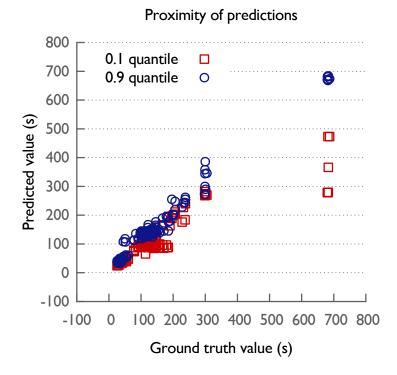

| 4.13 | GBRT regression on the Apps dataset using different quantile loss func-                                                                       |    |

|      | tions. The lower quantile regression function underpredicts for those sam-                                                                    |    |

|      | ples with high execution time, while predicting effectively for those with                                                                    |    |

|      | low execution times.                                                                                                                          | 75 |

| 4.14 | Ranks of different features obtained using GBRT with quantile loss func-                                                                      |    |

|      | tions at $\alpha = 0.1$ and $\alpha = 0.9$ respectively: left plot is for a combined set                                                      |    |

|      | of the three communication kernels (twelve datasets) and the right plot is                                                                    |    |

|      | for a combined set of the two applications (four datasets).                                                                                   | 76 |

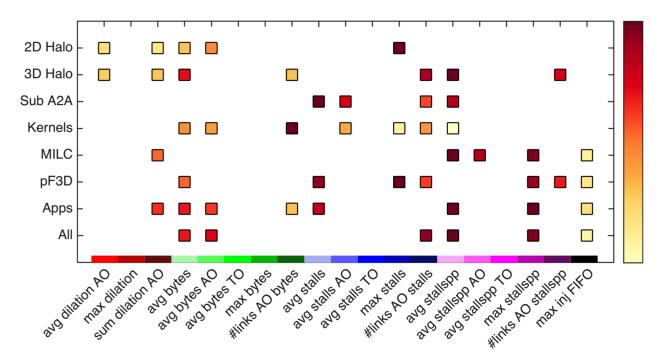

| 4 15 | Comparison of the feature ranks obtained using the feature selection tech-                                                                    | 10 |

| 1.10 | nique applied to the eight larger datasets. Note that the marker colors for                                                                   |    |

|      | each row/dataset are scaled independently (red is high and blue is low)                                                                       | 78 |

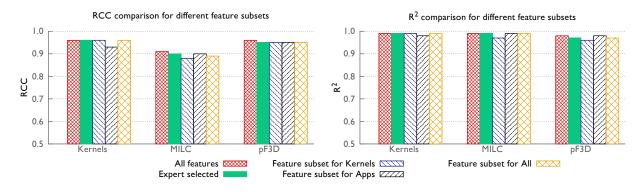

| 1 16 | Prediction performance of the features selected using the proposed quantile                                                                   | 10 |

| 4.10 | analysis on different datasets.                                                                                                               | 79 |

|      |                                                                                                                                               | 19 |

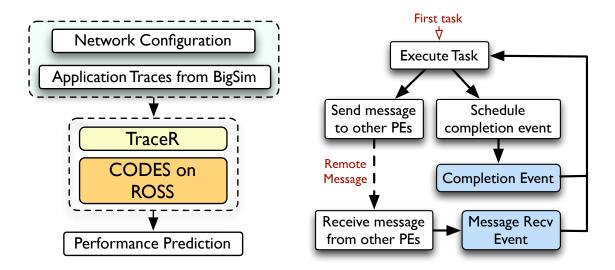

| 5.1  | Integration of TRACER with BigSim emulation and CODES (left). For-                                                                            |    |

|      | ward path control flow of trace-driven simulation (right).                                                                                    | 84 |

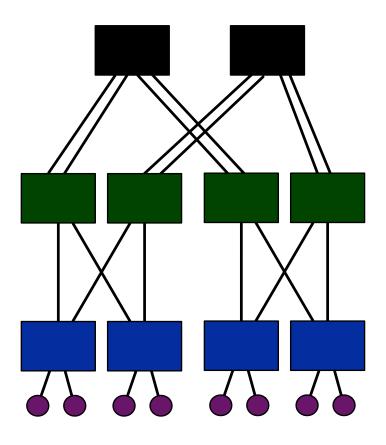

| 5.2  | Fat-tree construction using switches of same radix.                                                                                           | 88 |

| 5.3  | Optimistic vs. conservative DES                                                                                                               | 94 |

| -    | 1                                                                                                                                             |    |

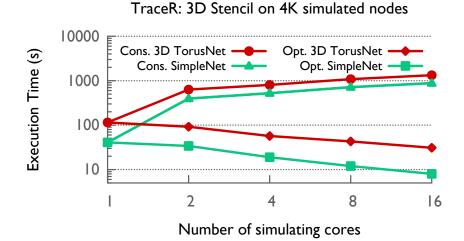

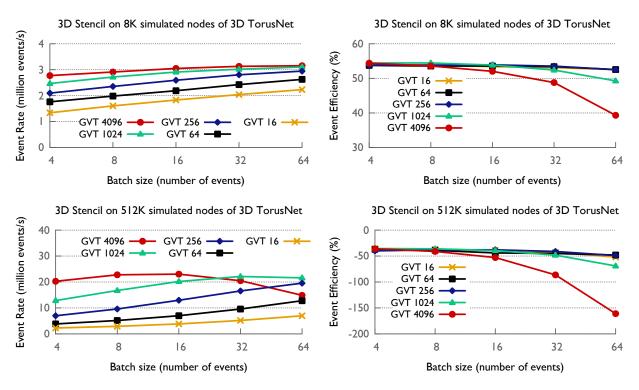

| 5.4          | Effect of batch size and GVT interval on performance: 8K simulated nodes are simulated using 8 cores (top 2 plots), and 512K using 256 cores (bottom                                                                          |   |                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|

| $5.5 \\ 5.6$ | 2 plots)                                                                                                                                                                                                                      | • | 95<br>96<br>97 |

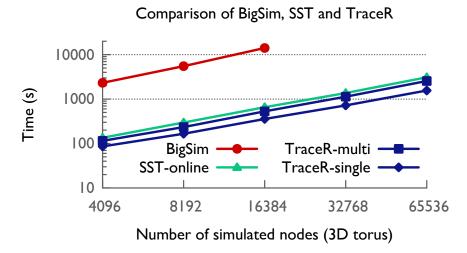

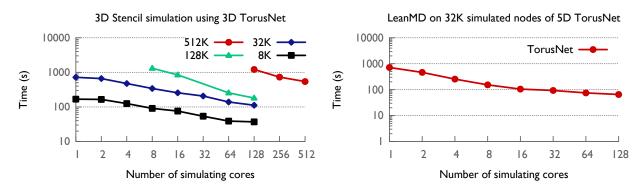

| 5.7          | Scalability of TRACER when simulating networks of various sizes                                                                                                                                                               | • | 98             |

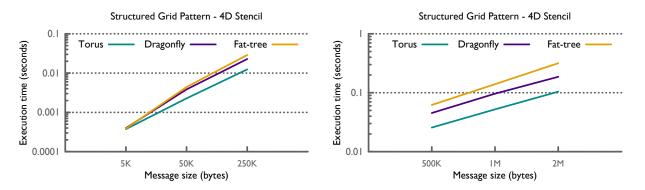

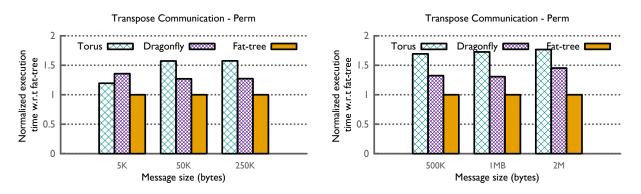

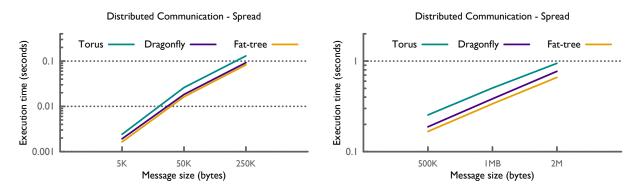

| 6.1          | Communication performance of different networks for 4D Stencil. Torus<br>outperforms dragonfly, which in turn performs better than fat-tree for<br>large message sizes. For smallest message size, all networks show similar  |   | 107            |

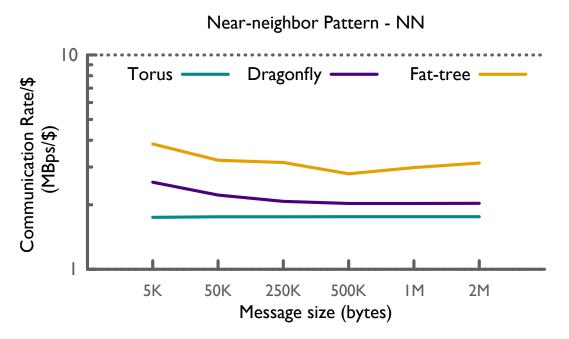

| 6.2          | performance                                                                                                                                                                                                                   | • | 107            |

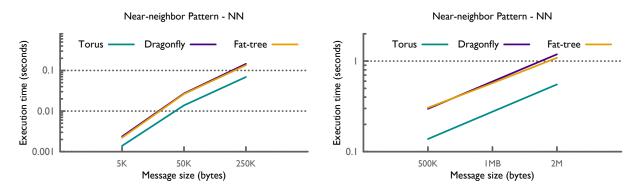

| 6.3          | dragonfly and fat-tree                                                                                                                                                                                                        | · | 108            |

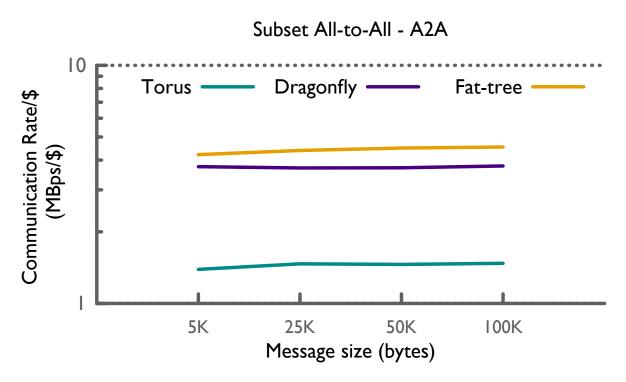

| 6.4          | worse than torus                                                                                                                                                                                                              | • | 108            |

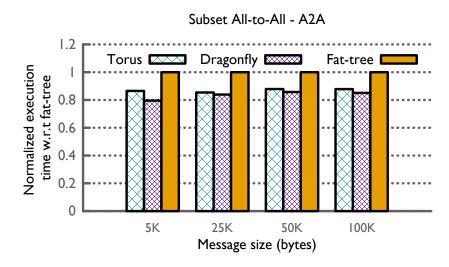

| 6.5          | which is better than torus by $\sim 25\%$                                                                                                                                                                                     | • | 109            |

|              | cantly faster than torus for all message sizes                                                                                                                                                                                |   | 110            |

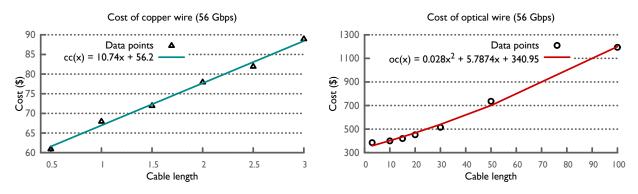

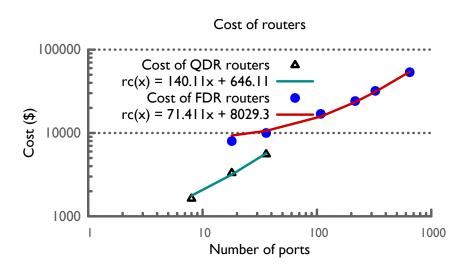

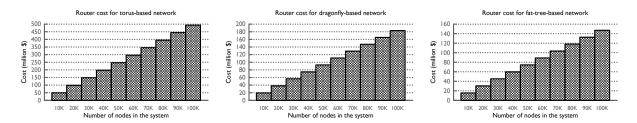

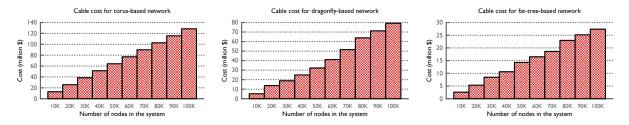

| $6.6 \\ 6.7$ | Cost model for copper and optical cables                                                                                                                                                                                      |   | 111<br>113     |

| 6.8          | Estimated router cost for building networks for prototype systems based                                                                                                                                                       | • | 110            |

|              | on different interconnect topologies.                                                                                                                                                                                         |   | 114            |

| 6.9          | Estimated cable cost for building networks for prototype systems based on                                                                                                                                                     |   |                |

| C 10         | different interconnect topologies.                                                                                                                                                                                            | • | 114            |

| 0.10         | Comparison of estimated cost for building different networks for a given<br>node count. Only router and cable cost are considered                                                                                             |   | 116            |

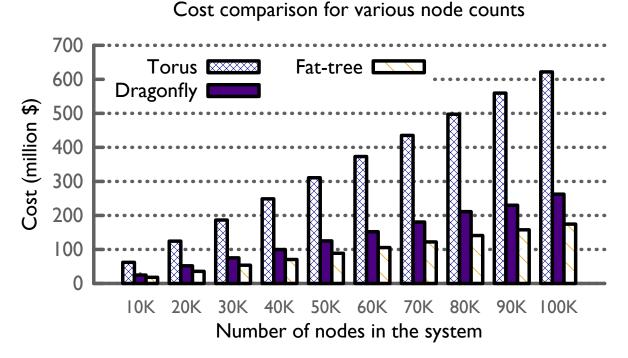

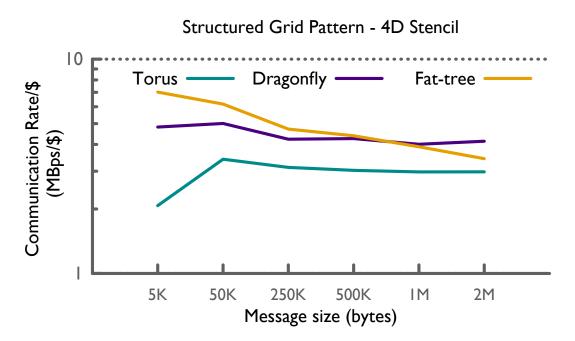

| 6.11         | Although torus provides the best performance, its performance per dollar                                                                                                                                                      | • | 110            |

|              | is worst among the three networks. As the message size increases, the                                                                                                                                                         |   |                |

|              | superior performance of dragonfly leads to a better performance per dollar.                                                                                                                                                   | • | 117            |

| 6.12         | Fat-tree shows the best performance per dollar due to its low cost, although                                                                                                                                                  |   |                |

|              | its performance is similar to dragonfly. Due to its superior performance, torus' performance per dollar is only 10% lower than the dragonfly.                                                                                 |   | 117            |

| 6.13         | Given the similar performance of all networks, performance per dollar is                                                                                                                                                      | · | 111            |

| 0.10         | significantly impacted by the cost of the networks                                                                                                                                                                            |   | 118            |

| 6.14         | The performance difference among the three network is further enhanced<br>by the cost difference. As a result, fat-tree show very high performance<br>per dollar in comparison to the dragonfly, which in turn is much higher |   |                |

|              | than the performance per dollar of torus                                                                                                                                                                                      |   | 119            |

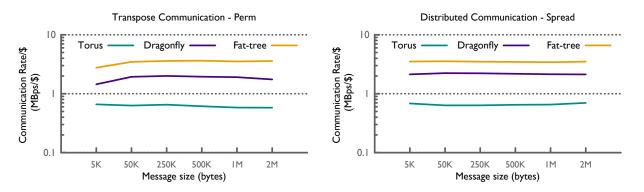

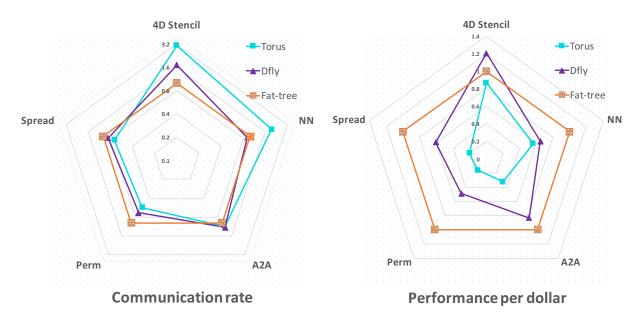

6.15 Summary of the communication rate and performance per dollar for large message sizes. Plotted values are normalized using the values for the fat-tree. 120

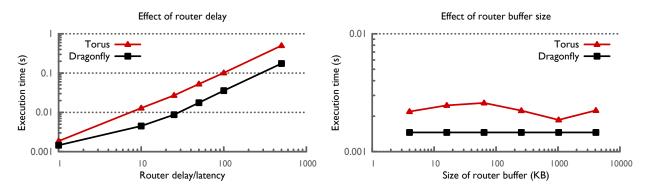

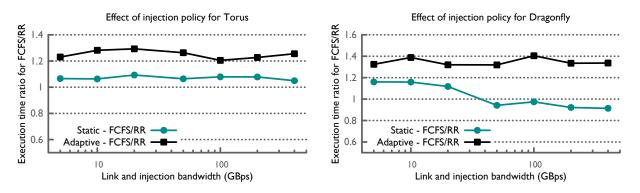

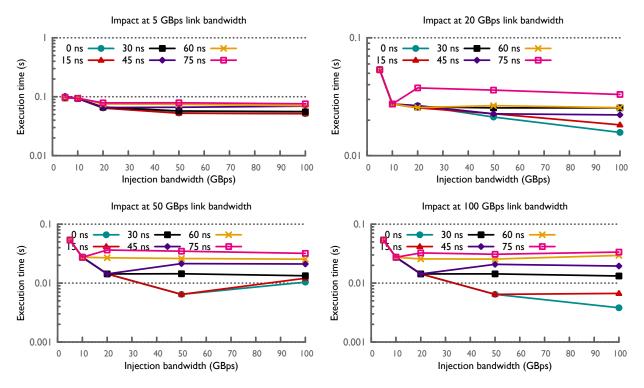

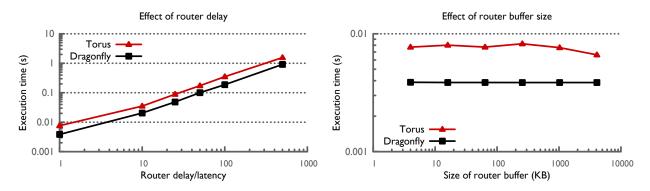

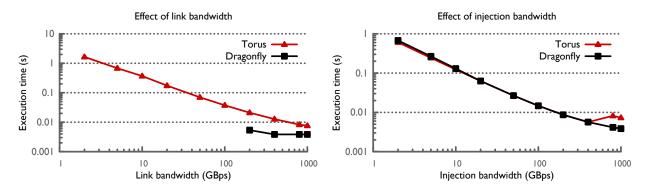

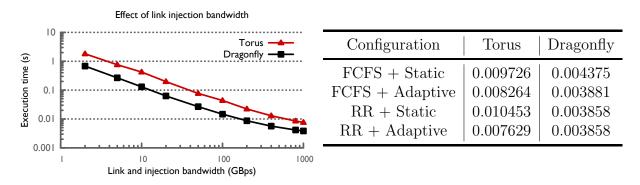

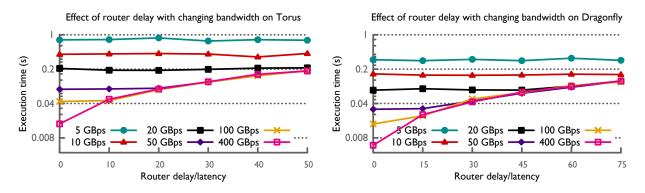

| 7.1 | (left) When all other resources are practically unlimited, the communi-<br>cation performance is directly proportional to the router delay/latency.<br>(right) Size of router buffer has no effect on the performance of the drag-<br>onfly network. Its impact on the torus network can be significant, but is                                                              | 100     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

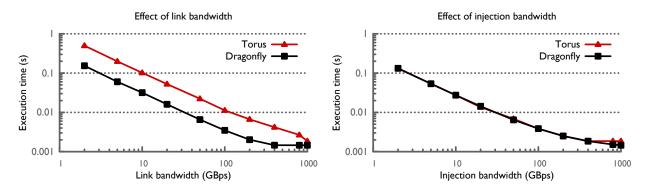

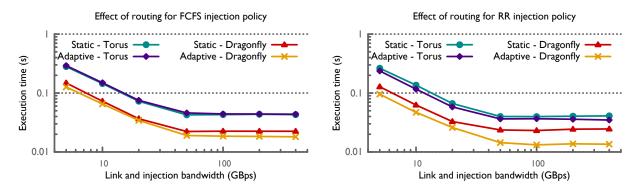

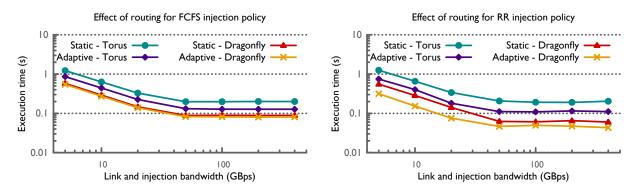

| 7.2 | hard to model                                                                                                                                                                                                                                                                                                                                                                | <br>122 |

| 7.3 | network saturates at 400 GBps                                                                                                                                                                                                                                                                                                                                                | <br>123 |

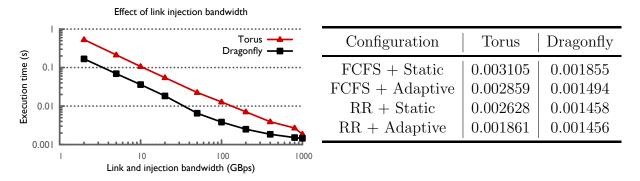

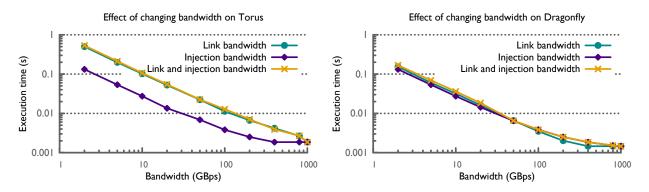

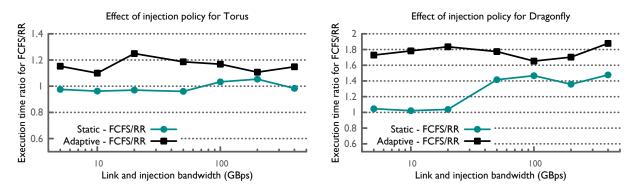

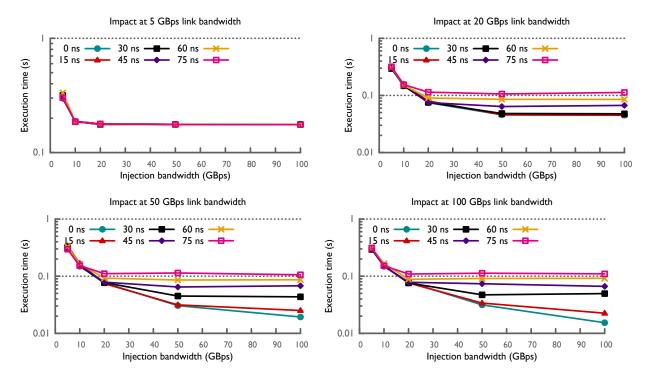

| 7.4 | contrast, on a dragonfly, good choice of one makes the other irrelevant (left) For torus, link bandwidth acts as a primary bottleneck, with injection bandwidth requirement saturating at large values. (right) For dragonfly, both link and injection bandwidth are critical, with link bandwidth being more important at lower bandwidth and injection bandwidth being the | <br>124 |

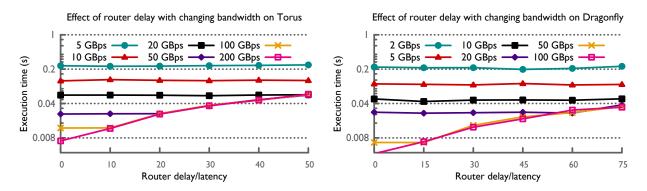

| 7.5 | bottleneck at larger values                                                                                                                                                                                                                                                                                                                                                  | <br>125 |

| 7.6 | torus and dragonfly networks                                                                                                                                                                                                                                                                                                                                                 | <br>125 |

| 7.7 | ment on a dragonfly                                                                                                                                                                                                                                                                                                                                                          | <br>126 |

| 7.8 | performance bottleneck                                                                                                                                                                                                                                                                                                                                                       | <br>127 |

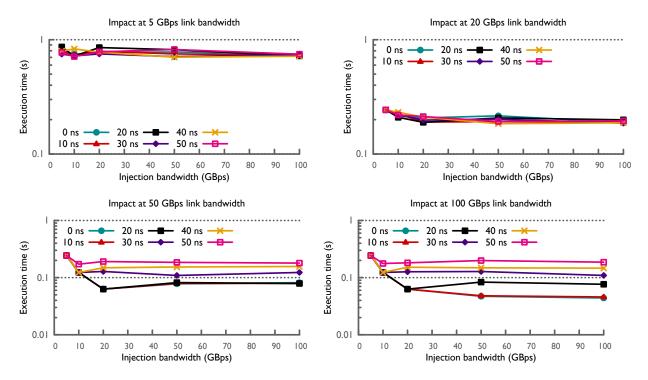

|     | very high latency can be the performance bottleneck.                                                                                                                                                                                                                                                                                                                         | <br>128 |

| 7.9          | Unlike torus, an increasing injection bandwidth impacts the execution time<br>both positively and negatively, even when link bandwidth is low. Similarly,<br>the router latency has impact on the performance even when the link and<br>injection bandwidth are relatively low.                                                                  |     | 129          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|

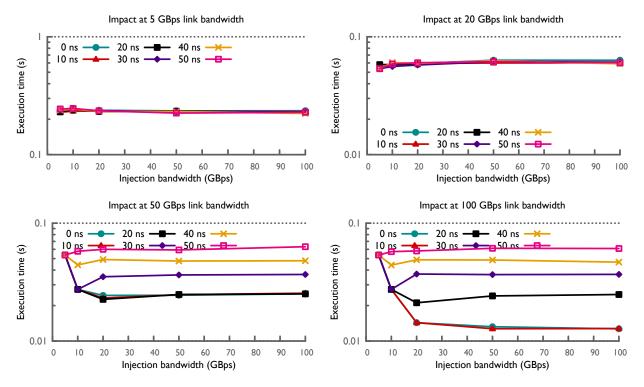

| 7.10         | (left) The execution time increases as the router latency is increased; per-<br>formance of the torus is similar to the dragonfly. (right) As for 4D Stencil,<br>size of router buffer has no effect on the performance of the dragonfly net-<br>work. Its impact on the torus network is significant, but does not follow a                     |     |              |

| 7.11         | pattern                                                                                                                                                                                                                                                                                                                                          |     | 130          |

| 7.12         | 1000 GBps. The reverse is true for injection bandwidth (left) For both torus and dragonfly, significant improvement in performance is observed, even for very large bandwidth. (right) Impact of routing policy and the injection policy: RR + Adaptive provides the best performance on torus, while only FCFS + Static performs badly on drag- |     | 131          |

| 7.13         | onfly                                                                                                                                                                                                                                                                                                                                            |     | 131          |

| 7.14         | routing is used, but FCFS shows similar performance for Static routing.<br>(right) On the dragonfly network, performance improvements are high for                                                                                                                                                                                               |     | 132          |

| 7.15         | Adaptive routing and for Static routing if the bandwidth is high<br>For low bandwidth, the router delay does not impact the execution time,                                                                                                                                                                                                      | • • | 133          |

| 7.16         | but as the router delay increases, it becomes the performance bottleneck.<br>Performance improves with increasing link bandwidth, but saturates quickly<br>when injection bandwidth is increased. Impact of latency is less prominent                                                                                                            |     | 134          |

| 7.17         | in comparison to 4D Stencil                                                                                                                                                                                                                                                                                                                      |     | 135<br>135   |

|              |                                                                                                                                                                                                                                                                                                                                                  |     | 100          |

| 8.1          | Phase 1 and 2 of Charm-FFT                                                                                                                                                                                                                                                                                                                       |     | 147          |

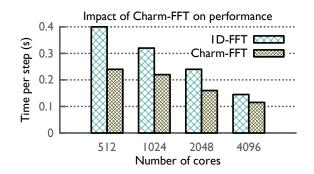

| $8.2 \\ 8.3$ | Phase 3 and 4 of Charm-FFT                                                                                                                                                                                                                                                                                                                       |     | $148 \\ 150$ |

| 0.0          |                                                                                                                                                                                                                                                                                                                                                  | • • | 100          |

# List of Tables

| 3.1 | Shape and connectivity of the partitions allocated on Vulcan (Blue Gene/Q) $$         |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | for different node counts                                                             | 20  |

| 3.2 | Tile sizes used for the Blue Gene/Q 5D torus and pF3D in different mappings.          | 23  |

| 3.3 | Details of communication patterns.                                                    | 40  |

| 3.4 | Percentage cores allocated to patterns in workloads                                   | 51  |

| 4.1 | *Prior and <sup>†</sup> new metrics that indicate contention for network resources    | 61  |

| 4.2 | List of communication metrics (features) used as inputs to the machine                |     |

|     | learning model. The colors in this table correspond to different hardware             |     |

|     | components in Table 4.1                                                               | 61  |

| 4.3 | Dimensions of the allocated job partitions on $BG/Q$                                  | 61  |

| 4.4 | Sizes of the input datasets in terms of the number of executions or samples           |     |

|     | for the different codes.                                                              | 62  |

| 4.5 | List of hybrid features that achieve strong correlations                              | 70  |

| 6.1 | Design choices for prototype systems. Specific values shown are for the               |     |

|     | systems compared in the next section. The job placement choices have                  |     |

|     | been made after comparing different types of placement schemes for each               |     |

|     | of the network.                                                                       | 104 |

| 8.1 | Commonly used algorithms.                                                             | 139 |

| 8.2 | Cost model based comparison                                                           | 143 |

| 8.3 | Link usage comparison for Scatter and Broadcast.                                      | 144 |

| 8.4 | Link usage comparison for Allgather.                                                  | 145 |

| 8.5 | Link usage comparison for Reduce-scatter and Reduce.                                  | 145 |

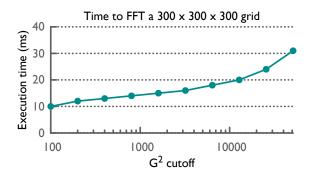

| 8.6 | Effect of decomposition on time to perform FFT on a $300 \times 300 \times 300$ grid. |     |

|     | Representative best values are shown for each of the object counts                    | 149 |

|     |                                                                                       |     |

## CHAPTER

## Overview

Efficient communication is a must for completing successful projects, even more so for parallel projects.

Communication is a necessary but overhead inducing component of high performance computing (HPC). It is imperative that it is *optimized* when parallel applications are implemented and executed in order to make the best use of large scale systems. The challenge of optimizing communication in parallel applications is analogous to the challenge of completing a multi-person project in several ways. A successful project requires many things to be done right: creation of a capable team, availability of a suitable work environment, distribution of work among the team members, coordination within the team, etc. Obtaining scalable *communication performance* requires similar tasks at multiple levels described in this section. Here, we use the term communication performance loosely to represent the impact of communication on application execution time.

The communication performance of an application is impacted by several related aspects of a parallel job execution: the network topology of the system used for the job execution, the placement of the job within the system, the message injection and reception mechanism, the routing protocol, suitability of the interaction pattern of the application executed to the network, etc. The multiplicity of these factors provides a challenge as well as an opportunity to study them and optimize performance by exploiting them; this forms a generic theme of this thesis.

As an application developer and user, optimizing for communication is also challenging due to the limited control over the system environment. Unlike the computation resources that are typically known apriori and are fully under the control of an executing application, the availability of network resources may neither be predictable nor be completely under the control of an executing application. For example, the placement of a job and the topology of

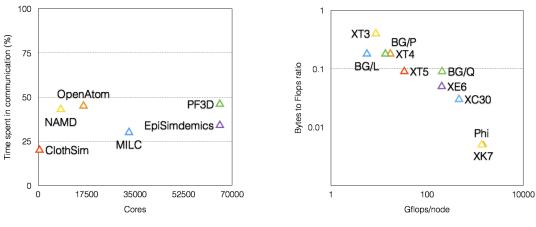

(a) Fraction of time spent in communication by scientific applications.

(b) Trend shown by bytes to flops ratio for HPC systems.

Figure 1.1: Motivating examples for research on communication optimization.

allocated nodes is decided by the scheduler based on the availability of resources. In many systems, the network resources may also be shared by multiple jobs.

As a system administrator, the goal is to make the best use of the system. Dependence of application performance on communication make this goal hard to achieve. How should the jobs be placed in the system? What parameters of the network should be universally fixed across jobs, and which should be decided by the users? Questions such as these require significant research to be answered correctly.

The diversity of the applications that are typically executed on large systems adds another level of complexity to the task of optimizing communication. Several studies, such as Kamil et al. [1], show that the communication requirements of various application classes are significantly different. Figure 1.1a shows that many of these diverse applications spend a significant fraction of time in performing communication. As a result, many types of communication optimization techniques are required to improve performance of common applications.

Finally, what makes studying communication performance more important than ever is the increasing scarcity of network resources. In Figure 1.1b, the x-axis represents the computation capability of a node in a given system, while the y-axis shows the bytes (injection bandwidth) to flops ratio (B/F ratio). This ratio, which represents the communication capability vis-a-vis the computation capability, is computed by dividing the injection bandwidth of a node with its computation capability. The trend is easy to notice in Figure 1.1b: as the capability of nodes have increased, the B/F ratio has gone down. In other words, as nodes have become computationally more capable in last 10 years ( $256 \times$  increase from Blue Gene/L to Xeon Phi), the B/F ratio has gone down from 0.18 to 0.005.

In summary, optimization of communication for parallel application is a multi-facet challenge, in part due to the multitude of the factors that impact communication performance, and in part due to the diversity of the use cases. As a result, this thesis consists of efforts that have been directed towards developing a better understanding (and associated tools) of different aspects of communication on HPC networks. Broadly speaking, the presented work aims at achieving the following three goals: improve runtime configuration and environment to facilitate communication, propose prediction tools and explore their applications in understanding and optimizing communication performance, and develop software that uses communication-aware algorithms.

A recurring theme in many of the chapters in this thesis is the use of *prediction* methodologies. As supercomputers continue to become larger and more complex, the prevalent practice of customized hand-tuning of applications and testing on production systems is no longer sufficient for efficient parallel executions. This is because such optimizations may take a significant fraction of the available life time of an expensive machine. Additionally, one will have to wait to start doing the tuning until the machine is available. Thus, prediction tools based on data analytics, functional modeling, and detailed simulation are a must to make the best use of systems we have today. Moreover, these tools are required in various ways at different stages of system and application development: during the design of machines with targeted applications being brought into the fold, during offline analysis and optimization of applications, and finally when the applications are launched and executed. Different chapters in this thesis present few such tools, and demonstrate their efficacy for the aforementioned use cases.

#### 1.1 Thesis organization

**Chapter 2** presents background and related work on six sub-topics that are closely related to communication and are repeatedly visited in the following chapters. These sub-topics are: common topologies in HPC networks, prevalent interaction or communication patterns, task mapping and job placement, metrics for modeling performance, simulation tools, and communication-centric algorithms.

Chapter 3 is focused on the problem of task mapping and job placement on the torus and dragonfly networks. For the torus network, which has been studied extensively in the past, this chapter suggests a three-step methodology to prepare applications for efficient production runs. A modeling-based prediction tool, Damselfly, and job placement studies based on it are the primary contributions of this chapter for the dragonfly network.

**Chapter 4** proposes use of machine learning to correlate observed communication performance with various measured and estimated metrics. For many communication kernels and production applications, this chapter shows that the execution time is strongly correlated to a small set of metrics, and fast prediction models can be built using large training sets.

**Chapter 5** presents a packet-level network simulator, TRACER, which is a successor to BigSim. By combining BigSim, CODES, and ROSS, TRACER provides a scalable way of simulating large scale networks for real applications accurately. Additionally, it can be used to generate input data for machine learning based methods in a fast manner when its fidelity is reduced.

Chapter 6 makes use of TRACER to compare three commonly used network topologies at the scale of the next generation supercomputers: torus, fat-tree, dragonfly. Using a set of benchmarks and cost prediction models, this chapter provides insights about performance capabilities and cost efficiency of these networks. Such studies can be important when networks are being compared for building future systems.

**Chapter 7** also uses TRACER to study the impact of various network configuration parameters, such as link bandwidth, router delay, etc., on the performance of two mini-applications. Via these case studies, this chapter proposes a generic methodology that can be used to study network designs and understand the changes in network behavior because of individual configurations. Using this method, optimal network configuration parameters can be obtained in an efficient manner.

**Chapter 8** is dedicated to communication-centric algorithms and software. The first part of this chapter discusses topology-aware algorithms for performing collectives on the dragonfly network. The second part of this chapter presents a 2D-decomposition based FFT library, which provides high performance by utilizing the network better.

Finally, **Chapter 9** summarizes the presented work and suggests possible directions for future work.

# CHAPTER 2

# Background and Related Work

Significant amount of research has been done on communication and networks for parallel computing in general, and for HPC in particular. This chapter provides a background and summarizes the past work relevant to various topics that this thesis is closely associated with. These topics are divided among the following sections: Topologies in HPC networks 2.1, Interaction patterns 2.2, Task mapping and job placement 2.3, Indicators of performance 2.4, Offline performance prediction 2.5, and Communication algorithms 2.6.

## 2.1 Topologies in HPC networks

Parallel computers have been built upon many types of interconnection topologies in the last three decades or so. At the one end of spectrum are the linear topologies where n - 1 links are used for connecting n routers (or nodes). A *star* or a linear chain are examples of this type. The other extreme is the *full* topology in which every router is connected to every other router. As expected, most of the real systems deploy network topologies that are between these extremes. In this thesis, we pay attention to four of these topologies that have commonly been used in large scale supercomputers: hypercube, fat-tree, torus, and dragonfly.

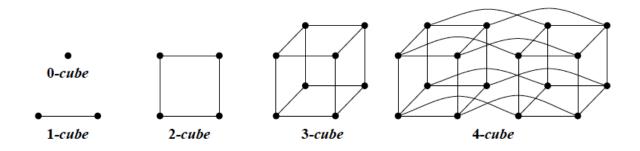

**Hypercube**: Geometrically speaking, hypercubes are *n*-dimensional analog of squares and cubes wherein each dimension is of length two. An *n*-dimensional hypercube consists of  $2^n$  nodes (or vertices) with log *n* neighbors per node. A hypercube of *n* dimensions can be defined recursively in terms of two (n - 1)-dimensional hypercubes: take two (n - 1)-dimensional hypercubes and connect the corresponding nodes. Many large supercomputers in the late eighties and nineties, such as nCUBE [2], used hypercubes as their network's

Figure 2.1: Example hypercubes of various dimensions: note the recursive construction of an *n*-dimensional hypercube using two n - 1-dimensional hypercubes.

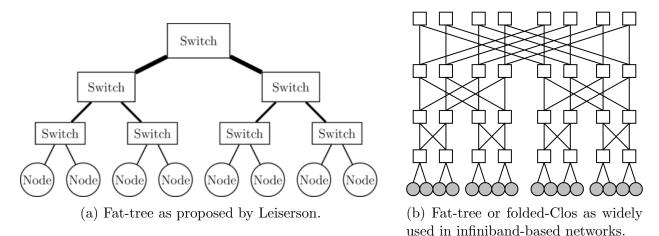

Figure 2.2: Variations of fat-tree/folded Clos topology.

topology. Figure 2.1 shows hypercubes of up to four dimensions and highlights the recursive construction of hypercubes.

Fat-tree, Folded-Clos and variations: Fat-tree topology was proposed by Leiserson as a network with provably efficient communication [3]. The key idea behind the fat-tree network is the following: in a tree topology, the loads on the links increase as we approach the root; thus link bandwidth should be higher for the links closer to the root (Figure 2.2a). The Connection Machine [4] was based on this topology. In terms of practical deployment, fat-tree requires the switches closer to the root to have more ports to support more links. This makes the construction more expensive as building switches with large number of ports is costly. Figure 2.2b shows a variation of fat-tree (which can also be viewed as a folded-Clos [5]) that builds a fat-tree using switches with smaller radix. The key idea here is to replace the fat switches near the root with many smaller switches that logically behave as one big switch. This topology has been widely adopted for deployment of infiniband-based supercomputers [6,7].

(b) IBM's construction of 5-D torus (source: [14])

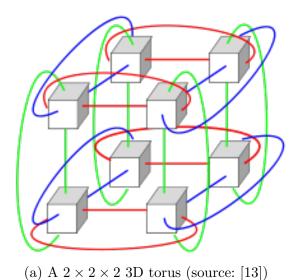

Figure 2.3: Torus are constructed by wrapping the corresponding grids at all boundaries.

**Torus**: In geometry, a torus is 3-dimensional structure generated by revolving a circle about an axis coplanar with the circle [8]. A generic *n*-dimensional torus can be viewed as an extension of a *n*-dimensional grid where the edges are wrapped around to form rings. It can also be viewed as a *k*-ary *n*-cube. Figure 2.3 shows two tori - one of dimension 3 and other of dimension 5. Torus of various dimension (two to six) have been used in many supercomputers in the last decade [9–12]. Note that commonly deployed torus are asymmetric form of *k*-ary *n*-cube, where the length of each dimension (the k's) can be different.

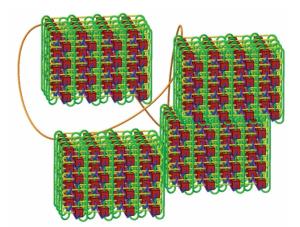

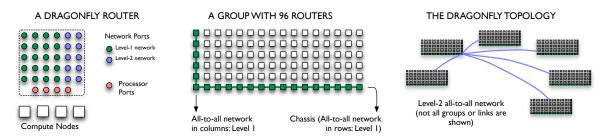

**Dragonfly**: Invented by Kim et al. [15], dragonfly is a multi-level dense topology aimed at making use of high-radix router. A typical dragonfly consists of two levels of connections. At the first level, routers are connected via a dense topology, e.g. an all-to-all, to form groups. The groups behave as virtual routers which are then again connected in an all-to-all manner (Figure 2.4). Dragonfly and its variations have been used in recent supercomputer networks such as Cray's XC30 [16], IBM PERCS [17], etc.

## 2.2 Interaction patterns

Communication patterns of various HPC applications can be significantly different. In their survey of many common applications, Kamil et al. [1] found that the average number of communicating neighbors per core can range from 6 to 256 for different applications executed on 256 cores. In addition to the variation in the number of communicating neighbors, the

Figure 2.4: Dragonfly: A two-tier network with dense all-to-all connections among logical routers at each level.

choice of neighbors has also been shown to be significantly different. As a result, at one end of the spectrum, processes (or nodes) in HPC applications can have less than 10 neighbors all of which are close to them in terms of the given rank space (and topology). On the other hand, many applications, including the ones that perform parallel FFTs, have all-toall communication pattern within large subsets of processors that may be far away from each other. To account for these variations, most studies in this thesis have been performed on a set of benchmarks and applications that are representative of distinct communication sets. Here, we provide generic descriptions of these representative patterns:

**Permutation/Transpose**: In this pattern, each process communicates with only one other process in a given phase of application. The selection of paired processes is often dependent on the input to the application, and may change as the application's phase changes. For example, in a multi-phase transpose of matrix distributed among a 2D grid of processes, every process interacts with a different process in each of the phase of the transpose operation. Given the data-dependent nature and presence of multiple permutations during an application execution, topology aware mapping of communicating processes is difficult to achieve. Thus, this operation often leads to large hop-counts for each message transferred and stresses the bisection bandwidth of the network.

**nD-Stencil**: Structured grid based near neighbor communication is one of the most commonly found communication pattern in parallel applications. A nD-Stencil pattern overlays the processes onto a nD-grid. Every process in the grid communicate with 2n nearestneighbor, two in each dimension. Example applications with such patterns include WRF [18] (2D-Stencil), MILC [19] (4D-Stencil), pF3D [20] (1D- and 3D-Stencil), etc.

Unstructured Near-neighbor: This pattern is the unstructured form of nD-Stencil. A typical formulation consists of an unstructured mesh divided among processes along the mesh edges. As a result, processes have different number of neighbors with whom they may communicate different amount of data. Another scenario which results in this pattern is when certain processes multicast their data to a small subset of processes that are mapped close to them. Example applications with such patterns include material modeling, Cloth Simulation [21], OpenAtom [22], etc.

Many-to-Many/A2A: When a subset of processes communicate among themselves in an all-to-all manner, we obtain the many-to-many communication pattern. Presence of parallel FFT operation often leads to such a pattern in many application such as NAMD [23], pF3D [20], Qbox [24], OpenAtom [22], etc. Parallel IO, parallel sorting, and other similar operations also result in many-to-many communication pattern.

Uniform Spread: In this pattern, every process communicates with a few other processes that are selected randomly from the remaining set of processes. One can also view this pattern as multiple permutation patterns communicating simultaneously. While less commonly induced by application requirement, the uniform spread is commonly observed due to the way jobs are placed by the job scheduler. For example, consider an application with nD-Stencil pattern placed alongside other jobs running on a large system in a non-contiguous manner. Due to this placement, the nD-Stencil pattern manifests itself as a uniform spread pattern.

## 2.3 Task mapping and job placement

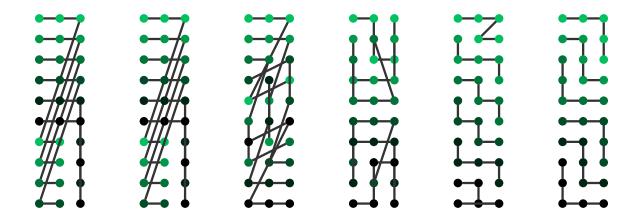

In parallel computing, several techniques have been developed to map communication graphs to hypercubes in the 1980s [25–27] and to torus networks in the early 2000s [28,29]. More recently, several application and runtime system developers have studied techniques for mapping [30–33] to three-dimensional torus topologies with the emergence of supercomputers like the IBM Blue Gene and Cray XT/XE series. Bhatele et al. [34] explored use of information about application's communication patterns, such as structured grid and unstructured mesh, and network's topology (e.g. 3D torus) to create automated tools for generating better mappings. In [34], several methods such as affine mapping, corner to center mapping, step embedding, etc. are described. Most of these schemes are designed to minimize hop-bytes: the total number of hops all the messages will take during the application execution. Fig-

Figure 2.5: Mapping of a  $6 \times 5$  grid to a  $10 \times 3$  mesh using different mapping strategies. (source [34])

ure 2.5 demonstrates how these different methods map a 2D-grid of size  $6 \times 5$  to a 2D-mesh of size  $10 \times 3$ , in order to obtain better performance.

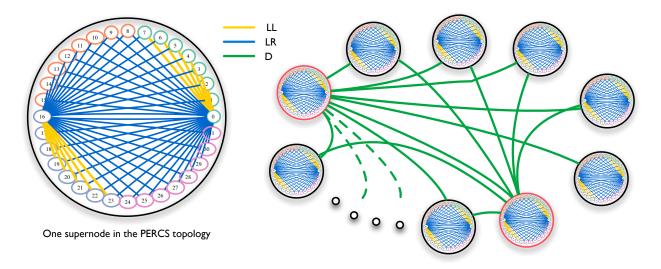

Hoefler et al. [35] discuss generic mapping algorithms to minimize contention and demonstrate their applicability to torus, PERCS, and fat-tree networks through mapping simulations of sparse matrix-vector multiplication on up to 1,792 nodes. The algorithms compared in [35] includes a greedy heuristic, recursive bisection, and mapping based on graph similarity. In addition to reducing hop-bytes, these schemes also try to minimize the maximum load on any link in the network.

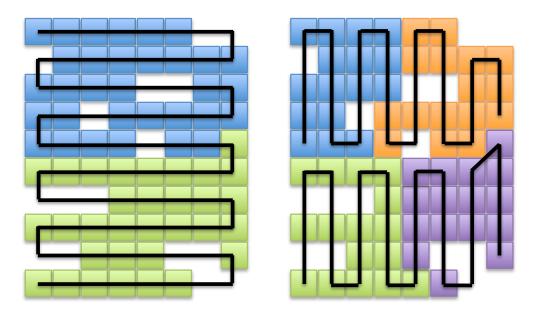

Fiedler et al. [36] have proposed methods for mapping applications with 2D, 3D, and 4D Cartesian topologies onto Cray systems with 3D torus networks and service nodes. This scheme considers the scenario where nearby nodes are allocated to jobs, preferably as prisms. Phillips et al. [37] have proposed space filling curved based mapping approaches for a even more generic case - mapping of unstructured communication patterns onto an arbitrary allocation. The key idea in the scheme proposed in [37] is to create an ordering of nodes using a topology aware space filling curve, and then deploy recursive bisection method on both network and application topologies. Figure 2.6 shows two stages of recursive bisection onto an ordered list of processes as proposed in [37].

Practical use of task mapping of an HPC application requires generation of an *assignment* of process task IDs or *ranks* to the cores and nodes in the network. Traditionally, programmers have written custom scripts to generate such assignments from scratch. This process is tedious and error-prone, especially with many tasks and high-dimensional networks. Bhatele et al. developed *Rubik* [38], a tool that abstracts several common mapping operations into

Figure 2.6: Two stages of recursive bisection topology-adapted partition mapping. The dark lines represent the sorted node traversal order for bisection. Grid element color represents recursive bisection domains after each stage.

a concise syntax. Rubik allows complex mappings to be generated using only a few lines of Python code. It supports a wide range of permutation operations for optimizing latency or bandwidth. The full range of transformations possible with Rubik is covered in [38]. Bhatele et al. also developed Chizu, a mapping tool based on graph partitioning. Chizu lets user choose different graph algorithms for recursively partitioning the application and network graphs. Once the partitioning is complete using the selected algorithms, Chizu maps them in a one-to-one manner, and generates the corresponding mapping file.

### 2.4 Indicators of performance

Let us assume a guest graph,  $G = (V_g, E_g)$  (communication graph between tasks) and a host graph,  $H = (V_h, E_h)$  (network topology of the parallel machine). M defines a mapping of the guest graph on the host graph (G on H). Several metrics have been proposed in the literature to evaluate communication performance offline by finding the suitability of the mapping M. To the best of our knowledge, the earliest metric that was used to compare the effectiveness of task mappings is dilation [39, 40]. Dilation for a mapping M can be defined as,

dilation(M) =

$$\max_{e_i \in E_g} d_i(M)$$

(2.1)

where  $d_i$  is the dilation of the edge  $e_i$  for a mapping M. Dilation of an edge  $e_i$  is the number of hops between the end-points of the edge when mapped to the host graph. This metric aims at minimizing the length of the longest wire in a circuit [39]. We refer to this as maximum dilation to avoid any confusion. We can also calculate the average dilation per edge for a mapping as,

average dilation-per-edge(M) =

$$\frac{\sum_{e_i \in E_g} d_i(M)}{|E_g|}$$

(2.2)

Hoefler et al. overload dilation to describe the "expected" dilation for an edge and "average" dilation for a mapping [35]. Their definition of expected dilation for an edge can be reduced to equation 2.1 above by assuming that messages are only routed on shortest paths, which is true for the IBM Blue Gene and Cray XT/XE family (if all nodes are in a healthy state). The average dilation metric, as coined by Hoefler and Snir, is a weighted dilation and has been previously referred to as the *hop-bytes* metric by Sadayappan [25] in 1988 and Agarwal in 2006 [30]. Hop-bytes is the weighted sum of the edge dilations where the weights are the message sizes. Hop-bytes can be calculated by the equation,

hop-bytes(M) =

$$\sum_{e_i \in E_g} d_i(M) \times w_i$$

(2.3)

where  $d_i$  is the dilation of edge  $e_i$  and  $w_i$  is the weight (message size in bytes) of edge  $e_i$ .

Hop-bytes gives an indication of the overall communication traffic being injected on to the network. We can derive two metrics based on hop-bytes: the average number of hops traveled by each byte on the network,

average hops-per-byte(M) =

$$\frac{\sum_{e_i \in E_g} d_i(M) \times w_i}{\sum_{e_i \in E_g} w_i}$$

(2.4)

and the average number of bytes that pass through a hardware link,

average bytes-per-link(M) =

$$\frac{\sum_{e_i \in E_g} d_i(M) \times w_i}{|E_h|}$$

(2.5)

The former gives an indication of how far each byte has to travel on average. The latter gives an indication of the average load or congestion on a hardware link on the network. They are derived metrics (from hop-bytes) and all three are practically equivalent when used for prediction.

Another metric that indicates congestion on network links is the maximum number of

bytes that pass through any link on the network,

maximum bytes(M) =

$$\max_{l_i \in E_h} (\sum_{e_j \in E_g | e_j \Longrightarrow l_i} w_j)$$

(2.6)

where  $e_j \implies l_i$  represents that edge  $e_j$  in the guest graph goes through edge (link)  $l_i$  in the host graph (network). Hoefler and Snir use a second metric in their paper [35], worst case congestion, which is the same as equation 2.6 above.

## 2.5 Offline performance prediction

Formal models such as LogP [41] and LogGP [42] have been used to analyze the communication in parallel applications for a long time. Subsequently, based on the LogP model, models such as LoPC [43], LoGPC [44], LoGPG [45], LogGPO [46], and LoOgGP [47] were developed to account for network congestion. Simulators based on these models, e.g. LogGOPSim [48], simulate application traces and predict communication performance.

Discrete event simulation has also been extensively deployed to predict communication performance and study communication. BigSim is one of the earliest simulators that supports packet-level simulations [49]. Structural Simulation Toolkit(SST) [50] provides online (skeleton application based) and offline (DUMPI [51] trace based) modes for simulation. Booksim [52] and IBM's Mambo [53] are sequential cycle accurate simulator that supports several topologies, but are extremely slow for simulating networks of size 10K and higher. There are several other network simulators that are either sequential and/or do not provide detailed packet-level (or flit-level) network simulation. These include the Extreme-scale Simulator(xSim) [54], DIMEMAS [55], PSINS [56], MPI-Netsim [57], OMNet++ [58], and SimGrid [59].

## 2.6 Communication algorithms

Application-level task-aware mapping has been shown to reduce the communication time for point-to-point communication operations (Section 2.3). However, typically, a good mapping has much less impact on collective operations. This is because in collective operations, the interaction among a large set of processes requires carefully designed algorithms for obtaining good performance. As a result, optimizing collectives via algorithmic design has been an important topic of interest in high performance computing [60]. Most of the existing algorithms can be grouped into two classes. The first class comprises of generic algorithms such as the binomial algorithm and recursive doubling/halving [61], which work well for many network topologies and a wide range of message sizes. Due to their simplicity and broad applicability, these algorithms are part of many MPI implementations including MPICH [62] and IBM's MPI. The second class of algorithms are specifically tailored for a given network topology. These algorithms outperform the generic algorithms for the specific target topologies and message sizes. For example, Van de Geijn et al. [63] proposed an algorithm for large message broadcast that has been shown to outperform the binomial algorithm [61]. Jain et al. [64] demonstrate that the bucket algorithm [65] can be generalized optimally, both for communication and computation, for an n-dimensional torus.

Optimization schemes for 3D torus networks have been presented in [66] and [64]. Faraj et al. [66] show how to carefully overlay six spanning trees over a 3-dimensional torus without contention. The algorithms in [66] can also be extended to rectangular sub-communicators. In general, when multiple spanning trees are directed towards or away from the root, performance improves for *Broadcast, Scatter, Gather and Reduce* because of increased link throughput utilization by multiple trees. Derived collectives, such as *Allreduce* that is performed by pipelining *Reduce* with *Broadcast*, benefit from two edge-disjoint trees, one in each direction towards and away from the root.

Unlike the collective operations discussed above, an all-to-all operation is extremely difficult to optimize. However, it is a critical operation since it is needed for widely used parallel algorithms such as 2D/3D-FFT. Hence, research has focused on improving its performance for specific cases. Kumar et al. [67] have explored Blue Gene system specific heuristics to improve the performance of all-to-all communication. FFTW [68] provides a generic implementation for 1D-decomposition based parallel nD-FFT, which relies on efficient implementation of MPI's all-to-all collective for performance. Various efforts have been made to improve the performance of 2D/3D-FFT on specific topologies. For Blue Gene systems, IBM provides a customized implementation of 3D-FFT, which takes advantage of the machine topology [69]. Anthony et al. [70] also did an in depth analysis of parallel 3D-FFT on Blue Gene style mesh topologies. They show that remapping processes on nodes and rotating the mesh by considering the communication properties of specific applications, such as P3DFFT, can reduce the communication time significantly. Special hardware based solutions for achieving fast 3D-FFT have also been explored [71].

# CHAPTER 3

## Job Placement and Task Mapping

Job placement and task mapping are techniques to optimize communication of parallel applications on the interconnection network without having to modify the source code [34]. These techniques place tasks or processes on compute nodes based on a careful consideration of the interconnection topology between the nodes and the communication behavior of the application. As discussed in Section 2.3, several researchers have studied and exploited job placement and task mapping for improving the performance of their applications.

Topology aware placement of tasks is especially important on torus networks because their large diameters can require messages to travel multiple hops to reach their destination, thereby increasing the burden on the shared links. A torus or mesh network topology has been commonly used to connect compute nodes since the Cray T3D machine was developed twenty years ago. Six of the ten fastest supercomputers in 2014 used a torus network for message passing between compute nodes. At the same time, understanding the tradeoffs of various job placement policies and task mapping algorithms for new networks such as the dragonfly is a must to make the best use of the system. The dragonfly networks also support many routing policies, whose impact on system performance is unknown.

In this chapter, our focus is on exploring answers to the open questions related to torus and dragonfly networks. This research agenda has been decided based on the state-of-the-art of the mapping research, and by anticipating the issues that may be important in coming years.