## POWER AND ENERGY MANAGEMENT OF MODERN ARCHITECTURES IN ADAPTIVE HPC RUNTIME SYSTEMS

#### BY

#### EHSAN TOTONI

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2014

Urbana, Illinois

#### Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor Josep Torrellas Professor María Jesús Garzarán Doctor Fabrizio Petrini, IBM TJ Watson Research Center

### Abstract

Power and energy efficiency are important challenges for the High Performance Computing (HPC) community. Excessive power consumption is a main limitation for further scaling of HPC systems, and researchers believe that current technology trends will not provide Exascale performance within a reasonable power budget in near future. Hardware innovations such as the proposed Exascale architectures and Near Threshold Computing are expected to improve power efficiency significantly, but more innovations are required in this domain to make Exascale possible.

To help shrink the power efficiency gap, we argue that adaptive runtime systems can be exploited. The runtime system (RTS) can save significant power, since it is aware of both the hardware properties and the application behavior. We use application-centric analysis of different architectures to design automatic adaptive RTS techniques that save significant power in different system components, only with minor hardware support.

In a nutshell, we analyze different modern architectures and common applications and illustrate that some system components such as caches and network links consume extensive power disproportionately for common HPC applications. We demonstrate how a large fraction of power consumed in caches and networks can be saved using our approach automatically. In these cases, the hardware support the RTS needs is the ability to turn off ways of set-associative caches and network links. We also present some required RTS techniques, such as recognizing the running application's pattern using pattern recognition to predict its future and adapt the hardware appropriately. Furthermore, we address two types of prevalent heterogeneity: utilization of accelerator devices and process variation. To study accelerators, we analyze and optimize an example application on a heterogeneous architecture and demonstrate techniques for efficient mapping on different devices (CPU and GPU). To address process variation challenges, we develop accurate models that let the RTS schedule efficiently in the presence speed and power consumption variation. Using the models,

we develop a novel scheduling framework that uses integer linear programming to enforce different performance and power consumption constraints.

### Acknowledgments

Ph.D. is a long and difficult journey, which one cannot possibly finish successfully without extensive support of others. I would like to thank my advisor, Prof. Kale, for letting me explore different research ideas. He was patient with me and gave me invaluable insights throughout my Ph.D. program. He also provided me the support I needed to achieve my goals.

University of Illinois is a great institution with world class faculty members. I profited from the advise and support of many other faculty members as well. For each of the research topics I pursued, I was able to work with a world-renowned expert of that field. I would like to thank Prof. Torrellas, Prof. Garzaran, and Prof. Heath for helping me in various projects. Their advice and support made finishing my research projects possible. Through my interactions with these experienced researchers, I learned how to approach a research problem, how to analyze the tradeoffs and find solutions, and how to present the results. I also need to thank Dr. Fabrizio Petrini (IBM Research) for providing me feedback, motivation, and insight about the big picture.

Parallel Programming Laboratory (PPL) is filled with many amazing students and staff. Their accomplishments and brilliant research ideas were constant sources of inspiration for me. Many ideas came out of our discussions, and they also assisted me in many other ways. I would like to thank Phil and Michael for proofreading my manuscripts and helping me prepare my presentations. Thanks to Nikhil for helping me solve technical problems and Esteban for motivating me. Also, thanks to Osman and Akhil for collaborating with me in power-related projects.

My life out of the lab was very important during these years. Champaign-Urbana's community, especially Iranians, welcomed me from the very first moment I arrived. I had an amazing time these years, learned a lot of things, and made some of my best friends. All in all, my life in Champaign was an unforgettable experience!

Last but not least, the emotional support from my family and friends was very important these years. In the most difficult times, I always felt loved and supported, which helped me carry on and continue to make progress. I will always be grateful to them.

### Grants

This work was partially supported by the following sources:

- Illinois-Intel Parallelism Center (I2PC), which is supported by Intel Corporation, partially supported this research.

- This work was also partially supported by U.S. Department of Energy grant DE-SC0006706.

- This research used resources of the Argonne Leadership Computing Facility at Argonne National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02-06CH11357.

## Table of Contents

| List of | Figures  |                                                                   | xi  |

|---------|----------|-------------------------------------------------------------------|-----|

| List of | Tables   |                                                                   | xiv |

| List of | Algoritl | hms                                                               | XV  |

| CHAPT   | ΓER 1    | Introduction                                                      | 1   |

| 1.1     | Disser   | tation Overview                                                   | 4   |

| CHAPT   | ΓER 2    | Performance, Power, and Energy Evaluation of Modern Architectures | 6   |

| 2.1     | Platfo   | orms                                                              | 8   |

|         | 2.1.1    | Intel Single-chip Cloud Computer                                  | 8   |

|         | 2.1.2    | Other Platforms                                                   | 10  |

| 2.2     | Applio   | cations                                                           | 11  |

| 2.3     | Evalua   | ation Results                                                     | 13  |

|         | 2.3.1    | Intel SCC                                                         | 14  |

|         | 2.3.2    | Intel Core i7 Processor                                           | 17  |

|         | 2.3.3    | Intel Atom D525                                                   | 18  |

|         | 2.3.4    | Nvidia ION2 Platform                                              | 19  |

|         | 2.3.5    | Load Balancing                                                    | 20  |

| 2.4     | Comp     | earison of Different Architectures                                | 22  |

| 2.5     | Relate   | ed Work                                                           | 26  |

| 2.6     | Concl    | usion                                                             | 27  |

| CHAPT   | ΓER 3    | Heterogeneous On-Chip Architectures: Case Study With Object       |     |

| Dete    | ection   |                                                                   | 29  |

| 3.1     | Enviro   | onmental Setup                                                    | 32  |

|         | 3.1.1    | ViVid                                                             | 32  |

|         | 3.1.2    | Blockwise Distance                                                | 33  |

|         | 3.1.3    | Cell Histogram Kernel                                             | 33  |

|         | 3.1.4    | Pairwise Distance                                                 | 34  |

|         | 3.1.5    | Ivv Bridge Architecture                                           | 34  |

|           | 3.1.6 Evaluation methodology                      |

|-----------|---------------------------------------------------|

| 3.2       | Optimization of Kernels in OpenCL                 |

|           | 3.2.1 Filter Kernel                               |

|           | 3.2.2 Cell Histogram Kernel                       |

|           | 3.2.3 Classifier Kernel                           |

|           | 3.2.4 Performance evaluation                      |

| 3.3       | Comparison with other Programming paradigms       |

|           | 3.3.1 OpenMP with Compiler Vectorization          |

|           | 3.3.2 OpenMP with Manual Vectorization            |

|           | 3.3.3 OpenCV Library Calls                        |

|           | 3.3.4 Performance and Effort Comparison           |

|           | 3.3.5 Possible Hardware and Software Improvements |

| 3.4       | Application Performance and Energy                |

|           | 3.4.1 Mapping Strategies                          |

|           | 3.4.2 Saving Energy with DVFS                     |

|           | 3.4.3 Trading Accuracy for Energy                 |

| 3.5       | Related Work                                      |

| 3.6       | Conclusions                                       |

| CII A DOT |                                                   |

| СНАРТ     | S. S          |

| 4 1       | 4.0.1 Background and Motivation                   |

| 4.1       | HPC Systems                                       |

|           | 4.1.1 Provisioning Practices                      |

|           | 4.1.2 Applications                                |

| 4.0       | 4.1.3 Runtime Systems                             |

| 4.2       | Cache Hierarchy                                   |

|           | 4.2.1 Cache Structure                             |

|           | 4.2.2 Cache Power                                 |

|           | 4.2.3 Architectural Opportunities                 |

| 4.0       | 4.2.4 Streaming                                   |

| 4.3       | Reconfiguration in Adaptive Runtime Systems       |

|           | 4.3.1 Overview of Our Approach                    |

|           | 4.3.2 Generalization                              |

|           | 4.3.3 Practical Details                           |

| 4.4       | Evaluation of Runtime Cache Reconfiguration       |

|           | 4.4.1 Methodology                                 |

|           | 4.4.2 Results                                     |

| 4.5       | Reconfigurable Streaming                          |

| 4.6       | Related Work                                      |

| 47        | Conclusion 88                                     |

| 5.1  | Background and Motivation                                                 |

|------|---------------------------------------------------------------------------|

|      | 5.1.1 Related Work                                                        |

|      | 5.1.2 Network Power Management Support on Current Machines                |

|      | 5.1.3 Extreme-scale Networks                                              |

|      | 5.1.4 Application Communication Patterns                                  |

| 5.2  | Potentials of Basic Network Power Management                              |

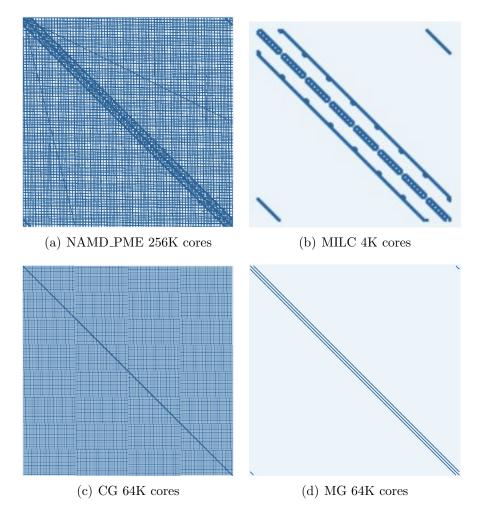

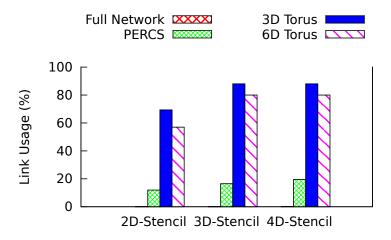

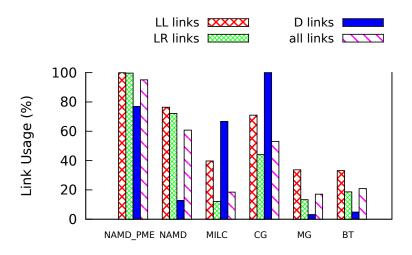

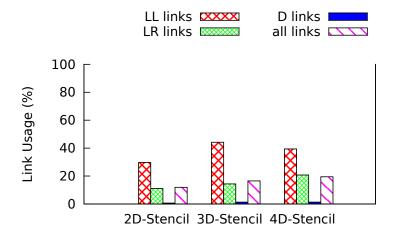

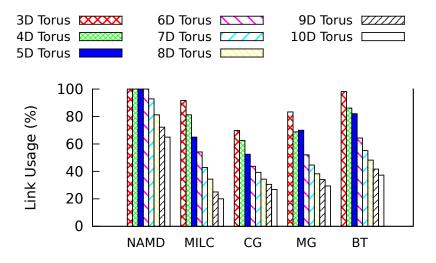

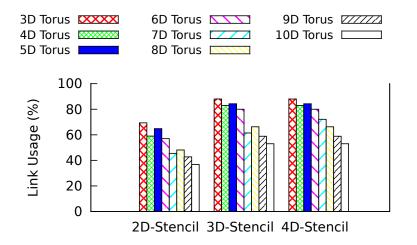

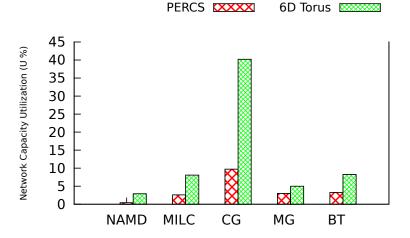

|      | 5.2.1 Link Usage of Modern HPC Networks                                   |

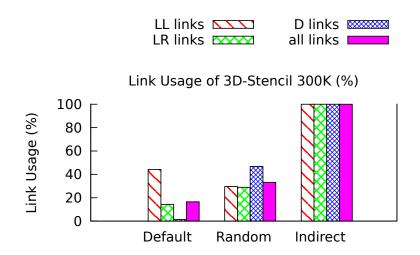

|      | 5.2.2 Different Mappings                                                  |

| 5.3  | Implementation in Runtime System and Hardware                             |

|      | 5.3.1 Runtime System Support                                              |

|      | 5.3.2 Hardware support                                                    |

| 5.4  | Power Model for Network Links                                             |

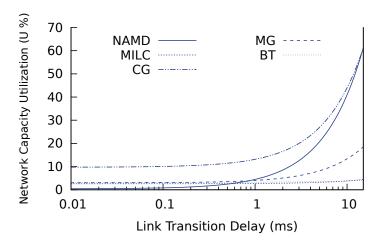

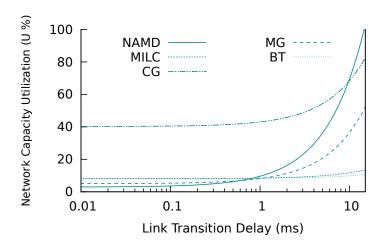

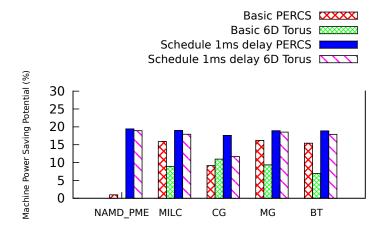

| 5.5  | Effect of on/off Transition Delay                                         |

| 5.6  | Conclusions and Future Work                                               |

| CHAP | ΓER 6 Runtime Scheduling in Presence of Process Variation Heterogeneity . |

| 6.1  | Background on Process Variation                                           |

| 6.2  | Evaluation Setup                                                          |

| 6.3  | Programming Systems                                                       |

| 0.0  | 6.3.1 Impact on Load Balance                                              |

| 6.4  | Performance and Power Modeling                                            |

| 0.1  | 6.4.1 Model 1                                                             |

|      | 6.4.2 Model 2                                                             |

|      | 6.4.3 Model 3                                                             |

|      | 6.4.4 Model 4                                                             |

|      | 6.4.5 Summary of Performance Models                                       |

|      | 6.4.6 Modeling Dynamic Power                                              |

| 6.5  | Model Driven Scheduling                                                   |

| 0.0  | 6.5.1 Efficient Configuration Space Exploration                           |

|      | 6.5.2 Incorporating DVFS                                                  |

|      | 6.5.3 Incorporating Communication Performance                             |

|      | 6.5.4 Adapting to Application Phases                                      |

| 6.6  | Evaluation                                                                |

| 6.7  | Related Work                                                              |

| 6.8  | Conclusion and Future Work                                                |

| 0.0  | Conclusion and Future Work                                                |

|      |                                                                           |

# List of Figures

| 2.1  | Architecture overview of the SCC                                                                                                            | 8  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Power breakdown of the SCC in full-power and low-power mode (from J.                                                                        |    |

|      | Howard et al. [17])                                                                                                                         | Ö  |

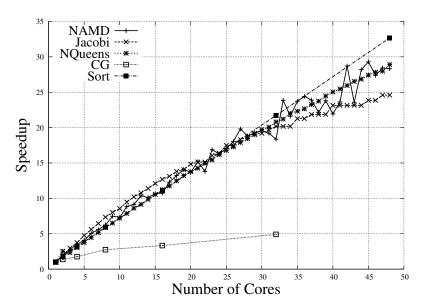

| 2.3  | Speedup of the applications on different numbers of SCC cores                                                                               | 15 |

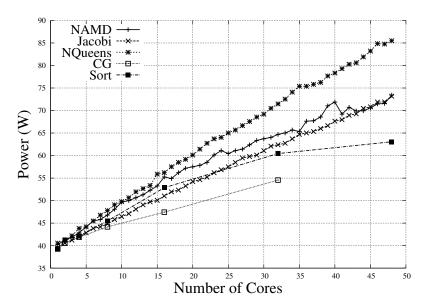

| 2.4  | Power consumption of the applications on different numbers of SCC cores                                                                     | 16 |

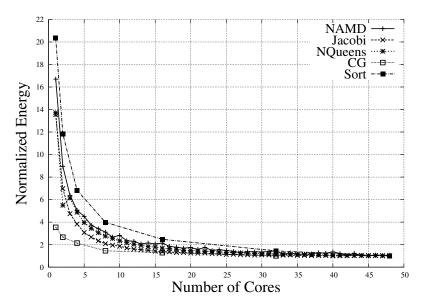

| 2.5  | Energy consumption of the applications on different numbers of SCC cores.  The data is normalized to the energy consumed with all the cores | 17 |

| 2.6  | Speedup of the applications on different numbers of threads in the Intel                                                                    |    |

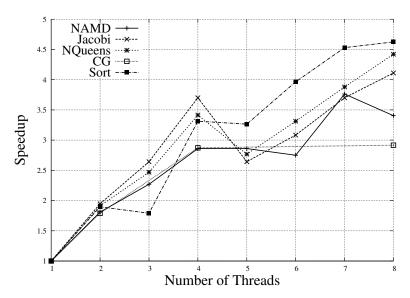

|      | Core i7                                                                                                                                     | 18 |

| 2.7  | Power consumption of the applications on different numbers of threads in                                                                    |    |

|      | the Intel Core i7                                                                                                                           | 19 |

| 2.8  | Energy consumption of the applications on different numbers of threads                                                                      |    |

|      | in the Intel Core i7. The data is normalized to the energy consumed with                                                                    |    |

|      | all the threads                                                                                                                             | 20 |

| 2.9  | Speedup of the applications on different numbers of threads in the Atom                                                                     |    |

|      | processor                                                                                                                                   | 21 |

| 2.10 | Power consumption of the applications on different numbers of threads in                                                                    |    |

|      | the Atom processor                                                                                                                          | 22 |

| 2.11 | Energy consumption of the applications on different numbers of threads                                                                      |    |

|      | in the Atom. The data is normalized to the energy consumed with all the                                                                     |    |

|      | threads                                                                                                                                     | 23 |

|      | Speed, power, and energy of the applications running on the ION2 platform.                                                                  | 24 |

| 2.13 | Utilization of the threads before and after balancing the load on the SCC                                                                   |    |

|      | and Core i7 platforms                                                                                                                       | 25 |

|      | Speed of the applications on the different platforms relative to Atom                                                                       | 26 |

|      | Power consumption of the applications on the different platforms                                                                            | 27 |

| 2.16 | Energy consumption of the applications on the different platforms normal-                                                                   |    |

|      | ized to the energy on the Atom platform                                                                                                     | 28 |

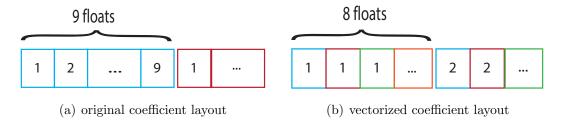

| 3.1  | change of coefficient data layout for vectorization                                                                                         | 38 |

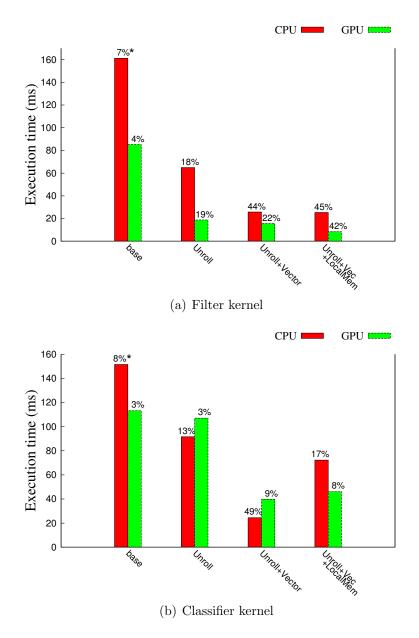

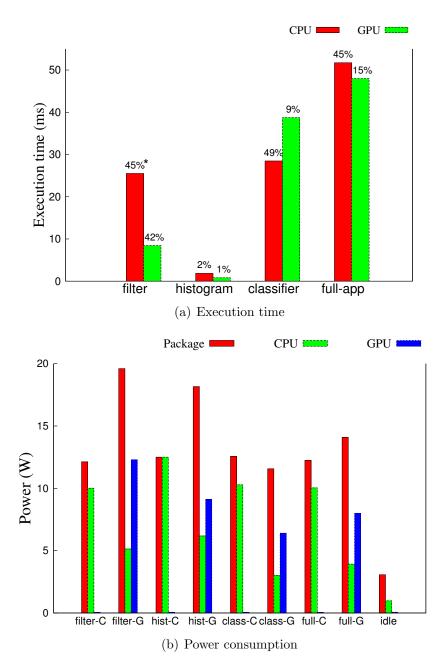

| 3.2  | Execution time of kernels with different optimizations (on Ultrabook); *-                                                                   |    |

|      | percentage of peak performance                                                                                                              | 41 |

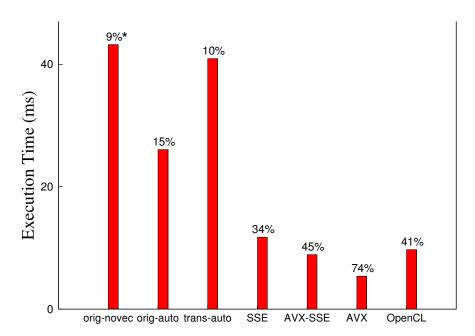

| 3.3        | Performance comparison of filter kernel in different paradigms (on Desktop); *- percentage of peak performance                             | 48           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------|

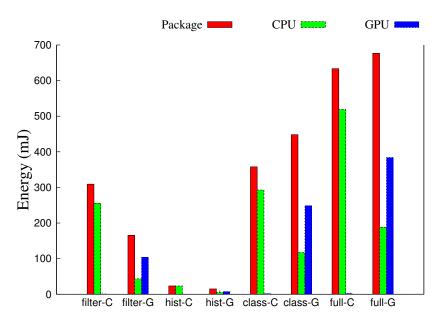

| 3.4        | Execution time and power consumption of kernels (on Ultrabook); *- percentage of peak performance                                          | 53           |

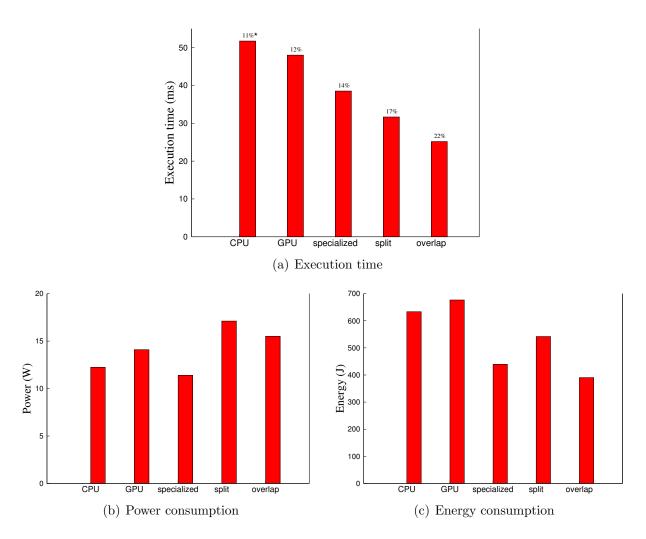

| 3.5<br>3.6 | Energy consumption (on Ultrabook)                                                                                                          | 54           |

|            | approaches; *- percentage of peak performance                                                                                              | 56           |

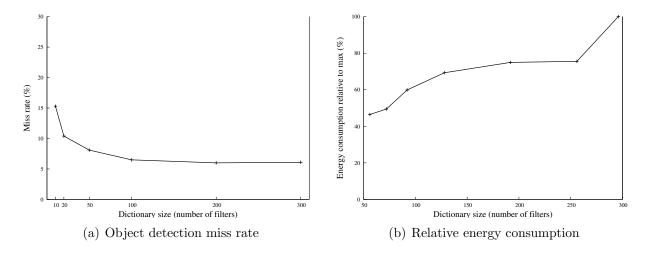

| 3.7        | Accuracy vs. energy consumption                                                                                                            | 58           |

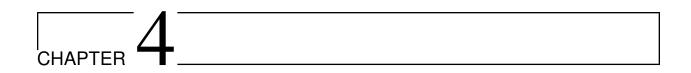

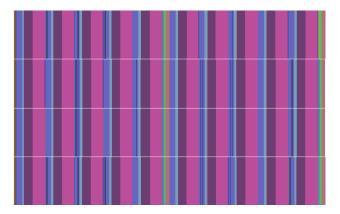

| 4.1        | 5-point 2D stencil example: boxes represent memory locations, ovals represent stencil data points, and arrows indicate data dependencies   | 67           |

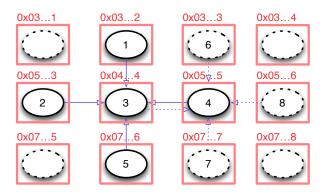

| 4.2<br>4.3 | Time between calls to Allreduce in MILC                                                                                                    | 72           |

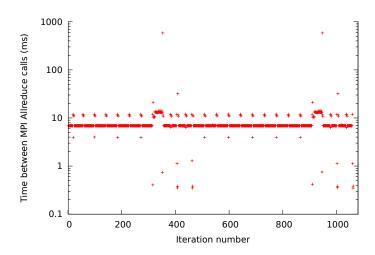

|            | illustrates the regular iterative pattern of MILC                                                                                          | 75           |

| 4.4<br>4.5 | PTA for sample <i>abc</i>                                                                                                                  | 75<br>78     |

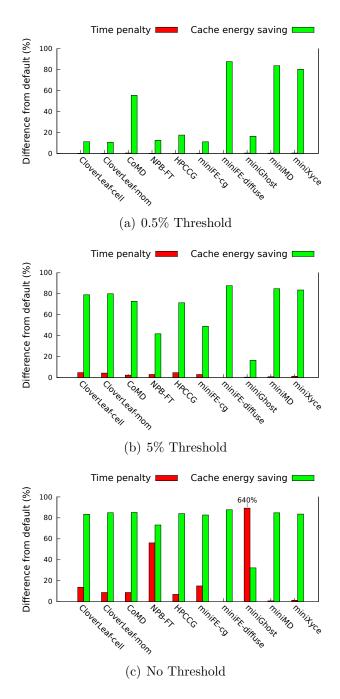

| 4.6        | Time penalty and cache energy saving of reconfiguration with different                                                                     | 10           |

|            | time penalty thresholds                                                                                                                    | 81           |

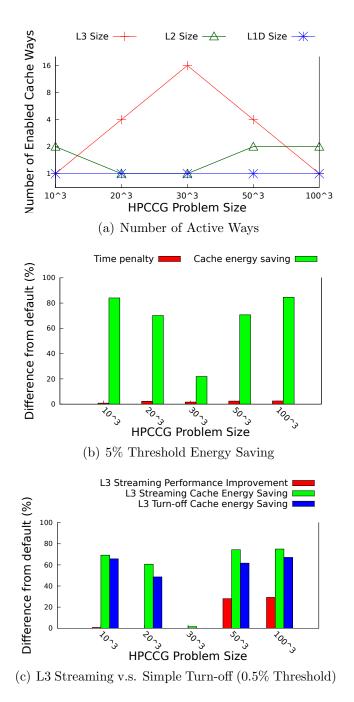

| 4.7<br>4.8 | Reconfiguration with different input sizes                                                                                                 | 83<br>85     |

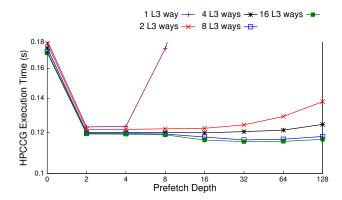

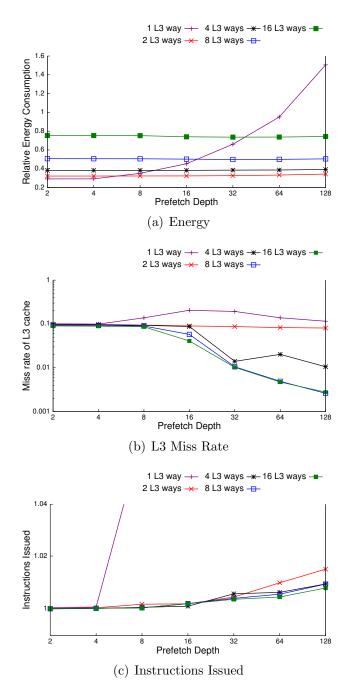

| 4.9        | Statistics of different streaming configurations for HPCCG (input size $50^3$ ).                                                           | 86           |

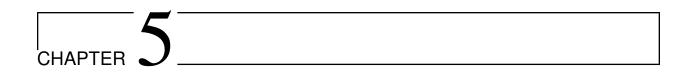

| 5.1        | IBM PERCS - a two-level directly-connected network                                                                                         | 94           |

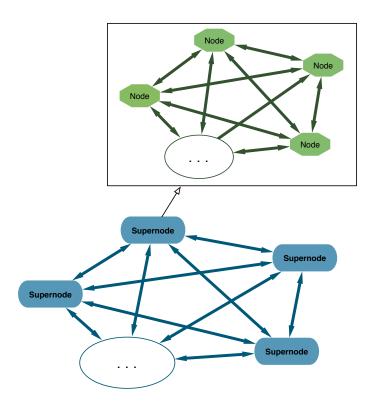

| 5.2        | Communication pattern of different applications                                                                                            | 95           |

| 5.3<br>5.4 | Fraction of links used during execution of various applications                                                                            | 98<br>98     |

| 5.5        |                                                                                                                                            | 100          |

| 5.6        |                                                                                                                                            | 100          |

| 5.7        | O                                                                                                                                          | 101          |

| 5.8<br>5.9 | $\circ$                                                                                                                                    | 101<br>103   |

|            |                                                                                                                                            | $103 \\ 108$ |

|            | 1 0                                                                                                                                        | 110          |

|            | 1 0                                                                                                                                        | 111          |

| 5.13       | Potential total machine power saving for different approaches                                                                              | 111          |

| 6.1        |                                                                                                                                            | 116          |

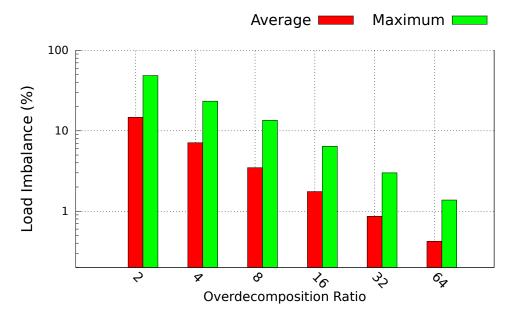

| 6.2<br>6.3 | An example of load balancing across cores with different frequencies The average and maximum load imbalance across all configurations with | 118          |

| 0.0        | · · · · · · · · · · · · · · · · · · ·                                                                                                      | 120          |

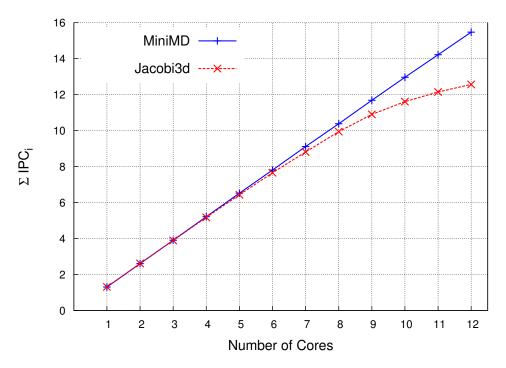

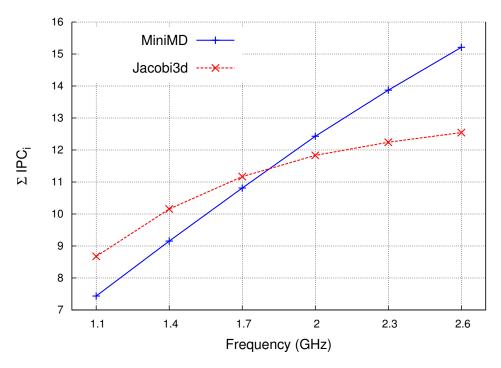

| 6.4        | <del>_</del>                                                                                                                               | 120          |

| 6.5        | Performance scaling with frequency                                                                                                         | 121          |

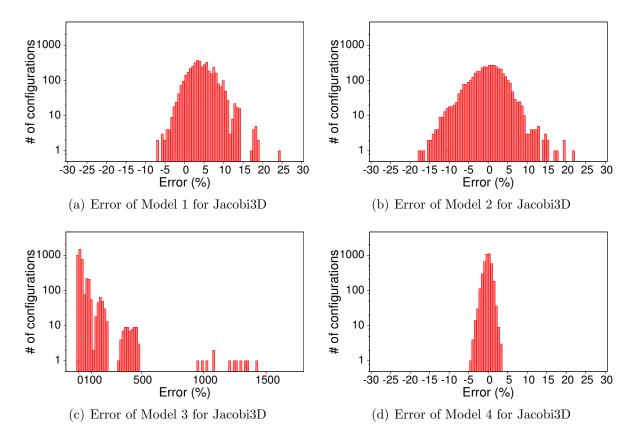

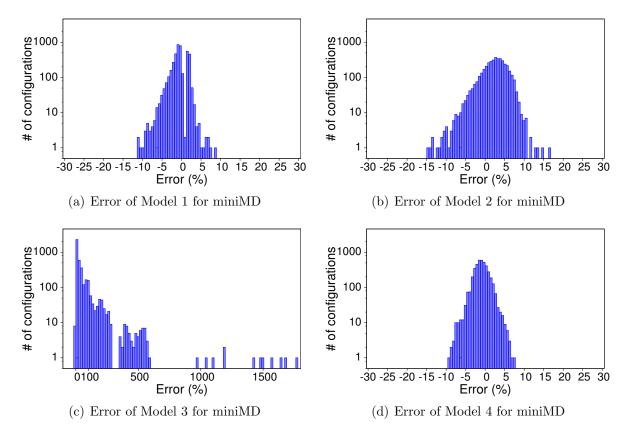

| 6.6  | Distribution of errors of different models for performance of Jacobi3D.          |     |

|------|----------------------------------------------------------------------------------|-----|

|      | The number of configurations on y-axis is shown in log scale. Model 4            |     |

|      | performs very well, with average prediction error of only 0.7% across all        |     |

|      | the configurations for Jacobi3D.                                                 | 123 |

| 6.7  | Distribution of errors of different models for performance of miniMD. The        |     |

|      | number of configurations on y-axis is shown in log scale. Model 4 per-           |     |

|      | forms very well, with average prediction error of only 1.6% across all the       |     |

|      | configurations for miniMD.                                                       | 124 |

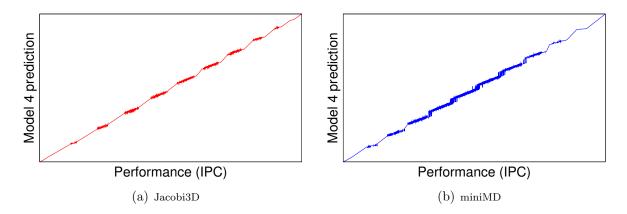

| 6.8  | Model 4 predictions as a function of actual (simulated) performance              | 127 |

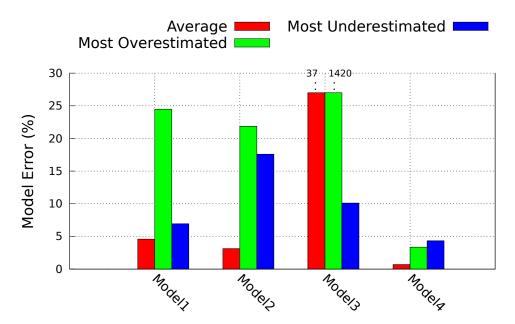

| 6.9  | Prediction accuracy of different models for Jacobi3d. Numbers on top of          |     |

|      | the Model 3 bars represent the values that are beyond the plotted range. $$ . $$ | 127 |

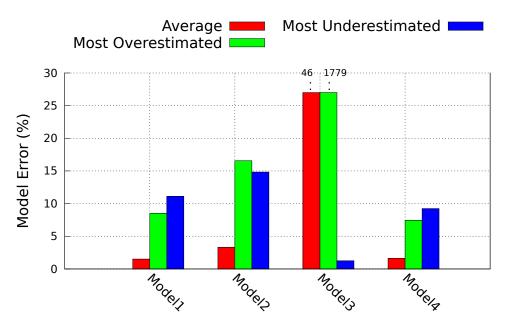

| 6.10 | Prediction accuracy of different models for MiniMD. Numbers on top of            |     |

|      | some bars represent the values that are beyond the plotted range                 | 128 |

| 6.11 | Distribution of errors of Model 4 for power consumption prediction               | 129 |

| 6.12 | Assigning communication scores to different cores on a chip                      | 133 |

| 6.13 | Comparison of our ILP-based scheduling approach to simple heuristics for         |     |

|      | miniMD                                                                           | 135 |

| 6.14 | Comparison of our ILP-based scheduling approach to simple heuristics for         |     |

|      | Jacobi3D                                                                         | 136 |

## List of Tables

| 2.1 | Intel Core i7 processor specifications                                 | 10  |

|-----|------------------------------------------------------------------------|-----|

| 2.2 | Intel Atom D525 processor specifications                               | 11  |

| 2.3 | NVIDIA ION2 graphics card specifications                               | 12  |

| 2.4 | Performance counters for the applications                              | 13  |

| 2.5 | SCC configuration used in the experiments                              | 14  |

| 3.1 | Intel Ivy Bridge (Core i5 3350 & 3317U) processor specifications       | 35  |

| 3.2 | Software environment used for experiments                              | 36  |

| 3.3 | Effective optimizations for filter and classifier kernels on Ultrabook | 42  |

| 3.4 | Software metrics for different implementations of the filter kernel    | 50  |

| 4.1 | Simulated processor's parameters                                       | 80  |

| 4.2 | Application domain sizes                                               | 80  |

| 4.3 | Best configuration found with lowest energy but without performance    |     |

|     | penalty. Format: (number of cache ways on)/(total number of ways)      | 82  |

| 6.1 | Simulated processor's parameters                                       | 117 |

| 6.2 | Example scheduling case comparing various schemes                      | 135 |

# List of Algorithms

| 1 | Filter kernel                                   | 33  |

|---|-------------------------------------------------|-----|

| 2 | Build PTA from sample                           | 75  |

| 3 | Greedy variation-aware load balancing algorithm | 119 |

CHAPTER 1

### Introduction

Power and energy issues are increasingly important for computers at different scales. The number of transistors on a chip continues to increase as predicted by Moores law, but the chip's power and energy consumption do not scale as before. Previous generations of CMOS could scale down the voltage (known as "Denard scaling" [1]) resulting in much lower power and energy consumption. However, the voltage of the transistors cannot be scaled much further easily because of the physical limitations. Therefore, the limited power budget of the processors should be used most efficiently.

Power and energy limitations have a direct impact on science and engineering applications in High-Performance Computing (HPC) environments. The HPC community is aiming to keep the total power intake of future Exascale machines (the next generation of faster computers) at tens of mega watts (MW), whereas current systems with only 10 PetaFLOPS of performance are already consuming over 10 MW of power. Multiple innovations must be developed to dramatically reduce the total power usage of supercomputers.

Realizing Exascale systems is mostly limited by power and energy consumption issues, and new design approaches are needed. Exascale systems are required to deliver 100-1000x higher performance compared to today's Petascale machines, but stay within similar power envelope. Various analyses in the literature, such as the comprehensive Exascale Computing Study [2], conclude that Exascale cannot be reached by following the current trends of energy efficiency. Hence, much more energy-efficient approaches are needed for the design of computer systems, potentially changing multiple layers, from hardware to applications.

There are various efforts to improve hardware's power efficiency towards Exascale, such as new architectures that are proposed in order to fulfill this objective [3,4]. To reduce various overheads, they include a large number of relatively simple processor cores rather than fewer complex cores. Simple cores do not have the overheads of power consuming features of

heavy cores, such as out-of-order execution and speculation. In essence, simple cores use the available power to execute useful operations, rather than spending power for scheduling instructions (e.g. out-of-order execution). However, they require more parallelism in the application to attain the same performance levels. In addition, Exascale architectures use heterogeneity to map different tasks to best matching processor type. For example, large latency-optimized cores are used for operating system and runtime, while simple cores are used for the applications calculations. Furthermore, these architectures strive to improve the energy efficiency of memory systems. For example, they do not provide full-chip cache coherence to avoid its overheads.

One major direction for power efficiency improvement is low voltage operation [5,6]. The reason is that decreasing the supply voltage  $(V_{dd})$  reduces dynamic power quadratically and also reduces static power. Researchers believe that the highest energy-efficiency can be obtained when the supply voltage is only slightly higher than the transistor's threshold voltage [7]. For current technologies, it roughly corresponds to  $V_{dd}$  of 0.5V, rather than the conventional 1V value. This regime is called Near-Threshold Computing (NTC). NTC can potentially decrease the chip's power consumption more than 40 times. However, low voltage operation slows down the processors significantly, brings more reliability challenges, and increases the effects of process variation. Therefore, circuits and devices need to be redesigned for low voltage operation.

Although these hardware innovation are expected to be significant, they are not enough to attain the power efficiency required for Exascale, based on the comprehensive Exascale report analysis [2]. Therefore, more innovations are required that are potentially software-centric. Among the software layers, the runtime system seems very promising comparatively. The runtime system is aware of both the running application and the hardware. Targeting the runtime most often avoids changing the application code, which is harder to change. It also avoids drastic changes and overheads in the hardware.

An HPC Runtime system (RTS) provides many services for the running application, and has great potential for power and energy management as well. The use of a runtime system for management of the application's communication and other parallel services is well known [8,9]. However, research has demonstrated the capabilities of runtime systems for other features such as load balancing [10], fault tolerance [11], and power management as well [12, 13]. We take advantage of an introspective software component that is aware of both the current hardware status as well as the application evolution.

In this research, we demonstrate that an adaptive runtime system can improve the power efficiency of HPC systems without significant changes in the application, and only with minor hardware support. It can do so by monitoring both the application and the hardware, and adapting to their properties. We only change the runtime layer of the system, since it is arguably the easiest to change compared to the hardware and the application layers. Our runtime studies follow a common theme. First, we exploit the capabilities of adaptive runtime systems as they are powerful tools that observe both the hardware status and the application behavior. Second, we analyze the relevant characteristics of common HPC applications and exploit them in our methods. Third, we propose small necessary hardware support, considering the properties and opportunities in modern hardware.

Avoiding drastic changes in the hardware and application is an important advantage of our approach. The approaches for power and energy efficiency can either make dramatic (revolutionary) hardware changes or incremental (evolutionary) ones. It is often argued that drastic revolutionary changes are required at this stage. However, small incremental changes had been more common so far because they are easier to sustain. Revolutionary changes for the benefit of only one domain (e.g. HPC) can potentially impair us from using commodity pieces, among other problems. For example, many large-scale supercomputers use commodity processors mainly designed for servers. Furthermore, even when the processors themselves are different, often times the same architecture design is used across various scales by just varying some parameters. For instance, Intel's Haswell microarchitecture [14] is used in processors from low power mobile devices to high-performance servers. Various instances of the architecture have different parameters such as the number of cores and the frequency range, but the underlying design is almost the same. Thus, incremental changes that allow the use of commodity hardware are highly preferred.

We argue that the same commodity processor can be used for more energy-efficient HPC machines as well, often with minor HPC-specific support. Thus, we strive to improve the power and energy efficiency of HPC machines while keeping them economically viable. Although we develop our methods mainly for HPC systems, they can be adopted for other domains as well (see Chapter 3 for an example).

Our proposals for power and energy efficiency are orthogonal with the mentioned hardware innovations and can be utilized at the same time. In some cases, our methods complement the hardware ones. For example, our variation-aware scheduling framework (see Chapter 6) addresses some of the challenges of process variation caused by low voltage operation.

Overall, we follow a cross-layer approach that focuses on the characteristics of HPC applications, capabilities of the adaptive runtime system, and the opportunities in different components (e.g. caches) of modern hardware. First, we analyze different architectural designs using multiple applications, focusing on the opportunities of heterogeneous and many-core architectures. Second, we study the opportunities and challenges (e.g. programmability) of heterogeneous architectures and propose energy efficient runtime methods to exploit on-chip

heterogeneity. Third, we strive to improve the energy efficiency of processor caches using adaptive runtime systems, since they consume a large fraction of processors power. Forth, we propose a similar adaptive runtime system based approach to improve the energy efficiency of large-scale networks. Fifth, we tackle the challenges of semiconductor process variation by intelligent runtime scheduling. These studies complement each other, and provide insight for better power and energy efficiency in different systems.

#### 1.1 Dissertation Overview

This dissertation is organized as follows. Chapter 2 evaluates and analyzes different parallel architectures, such as heterogenous and many-core architectures. We use Intel Single-Chip Cloud Computer (SCC) to analyze many-core architectures and compare them to others. The analysis criteria in this study are speed, power, energy, programmability, and application portability. The results show that many-cores represent a balanced point in terms of these metrics, since they can run existing code fast with low power. On the other hand, we show that heterogeneous architectures can be exceptionally superior for some applications, but they are difficult to program. We study them in more detail in the subsequent chapter. In addition, we study one important challenge for many-cores, namely process variation, in Chapter 6. In general, we use the insights of this chapter to tackle various power and efficiency challenges in later chapters.

In Chapter 3, we study the energy efficiency opportunities and challenges of heterogeneous architectures that were identified in the previous chapter. The opportunities include mapping different kernels of the running application to the more efficient device (CPU or GPU in this case) for that kernel. On the other hand, programmability is a main challenge, for example. To study the issues, we optimize and analyze a vision application on a heterogeneous on-chip architecture and improve its energy efficiency. This mobile application is very similar to large-scale HPC applications in various aspects, and hence, our results are extensible to other domains. We demonstrate that a unified programming paradigm such as OpenCL can increase programmer productivity since the same or similar codes can run on both devices. In addition, the results suggest that trying to get the maximum utilization of the heterogeneous platform naively is not efficient, and one has to map the kernels carefully. Since a fixed power budget is shared among devices, techniques such as software pipelining that map each kernel to the best device, while increasing utilization can be the most effective.

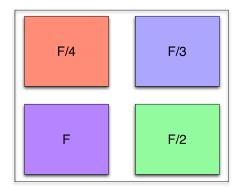

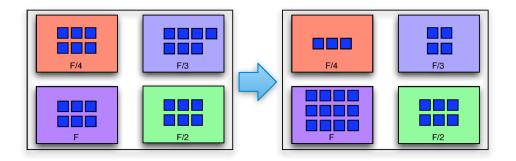

We continue by focusing on the cache hierarchy in Chapter 4, since caches consume a large fraction a processors power budget. We analyze the memory access patterns of common HPC applications and demonstrate why many of these applications cannot take advantage of all the cache capacity effectively in many cases. On the hardware side, since the caches are usually set-associative, they are already partitioned. Therefore, one can turn some of the ways of set-associative caches off to save significant power. We introduce a runtime system based method to reconfigure caches in this manner adaptively. In the context of this study, we illustrate how an HPC application's pattern can be identified and expressed using formal language theory. This helps the runtime system predict the future of the application and adapt effectively. In addition, we introduce a software-controlled streaming method that is controlled by the runtime system to adapt to the applications pattern. Overall, our approach makes the cache hierarchy more power-efficient for HPC applications.

We apply the same methodology we used for caches to improve power-efficiency of the large-scale networks in Chapter 5. Similar to caches, networks consume substantial power disproportionately, even when the running applications do not need it. We show that common HPC applications do not use a large fraction of the network links in modern high-radix topologies. In this case, the hardware property that we exploit for power efficiency is that some network links can be turned off. Therefore, we develop a runtime system based method to improve the power efficiency of large-scale HPC networks by turning links on and off adaptively. Note that we use the previous chapter's ideas to design our runtime techniques for a different component of the system, which shows the generality of our adaptive runtime system approach.

We return to many-core architectures in Chapter 6 and study their inherent heterogeneity, which is caused by process variation. This problem is different than previous ones, and therefore, it needs different runtime techniques. Because of process variation, different cores have different power and performance characteristics. The runtime needs to choose a configuration (a set of cores) that delivers the best performance while staying within the power budget. The number of configurations is exponential in the number of cores and hence, sampling all of the configurations is not possible. To solve this problem, we develop models that let the runtime system predict the performance and power consumption of different configurations of cores. Using these models, we develop a novel scheduling framework based on integer linear programming that lets the runtime enforce different performance and power constraints effectively. For example, the runtime can choose the set of cores that provide the best performance under a certain power budget. This runtime scheduling framework is also capable of enforcing other constraints, such as task mapping constraints for better communication performance.

Finally, we summarize our contributions in Chapter 7. This chapter also includes the possible future research directions based on this dissertation's insights.

# Performance, Power, and Energy Evaluation of Modern Architectures

Following Moore's law, the number of transistors that can be placed on a chip keeps increasing rapidly with each technology generation. Not surprisingly, users expect the performance to also improve over time with the increase in the number of transistors. However, performance depends on multiple factors beyond the transistor count.

The architecture community has historically tried to turn the higher transistor count into higher performance. For example, during the single-thread era, excess transistors were used for architectural features such as pipelining, branch prediction, or out-of-order execution. These features were able to improve performance while largely keeping the application unchanged.

However, in the last several years, some key technology parameters such as the supply voltage have stopped scaling. This has led to chips with unsustainably-high power, power density and energy consumption. This fact combined with the diminishing returns from single-thread architectural improvements, has pushed forward thread parallelism as the only solution to make effective use of the large number of transistors available. The result has been a paradigm shift toward parallelism.

A key architectural challenge now is how to support increasing parallelism and scale performance, while being power and energy efficient. There are multiple options on the table, namely "heavy-weight" multi-cores (such as general purpose processors), "light-weight" many-cores (such as Intel's Single-Chip Cloud Computer (SCC) [15]), low-power processors (such as embedded processors), and SIMD-like highly-parallel architectures (such as General-Purpose Graphics Processing Units (GPGPUs)).

The Intel SCC [15] is a research chip made by Intel Labs to explore future many-core

architectures. It has 48 Pentium (P54C) cores in 24 tiles of two cores each. The tiles are connected by a four by six mesh in the chip. The SCC naturally supports the message passing programming model, as it is not cache-coherent in hardware. We have ported Charm++ [16] and Adaptive MPI (AMPI) [16] to this platform to be able to run existing sophisticated applications without any change.

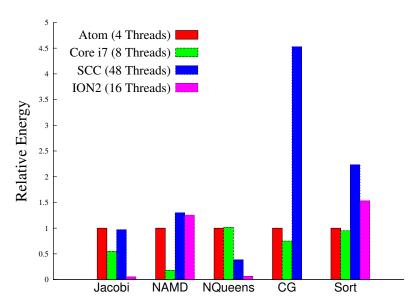

The goal of this chapter is to explore various trade-offs between the SCC and the other types of processors. We use five applications to study their power and performance: NAMD, Jacobi, NQueens, Sort and CG (conjugate gradient). These applications exhibit different characteristics in terms of both computation and communication. The processors used are the Intel SCC as a light-weight many-core, the Intel Core i7 as a heavy-weight multi-core, the Intel Atom as a low-power processor, and the Nvidia ION2 as a GPGPU. These processors represent different cutting-edge architectures. To compare these architectures, the applications are executed with the same input parameters and we measure speed, power, and energy consumption.

Our results show that each of the designs is effective in some metric or condition and there is no single best solution. For example, the GPGPU provides a significant advantage in terms of power, speed and energy in many cases, but its architecture is not general enough to fit all the applications efficiently. In addition, the GPGPU requires significant programming effort to achieve this efficiency (as we had to use different codes to run on the GPGPU) and cannot run legacy codes.

The Intel SCC results suggest that light-weight many-cores are an opportunity for the future. The SCC has lower power than the heavy-weight multi-core and runs faster than the low-power design. Also, the light-weight many-core is general enough to run legacy code and is easy to program (in contrast to the GPGPU). However, some weaknesses of the platform should be addressed in future designs to make it competitive with sophisticated multi-cores. One such weakness that we identified is slow floating-point performance.

This chapter also proves that the low-power processor does not necessarily result in less energy consumption. As shown by our data on the Intel Atom platform, the extra delay has a greater effect than the power savings achieved.

The rest of this chapter is organized as follows. Section 2.1 describes the architecture of the platforms that we study. Section 2.2 briefly introduces the applications, as their characteristics are very important to understand their scaling and power consumption on different platforms. Section 2.3 evaluates the platforms using the applications. We compare the architectures in Section 2.4 using the results of the previous section and analyze the tradeoffs of each one. We discuss the related work in Section 2.5 and conclude in Section 2.6.

#### 2.1 Platforms

Here we describe the platforms that we evaluate, with a focus on their design concept and level of parallelism. Among these platforms, the SCC is a research chip while the others are examples of commodity platforms, which are being widely used in different machines.

#### 2.1.1 Intel Single-chip Cloud Computer

The "Single-Chip Cloud Computer" (SCC) is Intel's new research many-core architecture. It has 48 Pentium cores connected through a mesh interconnect. It has been created by Intel Labs to facilitate software research on future many-core platforms. This chip is not cache coherent and it naturally supports the message passing parallel programming paradigm.

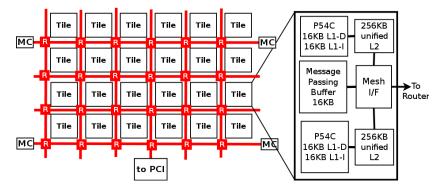

Figure 2.1 shows the architecture overview of the SCC [15]. The cores are arranged in groups of two in 24 tiles. The tiles are connected in a four by six mesh configuration. The cores are simple second-generation off-the-shelf Pentium cores (P54C). Each core has 16KB L1 data and 16KB L1 instruction caches as well as a 256KB unified L2 cache. Each tile has a 16KB SRAM called Message Passing Buffer (MPB), which is used for communication inside the chip. These MPBs form a shared address space used for data exchange. The cores and MPB of a tile are connected to a router by Mesh Interface (I/F) unit. The SCC also has four DDR3 memory controllers in the four corners of the mesh network to connect cores to memory.

Figure 2.1: Architecture overview of the SCC.

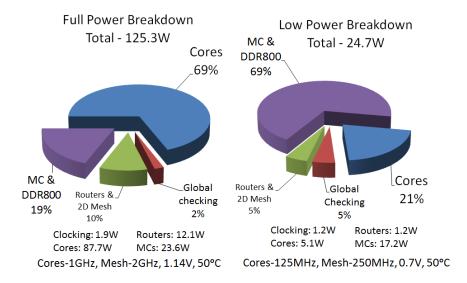

The SCC is implemented in 45nm CMOS technology and has 1.3 billion transistors. The area of each tile is 18 mm<sup>2</sup> with a total die area of 567 mm<sup>2</sup>. Power for the full chip ranges from 25W to 125W. It consumes 25W at 0.7V, with 125MHz cores, 250MHz mesh, and 50°C. It consumes 125W at 1.14V, with 1GHz cores, 2GHz mesh, and 50°C. Power for the on-die network is 6W for a 1.5 Tb/s bisection bandwidth and 12 W for a 2 Tb/s bisection

bandwidth. Figure 2.2 shows the power breakdown of the chip in two different modes: full power and low power [17].

Figure 2.2: Power breakdown of the SCC in full-power and low-power mode (from J. Howard et al. [17]).

The SCC was designed with power management in mind. It includes instructions that let programmers control voltage and frequency. There are 8 voltage domains on a chip: one for the memory controllers, one for the mesh, and six to control voltage for the tiles (at the granularity of 4-tile blocks). Frequency is controllable at the granularity of an individual tile, with a separate setting for the mesh, thereby providing a total of 25 distinct frequency domains. The RCCE library [18] provides easy access to these features, but it is more limited than the available hardware features [17].

As mentioned, message passing is the natural way of programming this non-cache-coherent chip. For this purpose, there is a low level message passing interface called RCCE that provides low level access to the communication features of the SCC. It was designed so that the chip can still operate without any operating system ("bare metal mode") to reduce the overheads [18]. However, Linux can also be run on the SCC, which is the most common usage, and we ran our experiments in this mode. In addition, there is another interface called Rckmb, which provides the data link layer for running network services such as TCP/IP. We used the latter to port Charm++ and run existing applications. Using other layers to port Charm++ could result in some communication performance improvement; however, it would not change our conclusions.

Porting Charm++ and the applications did not involve any conceptual difficulty as the SCC can be easily viewed as a cluster on a chip. However, there are many technical issues involved in working with it. These include dealing with old compilers, an old operating

system, and unavailability of some standard software and libraries. Unfortunately, we could not perform many of the intended experiments because of these technical issues and others took much more time than expected.

#### 2.1.2 Other Platforms

Intel Core i7 Processor The Intel Core i7 is a 64-bit x86-64 processor. We have used the Core i7 860 Nehalem processor chip, which has four CPU cores and on-chip cache memory on one 45nm die. Hyperthreading support allows it to appear to the OS as eight processing elements. The cores cycle at 2.8GHz (disregarding Turbo Mode), which is a relatively high frequency. Each of the four cores has 32KB instruction and 32KB data Level 1 caches, and 256KB of Level 2 cache. The four cores share an inclusive 8MB Level 3 cache. The specification of the Intel Core i7 is shown in Table 2.1.

Table 2.1: Intel Core i7 processor specifications

| Processor Number                   | i7-860             |

|------------------------------------|--------------------|

| # of Cores                         | 4                  |

| # of Threads                       | 8                  |

| Clock Speed                        | 2.8 GHz            |

| Cache Size                         | 8 MB               |

| Lithography                        | 45 nm              |

| Max TDP                            | 95W                |

| VID Voltage Range                  | 0.65V-1.40V        |

| Processing Die Size                | $296 \text{ mm}^2$ |

| # of Processing Transistors on Die | 774 million        |

Intel Atom D525 The Intel Atom is the ultra-low-voltage x86-64 CPU series from Intel. It is designed in 45 nm CMOS and used mainly in low power and mobile devices. Hyper-threading is also supported in this processor. However, there is no instruction reordering, speculative execution or register renaming.

Due to its modest 1.8 GHz clock speed, even the fastest Atom D525 is still much slower than any desktop processor. The main reason behind our selection of the Atom for our experiments is that, while desktop chips have a higher frequency, the Atom is hard to beat when it comes to power consumption. Atom allows manufacturers to create low-power systems. However, low power does not always translate into high efficiency, meaning that

Atom may have low performance per watt consumed. We have explored this issue in our experiments.

The specification of the Intel Atom processor that we used is shown in Table 2.2.

Table 2.2: Intel Atom D525 processor specifications

| Processor Number                   | D525               |

|------------------------------------|--------------------|

| # of Cores                         | 2                  |

| # of Threads                       | 4                  |

| Clock Speed                        | 1.80 GHz           |

| Cache Size                         | 512 KB             |

| Lithography                        | 45 nm              |

| Max TDP                            | 13W                |

| VID Voltage Range                  | 0.800V-1.175V      |

| Processing Die Size                | $87~\mathrm{mm}^2$ |

| # of Processing Transistors on Die | 176 million        |

Nvidia ION2 Platform Nvidia ION is a system/motherboard platform that includes Nvidia's GPU, DDR3 or DDR2 SDRAM, and the Intel Atom processor. The Nvidia ION2 has a dedicated graphics card for the new Atom CPUs. The ION2 is based on the GT218 chip (GeForce 305M, 310M) with dedicated memory (compared to the old ION that was a chipset graphics card). ION2 systems can use CUDA (Nvidia's General-Purpose Computing on Graphics Processing Units technology) as well as OpenCL (Open Computing Language), to exploit the parallelism offered by the CPU and the GPU together. This platform is used in low-power devices, and yet is equipped with a GPU. Hence it has the potential to offer great benefits in performance and power at the same time. We have used a 12" ION2 Pinetrail netbook platform for our experiments.

The specification of the CPU was mentioned in Table 2.2. The specification of the graphics processor is shown in Table 2.3.

#### 2.2 Applications

The characteristics of the applications are important to understand their different behavior and derive conclusions about the architectures. In this section, we describe the applications we used to examine the different parallel architectures. We choose scalable parallel applications that use Charm++ [16] or MPI message passing paradigms. For the GPU platform,

Table 2.3: NVIDIA ION2 graphics card specifications

| ION Series        | ION2    |

|-------------------|---------|

| GPU Number        | GT218   |

| # of CUDA Cores   | 16      |

| Clock Speed       | 475 MHz |

| Memory            | 256 MB  |

| Memory bus width  | 64-bit  |

| Power consumption | 12W     |

we use appropriate versions of the applications based on the OpenCL or CUDA models. The benchmarks are reasonably optimized but not highly optimized for any particular architecture. These applications represent different classes of programs with different characteristics to stress the platforms.

Iterative Jacobi The Jacobi calculation is a useful benchmark that is widely used to evaluate many platforms and programming strategies. A data set (2D array of values in our case) is divided among processors and is updated in an iterative process until a condition is met. The communication is mostly a nearest neighbor exchange of values. An OpenCL implementation was used for ION2, while a Charm++ version was used for the other platforms.

We selected Jacobi in our experiments since it is representative of stencil computations, which are widely used in scientific programs.

NAMD NAMD is a highly scalable application for Molecular Dynamics simulations [19]. It uses hybrid spatial and force decomposition to simulate large molecular systems with high performance. It is written in Charm++ to exploit its benefits such as portability, adaptivity and dynamic load balancing. It typically has a local neighbors communication pattern without bulk synchronization and benefits from communication and computation overlap. It also tries to keep its memory footprint small in order to utilize caches and achieve better memory performance. We chose this application to represent dynamic and complicated scientific applications. We used the ApoA1 system as input, which has 92,224 atoms.

**NQueens** The NQueens puzzle is the problem of placing n chess queens on an  $n \times n$  chessboard so that no two queens attack each other. The program will find the number

of unique solutions in which such valid placement of queens is possible. This problem is a classic example of the state space search problems. Since NQueens is an all-solutions problem, the entire solution tree needs to be explored. Thus, this problem also presents a great opportunity for parallelization with minimum communication.

We selected this problem since it is an integer program, as opposed to the other floatingpoint problems, and it represents state space search applications.

CG Conjugate Gradient is one of the NAS Parallel Benchmarks (NPB) [20], which are widely used to evaluate the performance of different parallel systems. CG is an iterative method and involves lots of communication and data movement. We chose it to stress the communication capabilities of our platforms. Unfortunately, we did not have a version of it available on our GPU system.

Integer Sort Parallel sorting is a widely used kernel to benchmark parallel systems because it represents commercial workloads with few computation and heavy communication. It does not have the massive floating point computations and regular communication patterns (such as nearest neighbors) of many scientific workloads. We use a straightforward implementation of Radix Sort in OpenCL and a similar Charm++ version.

Table 2.4 shows some performance counter values for the applications. They are obtained using the PAPI library running on the Core i7 system. The numbers are normalized with respect to the number of dynamic instructions executed. Since the applications are already well-known, these few numbers give enough insight to help explain the results.

Table 2.4: Performance counters for the applications

|                     | Jacobi | NAMD   | NQueens | CG     | Sort   |

|---------------------|--------|--------|---------|--------|--------|

| L1 Data Misses      | 0.0053 | 0.0053 | 0.0003  | 0.0698 | 0.0066 |

| Cond. Branches      | 0.0205 | 0.0899 | 0.1073  | 0.1208 | 0.0556 |

| Float-pt operations | 0.0430 | 0.3375 | 0.0004  | 0.2078 | 0.0001 |

#### 2.3 Evaluation Results

We now run the applications on the proposed platforms and measure the scaling behavior and the power and energy consumption. The data provides insight into the effectiveness of different architectural approaches. We focus on the ability of the applications to exploit the parallelism of the platform and how using more parallelism will affect power and energy consumption. We connected power meters to the whole systems (rather than just the processor chips) to measure the power consumption.

#### 2.3.1 Intel SCC

We have ported Charm++ to the SCC using the network layer (TCP/IP) provided by Rckmb. Thus, Charm++ programs can run on the SCC hardware without any change to the source code. This simplifies the porting of software significantly. We used the highest performance options available in the SCC software toolkit (1.3) to run the experiments and characterize the system. Table 2.5 shows the SCC configuration used in the experiments.

Table 2.5: SCC configuration used in the experiments

| Operating mode              | Linux    |

|-----------------------------|----------|

| Communication mechanism     | TCP/IP   |

| Tile frequency              | 800 MHz  |

| Mesh frequency              | 1600 MHz |

| Memory controller frequency | 1066 MHz |

| Supply Voltage              | 1.1 V    |

| Idle power                  | 39.25 W  |

Figure 2.3 shows the speedup of the five applications on different numbers of cores. It can be observed that using more cores improves performance, and that all the applications except CG are scalable on this platform. In addition, these Charm++ applications are scalable without any change to the source code. In Jacobi, the execution time per step on one core is 7.87s, and on the full machine is 0.32s. This corresponds to a 24.6 speedup on 48 cores. NQueens takes 568.36s to execute on one core and 19.66s on 48 cores. The resulting speedup is 28, which is even higher than Jacobi. In NAMD, the time per step is 34.96s on one core and 1.23s on all the cores. This also corresponds to a speedup of 28 on 48 cores. Thus, NAMD is an example of a full-fledged application that can use many-core architectures effectively.

Sort is the most scalable application, with a 32.7 speedup. This shows that the network can handle the communication effectively.

On the other hand, CG is the worst-scaling application, with a speedup of just 4.91 on 32 cores. We could not run it on more cores because this application requires the number of cores to be a power of two. The reason why CG is not scalable is the fine-grain global

Figure 2.3: Speedup of the applications on different numbers of SCC cores.

communication present in the algorithm. For example, there is a global reduction after each phase. Specifically, the performance counter data of Table 2.4 shows that CG has a high number of L1 cache misses on Core i7. Since the problem size is small and fits in the cache, the misses are caused by high communication. Thus, the SCC communication system (network and software) may not be suitable for this application. Optimizing the network for global communication such as by adding a collectives network can help significantly in this case. Also, tuning the runtime system such as by tuning the collective algorithms may help.

As indicated above, CG requires a power-of-two number of cores. This is an important consideration when designing many-cores, since some programmers may assume the number of cores to be a power of two for simplicity. A promising solution is to use virtualization, and use any number of virtual processors that the application needs on the available physical processors. This feature is available in Charm++ but we do not evaluate it here.

Finally, we ran four of the applications on every possible number of cores – from 1 to 48. The speedups are consistent in all the applications. In NAMD, there is some noise due to the application's dynamic and adaptive behavior.

Figure 2.4 shows the power consumption of the platform using different numbers of cores. These values are the maximum values seen during the run time of each individual application. For Jacobi, the power goes from 39.58W using just one core to 73.18W using all the 48 cores. NAMD's power consumption is similar to Jacobi. NQueens consumes more power, and goes up to 85.5W.

CG and Parallel Sort consume less power compared to the other applications. This is

Figure 2.4: Power consumption of the applications on different numbers of SCC cores.

mainly because these applications are communication-bound and processors often stall, waiting for the communications to be completed. CG consumes the least power because it has the most stall time.

Figure 2.5 shows the energy consumed by each application, which is the power multiplied by time of execution. The energy of each application with a given number of cores is normalized to the application's energy using all the cores. This allows us to compare the applications. The general trend shows that using more cores to run the applications results in less energy consumption on the SCC. This is because the performance improvement attained by the added cores is higher than the power increases. Note that on the left side of Figure 2.5 there is a large reduction in energy as we use more cores. This is because the idle power of the system is high compared to the power added by adding one core, while the execution time decreases notably. For example, when going from one to two cores, the execution time drops to nearly half, while the power difference is small. Therefore, the energy consumption drops to nearly half.

The highest energy drop is for Sort and the lowest is for CG. This is because Sort is scalable, and the time savings is more significant than the power added by using more cores. Conversely, the inferior scalability of CG results in a small drop in energy consumption. Again, one should keep in mind the idle power when analyzing power and energy consumption because it offsets the power increase with more cores, and the time savings become more important.

Figure 2.5: Energy consumption of the applications on different numbers of SCC cores. The data is normalized to the energy consumed with all the cores.

#### 2.3.2 Intel Core i7 Processor

We have used the Charm++ infrastructure for the Intel x86\_64 platform. In addition, we have used the same Jacobi, NAMD, NQueens, and Sort programs written in Charm++ and the same CG written in MPI as the ones we ran on the SCC. Since the Intel Core i7 is a quad core processor with hyperthreading, we can run up to 8 threads.

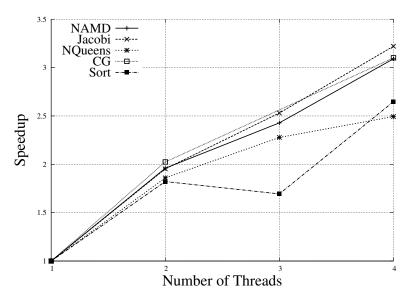

Figure 2.6 shows the speedup of these applications on different numbers of threads. By increasing the number of threads, we initially observe good speedups. Note the reduction in speedup when 5 threads are used as opposed to 4 threads. This is probably because at least two threads have to share the resources of one core. Therefore, they become slower and slow down the whole application. However, with increased parallelism, the application becomes faster and the slowdown is compensated.

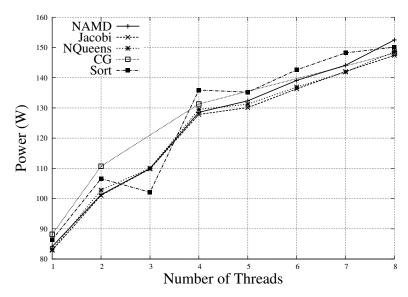

Figure 2.7 shows the power consumption of the Core i7 platform using different numbers of threads. As expected, the power used by this processor increases as the number of threads increases. However, the increase is much higher than in other platforms. The power range of the Core i7 system is from around 51W for the idle power up to 150W, which is much higher than the SCC power.

Figure 2.8 presents the energy consumed by each application, which is the power multiplied by the execution time. As in the case of the SCC, the energy is normalized to the energy consumed when running all the threads. The general trend is that with more cores, the energy consumption goes down. Again, as we saw in the case of speedup, when using 5

Figure 2.6: Speedup of the applications on different numbers of threads in the Intel Core i7.

threads, we had some increase in the runtime and, therefore, in energy consumption. Note that the reduction in energy is not as large as in the SCC case.

#### 2.3.3 Intel Atom D525

The Atom D525 is a dual core processor in which each core is 2-way hyperthreaded. All the 4 threads can execute independently. Hence we can specify up to 4 processors to Charm++. In Figure 2.9, we observe good speedups with the increase in the number of threads for several programs.

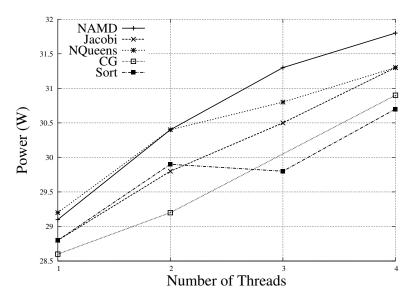

Figure 2.10 shows that the Atom system consumes much less power than the other platforms. The increase in power per thread added is less than 1 W. Since the idle power of the entire system is about 27.5 W, the power increase due to having all four threads active is about 15% of the idle power.

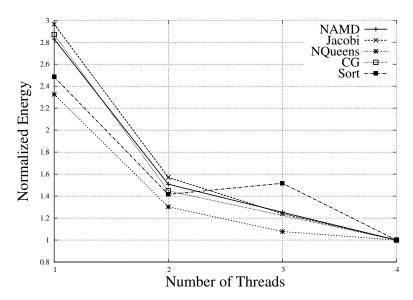

In Figure 2.11, we observe that using more threads leads to less energy consumption, like in the other platforms. The power used by the Atom increases with an increase in the number of threads. However, the increase is not as rapid as in the Core i7 because of Atom's simpler architecture. At the same time, execution time reduces considerably with more threads, and hence the energy consumption decreases.

Figure 2.7: Power consumption of the applications on different numbers of threads in the Intel Core i7.

#### 2.3.4 Nvidia ION2 Platform

We leverage the parallel computing power of the Nvidia ION2 platform using OpenCL for Jacobi, NQueens and Sort, and CUDA for NAMD. Unfortunately, we could not get a reasonably tuned version of CG. GPUs are very effective at data parallel applications due to the high number of simplistic SIMD compute units available in them. However, because the GPU is a coprocessor on a separate PCI-Express card, data must first be explicitly copied from the system memory to the memory on the GPU board. In general, applications which require a large amount of computation per data element and/or make full use of the wide memory interface are well suited to the GPU programming model.

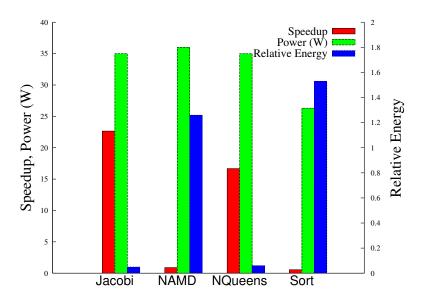

Figure 2.12 shows data on the speed, power, and energy of the applications running on the ION2 platform. We use all 16 CUDA cores in the GPU, and do not change the parallelism of the applications because there would not be a significant difference in power. The speed bars show the speedup of the applications running on the ION2 platform relative to running on the Atom platform with the maximum number of threads. We see that the speedup is 22.65 for Jacobi and 16.68 for NQueens. While these are high speedups, given the number of compute cores available in the GPU, we would have expected higher speedups. The copying of device memory buffers at the end of each iteration forms the bottleneck in this computation. Note also that NAMD is no faster on ION2 than on Atom. NAMD has had scalable results on GPGPUs and we believe that, with careful tuning, it is possible to achieve better results. However, the effort was estimated to be high. Finally, Sort is 1.76 times slower than all the

Figure 2.8: Energy consumption of the applications on different numbers of threads in the Intel Core i7. The data is normalized to the energy consumed with all the threads.

threads on the Atom. Thus, Sort is not suitable to run on GPGPUs.

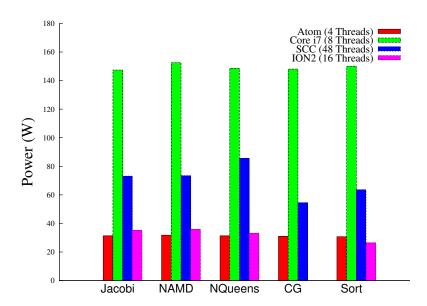

The power bars show the absolute power consumption of the ION2 platform in W using all the 16 CUDA cores. We see that the power consumption ranges from 25 W to 35 W. These numbers are much lower than those of the Core i7. Note that we have not performed our experiments on more powerful GPUs, which are expected to provide better performance, albeit at the cost of some more power consumption. In any case, we do not expect the power consumption to rise as high as a heavy-weight processor like the Core i7.

The final bars show, for each application, the energy consumed by the ION2 normalized to the energy consumed by the Atom. We normalize the energies to the Atom numbers to be able to compare the energy of the different applications — otherwise, long-running applications would dwarf short-running ones. For these bars, we use the Y axis on the right side. Overall, from the figure, we see the ION2 is more energy-efficient than the Atom for Jacobi and NQueens; the opposite is true for NAMD and Sort.

#### 2.3.5 Load Balancing

As the number of cores per chip increases, load balancing becomes more important (and challenging) for efficient use of the available processing power. Here, we investigate the effectiveness of dynamic load balancing on the SCC (with 48 threads) compared to the Core i7 (with 8 threads). We use *LBTest*, which is a benchmark in the Charm++ distribution,

Figure 2.9: Speedup of the applications on different numbers of threads in the Atom processor.

with *RefineLB* as the balancer. LBTest creates a 3D mesh graph where the nodes have objects that perform random computation. Each object also sends a message (of a size that can be specified) to one of its neighbors randomly. In our case, the size of the messages is very small compared to the computational load, so communication does not matter much. RefineLB is a simple load-balancing strategy that tries to balance the load by gradually removing objects from overloaded threads.

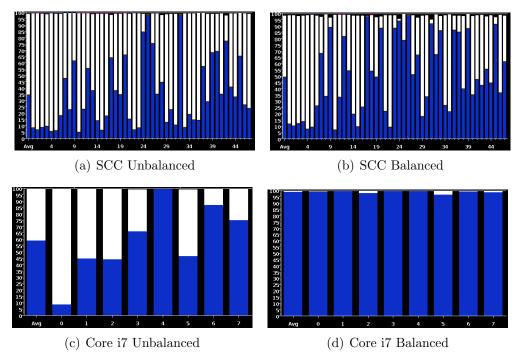

Figure 2.13 shows the utilization of each of the threads in the SCC and Core i7 platforms before and after applying the load balancer. The figure is obtained using Projections [21], which is a performance visualization tool in the Charm++ infrastructure. From the figure, we can see that the load balancer perfectly balances the load on the Core i7 platform and somewhat improves the balance on the SCC platform. On average, it increases the average thread utilization from 35% to 50% in the SCC, and from 59% to 99% in the Core i7. Load balancing is more difficult in a platform like SCC, which has many cores. The load balancer has increased the average utilization of the SCC cores significantly, but at 50% average utilization, it is clear that more effective methods are needed in the future. Overall, it can be shown that the load balancer improves the performance of the benchmark (with the same input parameters) by 30% in the SCC and by 45% on the Core i7.

Figure 2.10: Power consumption of the applications on different numbers of threads in the Atom processor.

# 2.4 Comparison of Different Architectures

In this section, we use the data of previous sections to analyze and compare the architectures. For each of the three metrics (speedup, power and energy consumption), we run the applications on all the parallel threads of each platform, to use all the resources available. On all the platforms except the ION2, we use the same source codes, written either in Charm++ (Jacobi, NAMD, NQueens, and Sort), or in MPI (CG). For the ION2, we use OpenCL for Jacobi, NQueens and Sort, and CUDA for NAMD. Unfortunately, we could not get a reasonably tuned version of CG for the ION2.

When comparing the SCC to the other platforms, one should keep in mind that the SCC is a research chip, whereas the other platforms are highly-optimized production machines. With this in mind, one main purpose of the comparison is to find the weaknesses of the SCC and propose improvements for the future.

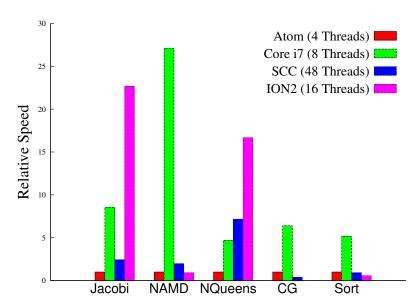

Figure 2.14 shows the speed of the five applications on the different platforms relative to Atom. As can be seen, the ION2 shows significantly better performance than the other platforms for Jacobi and NQueens, but not for NAMD or Sort. Jacobi and NQueens are simple highly-parallel applications with regular memory access and communication patterns. They match this "SIMD-like" ION2 hardware nicely. In contrast, Sort has irregular memory accesses and communication patterns, which make it unsuitable for the ION2. Finally, we could not obtain good speedups for NAMD on ION2 with our minimal porting and tuning effort, even though NAMD has been shown to scale well on GPGPUs elsewhere.

Figure 2.11: Energy consumption of the applications on different numbers of threads in the Atom. The data is normalized to the energy consumed with all the threads.

Porting applications to GPGPUs is one of the most important issues in these highly-parallel architectures. There are millions of lines of existing legacy parallel code, which cannot exploit GPGPUs easily (for example, scientific communities have a lot of parallel code mostly written in MPI). In addition, the effort for tuning and writing new code is high for GPGPUs. Generating highly-optimized codes on GPGPUs is not easy for an average programmer, and is not the subject of this work.

Overall, GPGPUs (and other architectures that are similar to SIMDs in general) are attractive for applications with simple control flow and high parallelism. However, they fail to provide good performance in other classes of applications.

In Figure 2.14, the Intel Core i7 is much faster than the other platforms for NAMD, CG and Sort. This shows that heavy-weight multi-cores are attractive solutions for dynamic applications with complex execution flow such as NAMD. The higher performance is due to high floating-point performance, support for short-length vector instructions such as SSEs, support for complex control flow (through aggressive branch prediction and speculation), and support for a high degree of instruction-level parallelism (attained by out-of-order execution).

In addition, these multi-cores are suitable for applications with irregular accesses and fine-grained communications, such as CG and Sort. These traditional platforms have highly-optimized cache hierarchies, share memory, and need less thread-level parallelism for high performance. Thus, irregular accesses are handled properly by the cache hierarchy, fine-grained communications are less costly because of shared memory, and there is less commu-

Figure 2.12: Speed, power, and energy of the applications running on the ION2 platform.

nication because of less parallelism.

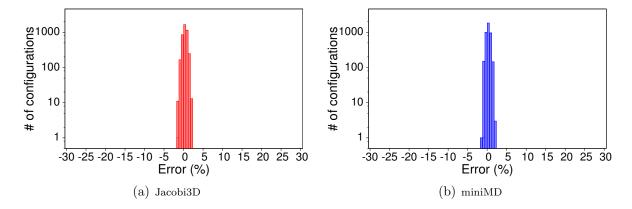

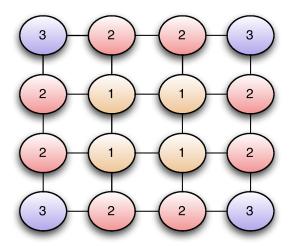

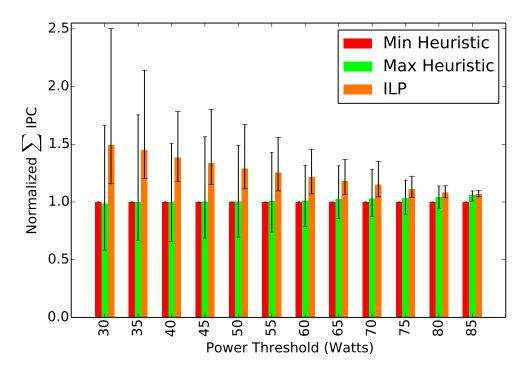

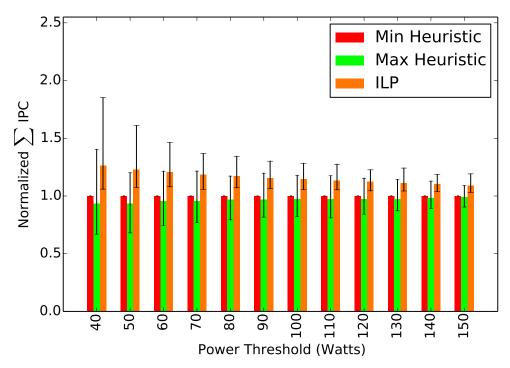

Focusing on the SCC, the figure shows that, in general, the SCC speedups are not that good. The SCC is faster than the Core i7 for NQueens, but slower for the other applications. For such applications, it is comparable to the Atom. The fine-grain communication in CG is especially hard to support well in the SCC.