© 2012 Chao Mei

### MESSAGE-DRIVEN PARALLEL LANGUAGE RUNTIME DESIGN AND OPTIMIZATIONS FOR MULTICORE-BASED MASSIVELY PARALLEL MACHINES

BY

### CHAO MEI

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2012

Urbana, Illinois

Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor David A. Padua Professor Josep Torrellas Dr. Pavan Balaji, Argonne National Laboratory

### Abstract

Multicore chips have become the standard building blocks for all current and future massively parallel machines. Much work has been done in scientific and engineering HPC applications to exploit shared-memory multicore nodes. This thesis, in contrast, pays close attention to the parallel language runtime system–a software layer that supports the execution of parallel applications. The essential idea is to parallelize the language runtime with threads as a natural consequence of the same general approach in applications to take advantage of the shared memory on a multicore node. Using the asynchronous messagedriven CHARM++ runtime system as an evaluation platform, we address the key question of how the runtime should be designed and how it can be optimized for multicore nodes on parallel machines so that applications running atop the runtime can achieve better performance with as few changes as possible.

Since the runtime performance on a single node is the basis for the overall runtime performance at scale, we have identified key factors for the runtime to run well on a single node, and developed corresponding optimization techniques. We have also developed the *CkLoop* library in the CHARM++ runtime, which showcases the necessity of a unified runtime that can make better support of the parallelism at different granularity.

Furthermore, we have explored the design space of work responsibility assignment among the threads in the multithreaded runtime. In the context of a runtime design of dedicated communication threads, we have investigated the consequent communication issues with the help from our extension to a performance analysis tool, and proposed methods that can resolve the issues. To achieve even better performance in applications, we have shown how developers can leverage new capabilities offered by the runtime, and developed new load balancing strategies that are more effective on multicore platforms.

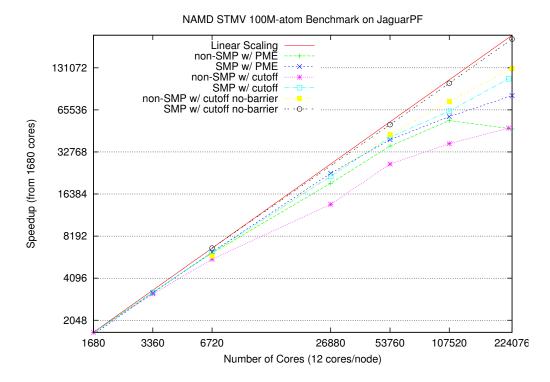

Finally, we have demonstrated the performance improvement on real production-level

scientific applications, including NAMD, a widely-used molecular dynamics simulation program, by using this multithreaded runtime on petascale massively parallel machines. In the case of the 100M-atom STMV simulation using NAMD, the multithreaded runtime leads NAMD to achieve about two-fold performance improvement on 224,076 cores of JaguarPF (Cray XT5), and about three times improvement in machine utilization on Intrepid (BlueGene/P). It also makes NAMD more scalable up to the full machine of JaguarPF and Titan (Cray XK6).

To my parents Jiwu Mei & Shizhen Tang, and to my wife Yan Zhou, for their love and support.

## Acknowledgments

I would like to thank my advisor and mentor, Professor Laxmikant V. Kalé, for his support throughout my graduate studies and for giving me wonderful opportunities to work on exciting projects. His guidance and inspiration have been invaluable not only for my education, but also for my everyday life. I would also like to extend my gratitude to the rest of my committee Prof. David Padua, Prof. Joseph Torrellas and Dr. Pavan Balaji for their insightful feedbacks and constructive help.

My sincere thanks go out to my current and former colleagues who have made the years at Parallel Programming Laboratory a truly cheerful and memorable experience. Specially, I would like to thank Dr. Gengbin Zheng for helping me on numerous implementation issues and providing his valuable experience in the graduate school as a foreign student, Dr. Sameer Kumar for the offer of an internship at IBM T.J. Watson Research which significantly helped me shape the direction of my thesis. I am very grateful, in no certain order, to Eric Bohm, Dr. Celso Mendes, Yanhua Sun, David Kunzman, Aaron Becker, Josephine Geigner, Jonathan Lifflander, Phil Miller, Pritish Jetley and Lukasz Wesolowski for their reviews of my thesis work.

It was also a great pleasure to work with people, especially Dr. Jim Phillips, from the Theoretical and Computational Biophysics Group to learn much about the molecular dynamics and the widely-used scalable simulation program–NAMD.

Finally, I would like to thank my parents for all their love and encouragement along these years when I am far away from home to pursue this doctorate. I am also much indebted to my wife Yan Zhou and my great friends, Hanlin Ouyang in particular, for their unwavering support during the ups and downs of my graduate student life.

## **Table of Contents**

| Li | st of [ | Tables                                                     | viii |

|----|---------|------------------------------------------------------------|------|

| Li | st of l | Figures                                                    | X    |

| 1  | Intr    | oduction                                                   | 1    |

|    | 1.1     | Motivation                                                 | 1    |

|    | 1.2     | Description of Problems and Scopes                         | 5    |

|    | 1.3     | Thesis Contribution                                        | 7    |

|    | 1.4     | Thesis Organization                                        | 8    |

| 2  | Bac     | kground                                                    | 9    |

|    | 2.1     | Essentials of CHARM++ Runtime System                       | 9    |

|    | 2.2     | Differences of Program Execution between MPI and CHARM++   | 12   |

|    | 2.3     | Major Scientific Applications Used in the Study            | 13   |

|    | 2.4     | Large-scale Parallel Machines Used in the Study            | 14   |

| 3  | Ben     | efits of A Multithreaded Runtime System                    | 15   |

| 4  | Inve    | estigation of Single-node Runtime Performance              | 19   |

|    | 4.1     | Study Environment Setup and Initial Performance            | 20   |

|    | 4.2     | Removing Extra Invocations of Network Progress Engine      | 22   |

|    | 4.3     | Reducing Contention in Making Runtime Multithread-Safe     | 23   |

|    |         | 4.3.1 Memory management                                    | 24   |

|    |         | 4.3.2 Granularity of critical sections                     | 26   |

|    |         | 4.3.3 Message queues                                       | 27   |

|    | 4.4     | Avoiding Cache False Sharing in the Multithreaded Runtime  | 29   |

|    | 4.5     | Setting CPU Affinity                                       | 32   |

|    | 4.6     | Decreasing the Number of Memory Accesses                   | 35   |

|    | 4.7     | Performance Studies of Applications                        | 37   |

| 5  | Exp     | loiting Fine-grained Single-node Parallelism               | 41   |

|    | 5.1     | Motivation                                                 | 41   |

|    | 5.2     | Problems with Using OpenMP                                 | 43   |

|    | 5.3     | A Unified Runtime to Exploit Single-node-level Parallelism | 47   |

|    | 5.4     | Scheduling Optimizations for the Unified Runtime           | 50   |

|    | 5.5     | Evaluation of Application Performance                      | 55   |

| 6  | Inve   | stigation of Multi-node Runtime Performance                         | 59  |

|----|--------|---------------------------------------------------------------------|-----|

|    | 6.1    | Design Exploration in Handling Communication Among Threads          | 60  |

|    |        | 6.1.1 Options in Assigning Communication to Threads                 | 60  |

|    |        | 6.1.2 Analysis of Different Options for Communication Assignment    | 62  |

|    |        | 6.1.3 Summary of SMP Mode Implementation in CHARM++                 | 70  |

|    | 6.2    | Optimizing the Usage of MPI as the Communication Substrate for the  |     |

|    |        | Message-driven Runtime                                              | 72  |

|    |        | 6.2.1 Pros and Cons of Using MPI as the Communication Substrate     | 73  |

|    |        | 6.2.2 Techniques to Overcome Disadvantages in Using MPI as the Com- |     |

|    |        | munication Substrate                                                | 77  |

|    | 6.3    | Tuning Communication Performance                                    | 81  |

|    |        | 6.3.1 The Extension of Performance Tracing Framework and Visualiza- |     |

|    |        | tion Tool                                                           | 82  |

|    |        | 6.3.2 Performance Analysis of the Communication Thread              | 85  |

|    |        | 6.3.3 Techniques to Improve Runtime Communication Performance       | 91  |

|    | 6.4    | Application-level Techniques to Leverage Multithreaded Runtime      | 95  |

|    |        | 6.4.1 Utilizing <i>NodeGroup</i> Construct to Improve Performance   | 95  |

|    |        | 6.4.2 Exploiting the Dedicated Communication Thread                 | 98  |

| 7  | Mul    | ticore-aware Dynamic Load Balancing                                 | 104 |

|    | 7.1    | Motivation                                                          |     |

|    | 7.2    | Background of Load Balancing Framework in CHARM++                   |     |

|    | 7.3    | Extension to the Existing Load Balancing Framework                  | 108 |

|    | 7.4    | Awareness of Message Latency Difference in SMP-mode                 | 110 |

|    | 7.5    | Awareness of Shared-Resource Contention Among PEs                   | 112 |

|    | 7.6    | Awareness of Asymmetric PEs Introduced by SMP Design                | 118 |

| 8  | Perf   | ormance Evaluation on Scientific Applications                       | 123 |

|    | 8.1    | Evaluation of Stencil Computation                                   | 123 |

|    | 8.2    | Evaluation of NAMD                                                  | 125 |

|    | 8.3    | Miscellaneous Evaluation                                            | 130 |

|    | 8.4    | Summary                                                             | 132 |

| 9  | Rela   | ted Work                                                            | 133 |

| 10 | Con    | clusion and Future Work                                             | 138 |

|    | feren  |                                                                     | 141 |

| ne | iei ei | ces                                                                 | 141 |

## **List of Tables**

| 2 | 2.1                                                         | Parallel Machines Used in the Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                           |

|---|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 3.1                                                         | Comparison of Average Memory Footprint in SMP and non-SMP Mode for 100M-atom Simulation in NAMD                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16                                           |

|   | 4.1<br>4.2                                                  | Memory Allocation Time on Different Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25<br>30                                     |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Performance of OpenMP in CHARM++ SMP modeInitial Overhead (us) of CkLoop LibraryOverhead (us) after Using a Simplified Node-level QueueOverhead (us) after Recycling Message Memory BufferOverhead (us) after Using Separate Micro Node-level QueueOverhead (us) after Using Separate Micro Node-level QueueOverhead (us) after Using Spanning Tree for NotificationFinal Overhead (us) of CkLoop LibraryParallel Performance of a Loop in Different SchemesParallel Performance Comparison of Two Simultaneous Loop Instances in | 45<br>51<br>52<br>52<br>53<br>54<br>54<br>55 |

| 4 | 5.10                                                        | Different Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57                                           |

|   |                                                             | ally in Jacobi2D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58                                     |

|   | 5.1<br>5.2                                                  | Comparing L1 and L2 Data Cache Misses for Separating the Computation<br>and Communication Work                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63<br>69                                     |

| ( | 5.3                                                         | Summary of Implementation Differences between the non-SMP Mode and the SMP Mode in CHARM++                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                                           |

|   | 5.4<br>5.5                                                  | Comparison among Different Broadcast Schemes with regard to Inter-node<br>and Intra-node Messages                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93                                           |

|   |                                                             | struct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98                                           |

|   | 7.1<br>7.2                                                  | The Number of L3 Data Cache Accesses and the Execution Time without<br>Any Load Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| 8 | 8.1                                                         | Parameters of Representative Molecule Benchmarks Used by NAMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123                                          |

| 8.2 | Jacobi2D Performance (ms/step) Comparison on JYC                       |

|-----|------------------------------------------------------------------------|

| 8.3 | Performance (ms/step) of NAMD on JYC                                   |

| 8.4 | Performance (ms/step) of 100M-atom STMV Simulation on JaguarPF 126     |

| 8.5 | NAMD Performance (PME Every 4 Steps) Under Different Communica-        |

|     | tion Substrate                                                         |

| 86  |                                                                        |

| 0.0 | Performance (ms/step) Comparison of Different SMP Node Size on JYC 130 |

| 8.7 |                                                                        |

## **List of Figures**

| 1.1  | Performance Results of NAMD on Abe After the Earlier Work in CHARM++ to Exploit Multicore | 4        |

|------|-------------------------------------------------------------------------------------------|----------|

| 2.1  | The Flow of a PE in non-SMP Mode                                                          | 10       |

| 4.1  | The CPU Topology of the Single-node Platform                                              | 21       |

| 4.2  | Performance Comparison between non-SMP Mode and Initial SMP Mode .                        | 22       |

| 4.3  | Performance before/after Skipping Network Calls                                           | 23       |

| 4.4  | Performance Comparison before/after Using a Better Memory Allocator                       | 24       |

| 4.5  | Performance before/after Reducing Granularity of critical sections                        | 27       |

| 4.6  | Performance Comparison with Memory Fence and Multiple Queues Re-                          |          |

|      | spectively                                                                                | 29       |

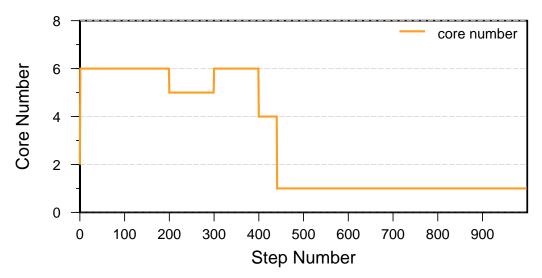

| 4.7  | Performance before/after using TLS                                                        | 31       |

| 4.8  | OS Keeps Changing the Core of a Thread.                                                   | 32       |

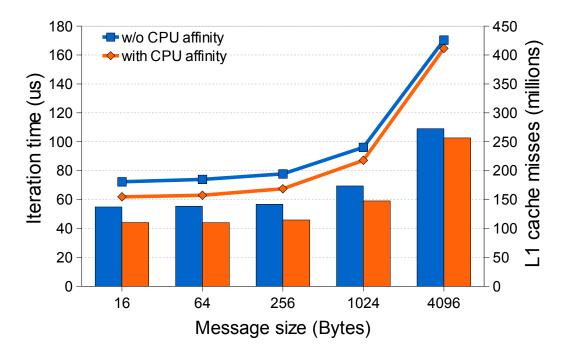

| 4.9  | kNeighbor L1 Cache Misses and Iteration Time                                              | 34       |

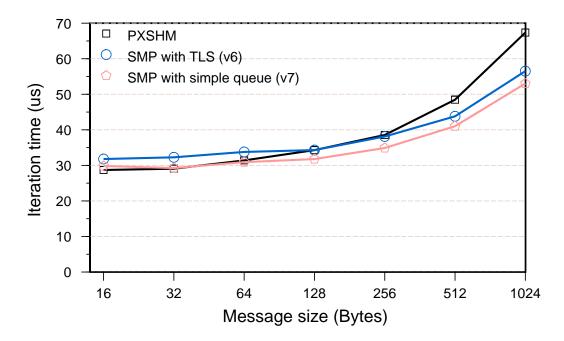

|      | Performance before/after Using the Simplified PCQueue                                     | 36       |

|      | Performance Comparison between non-SMP Mode and Final SMP Mode .                          | 37       |

|      | NAMD Performance on a Single Multicore Node                                               | 38       |

| 4.13 | ChaNGa Performance on a Single Multicore Node                                             | 39       |

| 5.1  | Snapshot of NAMD Timeline Indicating the Need of Exploiting Intra-node                    |          |

|      | Parallelism                                                                               | 42       |

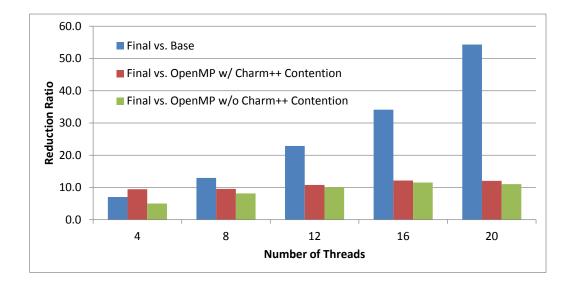

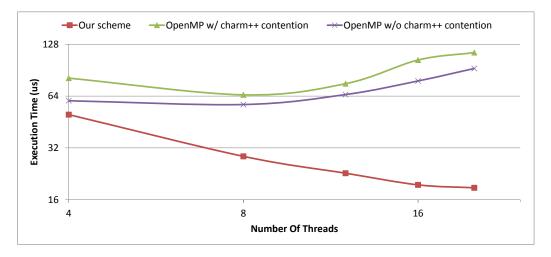

| 5.2  | Comparison of Overhead Reduction with the Final Dynamic Scheduling                        |          |

|      | Scheme                                                                                    | 55       |

| 5.3  | Scalability Comparison of the Parallelized Loop Performance in Different                  |          |

|      | Schemes                                                                                   | 56       |

| 6.1  | The Communication Pattern of the Benchmark Evaluating the Aggregated                      |          |

|      | Sending and Distributed Sending                                                           | 67       |

| 6.2  | Performance Comparison between Aggregated Sending and Distributed Send-                   |          |

|      | ing                                                                                       | 68       |

| 6.3  | The Flow of a Worker/Communication Thread in SMP Mode                                     | 72       |

| 6.4  | Performance of the Hybrid Receiving Scheme on a Multi-Pingpong Bench-                     |          |

|      | mark                                                                                      | 78       |

| 6.5  | Performance of the Hybrid Receiving Scheme on a Multi-Pingpong Bench-                     |          |

|      | mark                                                                                      | 79       |

| 66   |                                                                                           |          |

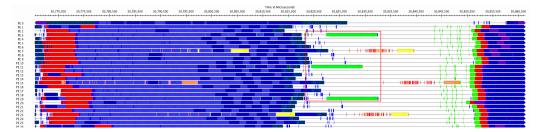

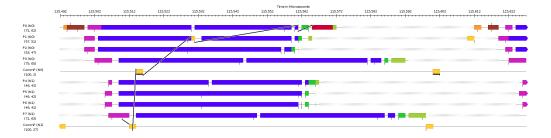

| 6.6  | A Snapshot of Timeline View of Projections                                                | 83<br>85 |

| 6.8  | Differences between Node-unaware Communication and Node-aware Com-      |

|------|-------------------------------------------------------------------------|

|      | munication                                                              |

| 6.9  | Performance Speedup of Utilizing NodeGroup Construct in NAMD 98         |

| 6.10 | The Timeline before Exploiting the Dedicated Communication Thread 102   |

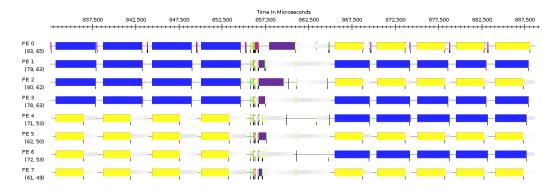

| 6.11 | The Timeline after Exploiting the Dedicated Communication Thread 103    |

| 7.1  | The CPU Topology of Intel Xeon E5520 Visualized by HWLOC 108            |

| 7.2  | The Timeline before and after Cache-contention-aware Load Balancing 118 |

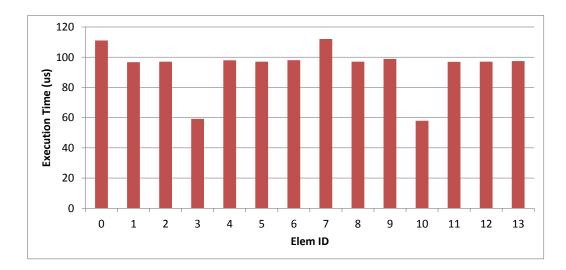

| 7.3  | The Initial Average Execution Time of Objects                           |

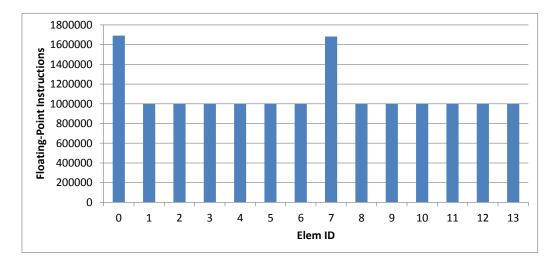

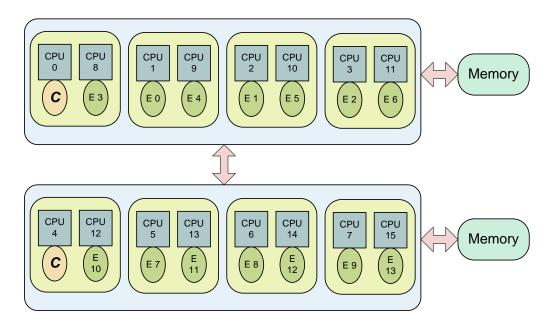

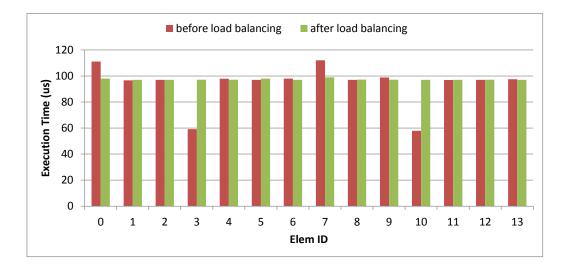

| 7.4  | The Amount of Floating-point Operations of Each Objects                 |

| 7.5  | The Mapping of Objects to Logical CPUs on a Node                        |

| 7.6  | The Average Execution Time of Objects after Asymmetric-PE-aware Load    |

|      | Balancing                                                               |

| 8.1  | The Speedup of 100M-atom STMV Simulation on JaguarPF                    |

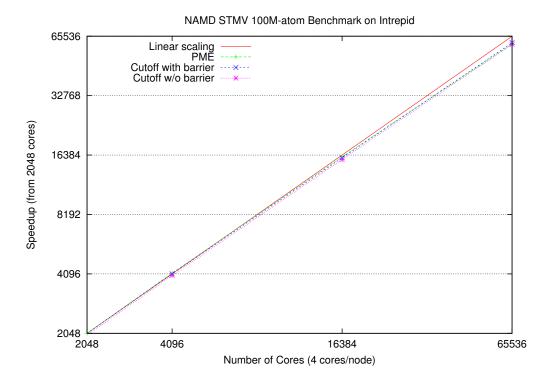

| 8.2  | The Speedup of 100M-atom STMV Simulation on Intrepid                    |

| 8.3  | The Performance (ms/step) of 100M-atom STMV Simulation (PME Every       |

|      | 4 Steps) on Titan                                                       |

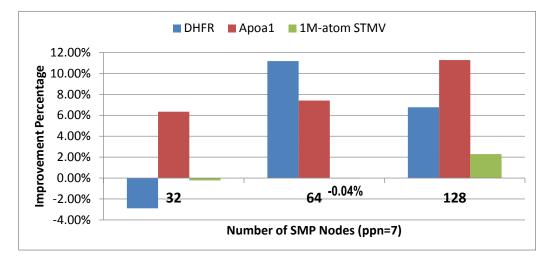

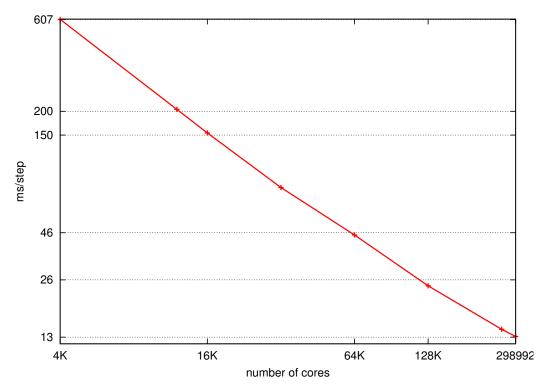

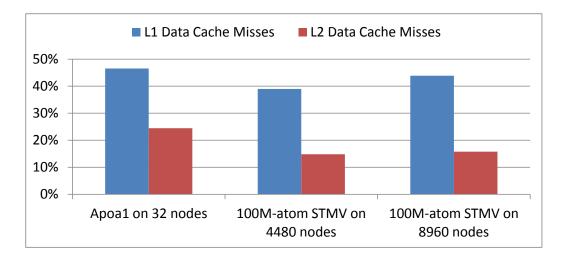

| 8.4  | The Percentage of Cache Performance Improvement                         |

## **1** Introduction

In this chapter, the motivation of this work is presented first before summarizing the issues that are investigated in this thesis. Afterwards, the contribution of this work will be listed and a brief description of the thesis organization will be given.

### **1.1 Motivation**

Since the wide adoption of multicore chips by the industry, clusters or supercomputers built on these chips of various architectures have become the most popular option for HPC systems. According to the Top500 list of June 2011<sup>1</sup>, more than 92.4% of those parallel machines have 8 cores or more per node. The percentage increases to 98.5% if we just look at the parallel machines deployed in 2010 or later. It is clear enough that near future massively parallel machines will be built from multicore nodes, and each node will consist of tens of cores. For example, BlueWaters, a heterogeneous Cray XK6 sustainable petascale supercomputer hosted in the University of Illinois at Urbana-Champaign, has 32 CPU cores per CPU-only node and 16 CPU cores per CPU-GPU-hybrid node. BlueGene/Q, the latest generation of BlueGene supercomputers, is installed with 16 cores per node but can support up to 64 logical CPUs (hardware threads) per node. These multicore-based highly parallel systems raise questions about parallel software development, especially how to write or tune parallel applications that will run efficiently on these platforms.

Many scientific and engineering applications, including the main consumers of the machine hours on these massively parallel machines, are written in MPI [1], and MPI continues to be the major programming option. Therefore, much work has been done to optimize MPI performance for multicore architectures. In particular, to reduce the message latency

<sup>&</sup>lt;sup>1</sup>http://top500.org/lists/2011/06

within a node, approaches such as posix-shared memory [2] and OS-kernel-assisted direct copy [3, 4, 5] have been explored to exploit the shared physical memory among cores within a node. As a result, both legacy applications and newly developed ones automatically enjoy performance benefits gained from multicore-based nodes. Given that each MPI task is an OS process, this type of work essentially tries to deliver efficient inter-OS-process data exchanges on a multicore node. However, it is more natural and efficient to do data exchange via threads instead of OS processes because data owned by threads are in the same memory address space. Furthermore, sharing read-only data, which is a common optimization for shared memory, is made difficult due to the disjoint memory address spaces of MPI tasks. Additionally, other characteristics of multicore chips, such as resource sharing (e.g., multiple cores sharing L2/L3 cache), are generally ignored in this kind of work, thus missing performance optimization opportunities that could be used to further utilize multicore chips.

Additionally, much effort has been spent on combining shared-memory programming options, such as OpenMP [6], Pthread [7], Thread Building Block (TBB) [8] etc., with MPI to form a hybrid programming approach. Because of the simple expressiveness of OpenMP and compiler support, MPI+OpenMP is the most popular approach [9, 10]. OpenMP is used to access the shared memory of a node to avoid intra-node communication and parallelize computation-intensive loops, while MPI is used for inter-node communication. Such a hybrid approach to take advantage of multicore-based parallel machines is also beneficial because of the large memory footprint of pure MPI programs running on parallel machines that have a relatively small amount of memory per core. For example, Hopper at NERSC is installed with 24 cores per node, but every node only has 32GB of memory. On those machines, some pure MPI programs may run out of memory if every core of the node hosts a MPI task. MPI+OpenMP allows application developers to overcome the memory issue and utilize all the cores of a node at the same time. However, although hybrid programming is popular, it delivers mixed performance results [11]: some applications always perform best with pure MPI codes, while others perform best with a certain combination of MPI tasks and OpenMP threads on a multicore node. When launching a hybrid program, spare physical cores without hosting any MPI ranks are allocated in advance for the computation parallelized using OpenMP. However, if only a part of the computation in the application can be parallelized with OpenMP, then those spare cores are going to be wasted when the other part of computation is processed. Such waste may, therefore, lead to an overall worse performance. Moreover, to achieve better performance in the hybrid approach, it may require a significant amount of programming effort and shared-memory programming experience [10]. As a result, it is better to have an approach to exploit the multicore nodes with as little increase in the programming complexity as possible.

In addition to the large amount of work done related with MPI and its applications, work on other parallel programming languages has flourished as well. They also must address the programming challenge on these massively parallel machines, as it is projected that there could be millions of cores in a machine in the near future. For example, Partitioned Global Address Space (PGAS) languages, such as Unified Parallel C (UPC) [12], are emerging alternatives that allow shared memory-like programming on those multicore-based parallel machines. Furthermore, more interests are accruing on parallel programming languages, such as ParalleX [13], CnC [14], CHARM++ [15] etc., that use a data-driven or messagedriven execution model. Such an execution model is considered to be more advantageous than the traditional message passing model represented by MPI with regard to exploiting the full computation power entailed by machines that have hundreds of thousands of cores or more [16]. For one of those languages to be accepted for a wide adoption, its runtime should first be able to run across different parallel machine platforms. More importantly, its runtime should exhibit high-performance, in which case, it is better to exploit multicore nodes. Additionally, as applications become more dynamic and complex in order to take advantage of the increasing computing capability, dynamic load balancing becomes more important. Therefore, load balancing strategies adopted by the runtime should consider the characteristics of multicore chips.

Considering all the relevant work to exploit the multicore nodes in the HPC community, this thesis studies *the design and optimization techniques from the perspective of the language runtime to exploit the multicore nodes on massively parallel machines with*  *minimal increase in programming complexity*. We take the approach to parallelize the runtime system with threads as a natural consequence of the same general approach to optimize applications for a multicore node. It is straightforward that this approach is expected to provide better communication within a node because the message can now be delivered via a message pointer in the user space without any OS kernel involvement, and provide the capability of sharing certain data structures thanks to the single memory address space on a node.

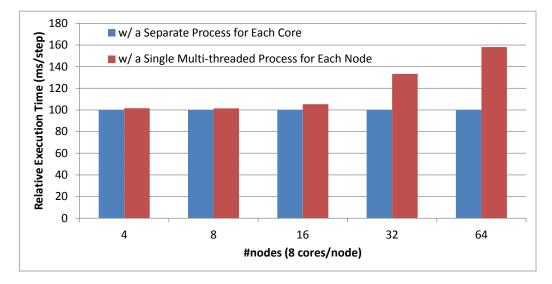

Figure 1.1: Performance Results of NAMD on Abe After the Earlier Work in CHARM++ to Exploit Multicore

Earlier versions of CHARM++ supported running in a mode that adopts the above approach as launching one process for each node and *pthread* threads for each core. However, just as in many experiments with MPI and OpenMP where the MPI everywhere performs better initially, the mode with a separate process for each core was typically faster. As one of the examples, consider the performance of NAMD [17], a widely used molecular dynamics simulation application written in CHARM++. We ran NAMD on Abe<sup>2</sup> with standard benchmark input Apoa1. In Figure 1.1, the execution time of NAMD with two versions is shown (normalized to the version with separate processes per core). Clearly, NAMD running with CHARM++ in a single-process-per-node mode performs worse and

<sup>&</sup>lt;sup>2</sup>A cluster at NCSA, which retired in early of 2011:

http://www.ncsa.illinois.edu/UserInfo/Resources/Hardware/Intel64Cluster/

becomes much worse when the number of nodes increases.

Strongly motivated by the performance problem in the earlier implementation of the multithreaded runtime approach in CHARM++, this thesis explores relevant issues in the design and optimization of a user-transparent multithreaded message-driven parallel language runtime system. Built on the ealier work in CHARM++, this research uses CHARM++ as a platform for experimentation to study the performance issues and investigate corresponding solutions. We also develop benchmarks and use real scientific applications, such as NAMD, to assess the effectiveness of this multithreaded runtime and the related optimization techniques on multiple massively parallel machines, including those in the list of top ten world's fastest supercomputers.

Exploiting multicore nodes in the runtime can capture some performance optimization opportunities that are not exposed at the programming stage, hence it is complementary to efforts by application developers. Furthermore, through performance investigation in the CHARM++ runtime on multicore-based massively parallel machines, we develop insights into how a parallel language runtime can utilize multicore nodes, which is useful to implementations of other parallel language runtime systems. Optimization techniques developed to address performance issues identified in the runtime are generally applicable to other systems or applications that are targeted at being optimized for multicore-based parallel machines.

### **1.2 Description of Problems and Scopes**

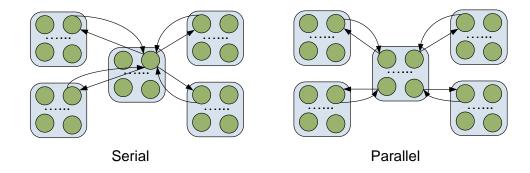

Based on possible benefits of a multithreaded runtime on parallel machines built from multicore chips, this work will explore the design space of a multithreaded runtime. In addition, this work investigates various issues and corresponding techniques to attack them both in single-node and multi-node environments. This investigation is done in the context of the asynchronous message-driven CHARM++ runtime, which is used as a platform to evaluate and implement the multithreaded runtime designs. In summary, the following issues are identified and addressed in my work: 1. What are the key factors to achieve good performance for the multithreaded runtime on a single node, and what techniques are to be used to improve its performance? We will examine common runtime data structures and identify common pitfalls in supporting them on a multicore node. In particular, we focus on the optimization for the communication within a node.

2. What is the best way to exploit fine-grained single-node parallelism in an asynchronous *multithreaded runtime?* We will study multiple mechanisms including using OpenMP, and show that it is better to exploit single-node parallelism with a mechanism we develop that reuses the existing multithreaded runtime framework. In essence, we propose a unified language runtime that can exploit parallelism at different levels of granularity.

3. What are the performance issues of a multithreaded runtime when executing on multiple nodes, and what techniques should be employed to deal with them? This issue requires investigation from several perspectives. First, we explore the design space on how the responsibilities of performing computation and communication should be assigned among runtime threads. Secondly, closely related to the first aspect, we study the communication substrate to be used in the multithreaded runtime and how it can be used better in an asynchronous message-driven runtime. We particularly focus on the case of MPI, as it is the *de facto* standard high-performance message-passing library available on every parallel machine. Finally, we investigate the general communication issues that are exhibited in a multithreaded runtime and develop techniques that are applicable to both the runtime system and applications.

4. How can we leverage the capabilities provided by a multithreaded runtime to optimize other features of a parallel programming system or performances of user-level applications? We will demonstrate this through two use case studies. One is about utilizing a language construct that exposes the multithreaded execution mode. And the other is about exploiting the dedicated communication processing power in the multithreaded runtime, especially to improve the responsiveness of the asynchronous non-blocking collective communication.

5. What factors and strategies should load balancers consider differently for multicore-

*based parallel machines?* We will study the differences between multicore chips and traditional single-core processors as well as the changes brought by a multithreaded runtime. Based on those differences, we present our insights and develop new load balancing strategies that are more effective on multicore-based parallel machines.

### **1.3** Thesis Contribution

In an era when exascale computing is expected within a decade, there is a growing consensus in the high-performance computing community that shared-memory programming should be adopted within a node while message passing should be used across nodes. This thesis examines the various issues that arise from the implementation of such a programming model. The findings and techniques described in this thesis to handle performance issues could shed light on the efforts of the community towards the realization of programming models for exascale computing. In short, this thesis makes the following contributions:

• A systematic study on a user-transparent multithreaded parallel language runtime that targets multicore chips for massively parallel machines, identifying its single-node and multi-node issues with regard to design and performance.

• Development of corresponding optimization techniques to address the various performance issues, including a better way of exploiting more fine-grained single-node parallelism and new load balancing strategies that consider the characteristics of multicore chips.

• A demonstration that a multithreaded runtime can improve the performance of real scientific applications, and it enables better scalability of a widely used molecule dynamics application up to almost all computing cores of full petascale parallel machines.

• A demonstration that application programmers can further leverage the capabilities offered by the multithreaded runtime to optimize other features of the parallel programming system.

### 1.4 Thesis Organization

In the remainder of this thesis, I will first describe the background of my work in chapter 2, which includes the introduction of the CHARM++ system, its differences from MPI as well as scientific applications and parallel machines that are used in the work. Afterwards, I will present the benefits of the multithreaded runtime in chapter 3. Then I will show studies on single-node performance issues in chapter 4, mainly focusing on problems in intra-node communication and their corresponding solutions. In chapter 5, I describe a better way of integrating more fine-grained single-node parallelism inside an asynchronous messagedriven multithreaded runtime. After investigating the issues on a single node, chapter 6 will pay attention to runtime performance issues in multi-node environment, especially focusing on analysis of inter-node communication related problems and ways to handle them. This chapter ends with user-level optimization techniques to leverage the new capabilities provided by the multithreaded runtime. I will introduce new dynamic load balancing strategies improved for multicore chips in chapter 7 before presenting the evaluation of productionlevel scientific applications running with this mulithreaded runtime in chapter 8. Finally, I will show related work in chapter 9, and finish the thesis with conclusion and future work in chapter 10.

## **2** Background

This chapter starts with an introduction of CHARM++ runtime system including its programming model and execution model as it is the software infrastructure that lays the foundation of this work. Then, the major differences between MPI and CHARM++ are described in order to better understand CHARM++. In the end, the production-level scientific applications used in performance experiments are introduced as well as a brief summary of the parallel machines used to carry out the study.

### 2.1 Essentials of CHARM++ Runtime System

CHARM++ is an object-oriented C++-based parallel programming system, featuring asynchronous message-driven execution [18]. With the encapsulation of data and work in objects, a.k.a *chares* in CHARM++, it naturally promotes the data locality that is needed to achieve good performance on multicore architectures. Additionally, it encourages overdecomposing the problem into many objects and letting the adaptive runtime map those objects to CHARM++ logical processors, called PEs (for processing elements). A CHARM++ PE is a logical control flow handling computation and communication, a counterpart of a task or rank in MPI. In CHARM++, a PE is mapped to a distinct core (or hardware thread). A CHARM++ implementation will not oversubscribe the node because the benefits of oversubscription [19] could be achieved by over-decomposing the problem instead.

Objects interacts through message passing via the invocation of an *entry method*. When an object A sends a message to another object B, the message is first delegated to object B's proxy located on the same processor with object A via the invocation of an *entry method*. Then, the computation identified by the message handler of the *entry method* is triggered by the receipt of this message on object B, and it is executed non-preemptively. The messaging mechanism in CHARM++ can use different low-level communication support, or even MPI if no specialized support is available for that underlying network hardware.

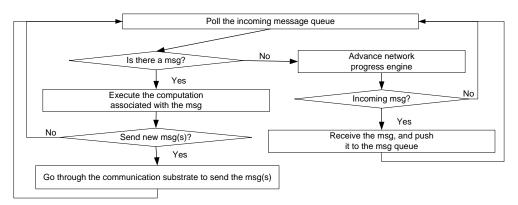

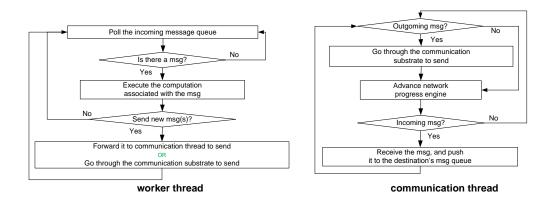

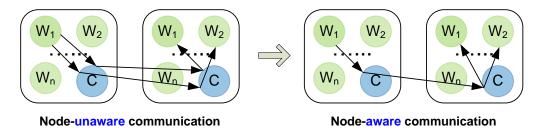

In order to check if there is any incoming message for an object on a PE, continuous message polling is used. Upon the receipt of the message, the associated *entry method* is executed in the same context. Additionally, as the runtime is executing on parallel machines connected via high-performance networks, the network progress is required to be made continuously. In essence, operations performed by a processor in the CHARM++ runtime are illustrated in the left part of Figure 2.1. Note that in the actual implementation of CHARM++ runtime, there are multiple message queues serving different purposes such as handling messages of different priorities. However, as shown in Figure 2.1, all those multiple queues are represented by one queue for simplification without sacrificing the description of essential control flow of a processor in CHARM++. Such continuous-polling type of work running on a PE discourages oversubscription as well because it creates severe resource contention and switching overheads.

Figure 2.1: The Flow of a PE in non-SMP Mode

Traditionally, the PE is encapsulated in an OS process, and we call it the "*non-SMP*" mode of CHARM++. The key implementation characteristics of this mode are summarized as follows:

• An **OS process** represents a CHARM++ PE, and is mapped to a logical CPU (a core or a hardware thread).

• **Disjoint** virtual memory address space for all PEs on a physical node.

• Alternative computation and network communication per PE.

Note that messages between PEs in the same node are handled in the same way as internode messages. Based on the description above, it is clear that the concept of multicore nodes is not reflected in this traditional CHARM++ runtime.

Well before multicore chips dominated the consumer market, shared-memory multiprocessor nodes had been used for high-end parallel machines for a long time in HPC. Thus, CHARM++ introduced the multithreaded runtime called "SMP" mode trying to take advantage of these parallel machines. In this mode, the PE is encapsulated into a thread, and all the threads that share the single memory address space consist of a CHARM++ logical SMP node. Now the CHARM++ logical node is associated with an OS process while it is the logical PE that is associated with the OS process in non-SMP mode. Within this CHARM++ logical node, data can be shared via pointers in CHARM++ programs. Although objects in CHARM++ typically do not exploit such sharing directly, CHARM++ system libraries may exploit this feature. A physical node may be partitioned into one or more CHARM++ logical nodes. In both modes, a PE is always mapped to a distinct physical core or hardware thread (i.e., two PEs are never mapped to the same physical core or hardware thread). However, the performance of "SMP" mode, prior to the work done in this thesis, was not satisfactory, as demonstrated by Figure 1.1. Furthermore, the non-SMP mode of CHARM++ was good enough to deliver excellent performance on real applications, thus diverting our limited energy to other important research issues. Given the wide adoption of multicore nodes, the SMP mode of CHARM++ started to gain attention. Therefore, this thesis is built on this basic structure of SMP mode with efforts on exploring the design space and rationalizing our implementation in addition to identifying performance issues in the runtime and investigating corresponding optimization techniques to address them.

### 2.2 Differences of Program Execution between MPI and CHARM++

In CHARM++ programs, a message to an object is sent asynchronously in the form of invoking a non-blocking entry method on that object's proxy, and the arrival of this message on that object triggers the associated work. The receiving side of this message (i.e., the object) has no idea of when this message is expected to arrive, and even may not be aware of where this message comes from, or what message is expected to be received. In other words, the receiver is blind to the message sending operations, and all the messages are "unexpected" from the perspective of the receiver. This style is a natural consequence of the message-driven programming model. The express advantage of this style creates a performance challenge, especially when it is being implemented on top of MPI. We address this challenge in section 6.2. Note that in CHARM++ programs, user-defined persistent communication operations also exist but are not commonly used. Messages then become "expected" under such circumstances.

In contrast, MPI programs use two-sided communication interfaces, in most cases, the message is involved with actions on both sending and receiving side. When a message is sent from the sending side, the receiver will correspondingly prepare for the arrival of this message at some time regardless of the sending time. Such "expected" message-passing mechanism in MPI is the main difference from the "unexpected" one in CHARM++.

Since MPI 2.0, one-sided communication interfaces have been provided to take advantage of the capabilities of RMA network hardware [1]. Such one-sided communication sounds like the communication in CHARM++ on the surface, but it is far more restricted in real usage. First, only a special memory region from a MPI rank could be used in MPI one-sided operations, and this memory region must be exposed by a collective call. Secondly, MPI one-sided operations must be synchronized either involving the sender and the receiver, or involving only the sender but requiring globally exclusive access to the special memory region. In contrast, the communication in CHARM++ is free of those restrictions. Such restrictions also prevent existing versions of MPI (1.1 or 2.0) from being the efficient compilation target for PGAS languages [20]. The MPI 3.0 may have features to alleviate these problems, but their utility in the context is not demonstrated yet.

### 2.3 Major Scientific Applications Used in the Study

In this study, the primary scientific application used intensively is **NAMD**–one of the most widely used biomolecular dynamics simulation application in the world [17]. Biomolecular simulation is a very important approach to understanding the functioning of biological systems. The atom-by-atom simulation of such systems helps us to determine the relationship between the structure of proteins and their functions, understand various biological processes, and facilitate rational drug design and nano-device construction. Generally, for this type of simulation, the individual timestep needs to be carried out in milliseconds in order to obtain interesting simulation results. Considering the variety of computations that must happen during this time and the communication dependencies between them, it is highly challenging to achieve such a short timestep. NAMD is developed in the CHARM++ parallel programming system and uses a hybrid parallelization scheme that is similar to ones described in [21, 22]. In this method, atomic coordinates and velocities are stored and propagated by static spatial domain objects called "patches" while the calculation of interactions between atoms is decomposed into independently migratable "compute objects".

The work also studies the performance of a cosmological application–**ChaNGa** [23] that is used for the simulation of the evolution of the universe. ChaNGa handles forces generated by both gravitational and hydrodynamic interaction. It already considers multicore-related optimizations at the application level, and makes extensive use of the CHARM++ language constructs that are designed for the SMP mode. With these optimizations, during the computation of the forces it leverages the shared memory and avoids all communication within a node. Communication is present during other phases of the iterative process, such as during construction of the global tree.

### 2.4 Large-scale Parallel Machines Used in the Study

In this study, we have used the following large-scale parallel machines shown in Table 2.1. The first column of the table indicates the name of the machine which will also be used in the thesis to represent the platform. The second column shows the place where the machine is hosted. The remaining columns illustrate the architecture characteristics of the machine. Note the last parallel machine JYC is a smaller system having the same configuration with the NSF-funded sustainable petascale machine–BlueWater.

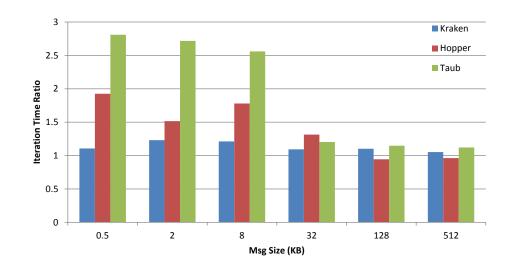

| Name     | Location | Memory<br>per node | #Cores<br>per node | Network         | Processor Type                                    |

|----------|----------|--------------------|--------------------|-----------------|---------------------------------------------------|

| JaguarPF | ORNL     | 16GB               | 12                 | Cray Seastar2+  | AMD Opteron 8435<br>2.6GHz 6-core                 |

| Kraken   | NICS     |                    |                    | Only Soustai21  | Istanbul                                          |

| Hopper   | NERSC    | 32GB               | 24                 | Cray Gemini     | AMD Opteron 6172<br>2.1GHz 12-core<br>Magny-Cours |

| Intrepid | ANL      | 2GB                | 4                  | IBM Proprietary | IBM BlueGene/P<br>0.85GHz 4-core<br>PowerPC 450   |

| Taub     | UIUC     | 24GB               | 12                 | Infiniband      | Intel Xeon X5650<br>2.66GHz 6-core<br>Nehalem     |

| Titan    | ORNL     | 32GB               | 16                 | Cray Gemini     | AMD Opteron 6274<br>2.2GHz 16-core                |

| JYC      | NCSA     |                    | 32                 | Cray Ochinii    | Interlagos                                        |

Table 2.1: Parallel Machines Used in the Study

# **3** Benefits of A Multithreaded Runtime System

This chapter describes the benefits we have identified that a multithreaded runtime will bring to programmers and applications. First, we have a short summary of the multi-threaded runtime (referred to as the "SMP" mode). The idea behind such a parallel language runtime is a natural consequence of the common practice in single-node shared-memory programming that an application is parallelized using threads to harness the computation power of a multicore chip. In the context of a language runtime, the control flow on each logical CPU is now encapsulated into a thread, such as Pthread [7], instead of an OS process. We regard that the threads spawned by the same OS process now consists of a SMP node. The single memory address space shared by those threads provides a natural way to exploit the shared physical memory on a multicore node. Speaking of MPI, this SMP mode corresponds to the scenario in which each MPI rank is mapped to a thread in runtime. It differs from the hybrid mode of MPI+pthreads or MPI+OpenMP where each MPI rank is still mapped to a process while threads spawned by the process are not considered to be MPI ranks.

Based on our experience with the multithreaded runtime, the following benefits have been identified that a multithreaded runtime could at least bring to the applications and their developers:

• Low-overhead and faster intra-node communication: because all the threads are in the same memory address space, the intra-node communication turns to simply passing the message pointer in CHARM++. Comparing this mechanism with process-based intra-node communication, this method first avoids the double memory copy as used in methods via posix-shared memory such as [2], and secondly saves overheads on switching between user mode and kernel mode in the OS as well as packing/unpacking control information in the single-copy mechanism assisted by OS kernel [3, 4].

| #Nodes         | 140    | 560    | 2240   | 4480   | 8960    | 17920   |

|----------------|--------|--------|--------|--------|---------|---------|

| #Cores         | 1680   | 6720   | 26880  | 53760  | 107520  | 215040  |

| non-SMP (MB)   | 838.09 | 698.33 | 798.14 | 987.37 | 1331.84 | 1760.86 |

| SMP (MB)       | 280.57 | 141.83 | 122.41 | 126.03 | 131.84  | 157.76  |

| Reduction Rate | 2.99   | 4.92   | 6.52   | 7.83   | 10.10   | 11.16   |

Table 3.1: Comparison of Average Memory Footprint in SMP and non-SMP Mode for 100M-atom Simulation in NAMD

• Memory footprint of programs reduced: there are two sources of saving memory in SMP mode. First, memory usage in the system-level may be reduced, especially for the communication library. Take the SMP mode built on MPI as an example, as the number of MPI processes in a program is reduced by the node size in SMP mode, the memory taken for inter-node communication channels setup, pre-allocated message buffers is reduced correspondingly. Secondly, the single memory address space shared by PEs in the same node allows a single copy of data structures that are read-only or ones that are written only during the startup of the application or during certain execution phases. The memory footprint of the program will be reduced further by being aware of this possibility of sharing data structures in SMP runtime mode. For instance, in NAMD, the molecule object that contains static physical attributes of atoms, and the map object that tracks the distribution of patch and compute objects are optimized to be shared in a node. Thanks to this memory sharing, the 100M-atom simulation could start to use more than one core per node on Intrepid where only 2GB of memory is available per node. If simulating this huge molecule system in the non-SMP mode, however, about 2GB is required per CHARM++ PE. Consequently, just one PE could be launched per node on Intrepid so as to meet the memory constraints, leaving three cores of out of four wasted without any computation. The following table 3.1 shows the actual memory footprint consumption of the 100M-atom simulation both in non-SMP mode and SMP mode on JaguarPF, illustrating the benefit of SMP mode in memory footprint reduction. Note that the table is excerpted from my published paper [24]. According to table 3.1, we first can observe that the overall memory usage of each mode will first decrease and then increase when the number of nodes used grows. This results from a mix of three factors: a) the whole input data distributed on every core is reduced with the increase in the number of cores used; b) the memory usage of some data structures, including those that are shared across cores within a SMP node, grows linearly with the number of cores used; c) the CHARM++ runtime, including the lower communication library (MPI in this testcase) also requires more memory when the simulation scales up. Furthermore, shown by the last row in the table, it is clear that there is a growing memory reduction rate with the increase of nodes used for simulation. In short, we obtained an average of  $\sim$ 7X reduction rate for memory consumption in SMP mode.

• **Reduced job startup time:** in SMP mode, only one process is created for a SMP node composed of multiple cores, which also implies that there is only one instance of the underlying communication library. In constrast, in non-SMP mode, the number of processes created is the same with the number of cores requested. As a result, the job launch time will be significantly reduced, especially for very large scale runs. It has been demonstrated by our experiment of running NAMD on JaguarPF using MPI as the communication substrate for CHARM++. In particular, for a run with 224,076 cores, it took about 1 minute to launch the job in SMP mode while it took about 6 minutes in non-SMP mode! This is because the total launched MPI ranks in SMP mode is reduced by 12 times! In SMP node, we created one MPI rank per physical node (12 cores/node) whereas each physical core hosts one MPI rank in non-SMP mode.

• **Transparency to application developers under the same programming model:** with parallelizing the language runtime into a multithreaded one, it is transparent to application developers because they will still continue to write programs under the same programming model. The same application that runs in non-SMP mode will almost run flawlessly in SMP mode, and vice versa. This is especially feasible in CHARM++, because the programmers write in terms of objects (chares) without any reference to processors and then the runtime will adaptively map those objects to processors. Therefore, the software implementation of a processor hardly affects the above user applications.

In addition, particularly for CHARM++, since the data and work have been encapsulated in the parallel object, it naturally promotes the data locality which is required to achieve good performance in multithreaded shared-memory programming. As a result, maintaining the same programming model is more favorable than the hybrid programming approach. Admittedly, to make the best of the multicore chips, an additional different programming model such as the shared-memory programming model may have to be used so as to achieve the best application performance. However, by exposing the additional programming model to developers in a very limited way through certain constructs or features of the parallel language that the multithreaded runtime is associated with, we believe that the burden on the developers to use an additional programming model for the multicore platforms can be reduced.

In spite of these significant benefits, the SMP mode of CHARM++ and the multithread MPI implementation have not been very popular. A large fraction of the applications still continue to use the non-SMP mode where each core constitutes an OS process which represents a MPI rank or a CHARM++ PE. This is in large because the performance is no better in SMP mode as shown by Figure 1.1, and sometimes it is even significantly worse as we will see in section 4.1. A major objective of this dissertation is to understand the performance loss seen in practice, and explore optimization techniques to eliminate the performance loss so that the potential benefits of SMP mode described in this chapter could be retained.

## **4** Investigation of Single-node Runtime Performance

The performance of the runtime on a single node is the basis of the overall performance of the runtime in a massively parallel machine. In this chapter, we will examine the following two issues:

• What are the key factors that affect the performance of a multithreaded runtime on a single multicore node?

• Based on the identified factors, what are the optimization techniques that can be employed to improve the performance?

We investigate these issues through studying the multithreaded CHARM++ runtime (i.e., the SMP mode). We examined common data structures used in the runtime and pitfalls of shared-memory multithreading programming. We have used "*k*Neighnor", a communication intensive synthetic benchmark written in CHARM++, to evaluate each optimization technique we developed to address a certain performance issue. At the end of this chapter, performance results on real scientific applications are presented. This part of work has been published in paper [25]. Although the corresponding optimization techniques developed for the identified performance issues in this chapter look straightforward from the current perspective, because the CHARM++ system evolved in the last two decades, those optimization techniques are not supported or developed at the time when implementing the feature that turns to be problematic in performance nowadays. From this point of view, the case study presented in this chapter also serves as a summary of optimization techniques that are available currently to improve performance for a multithreaded runtime effectively.

### 4.1 Study Environment Setup and Initial Performance

The benchmark–kNeighbor creates a certain number of objects distributed on the parallel machine, and arranged in a 1-dimensional array. In each iteration, each object sends a message to its k neighbor objects on both sides in a wraparound fashion. When each object has received all the expected messages (2 \* K), it proceeds to the next iteration. Throughout the study described in this chapter, k is set to 3 and the number of objects is set to be same with the logical CPUs of the node size (as the program is evaluated on a single SMP node) so that every PE has exactly one object. Clearly, this benchmark emphasizes on the performance of the intra-node communication. As the multithreaded runtime is expected to have smaller latency for intra-node communication, we also compare the performance of kNeighbor with that in non-SMP mode using the same configuration in order to demonstrate such benefit enabled by the multithreaded runtime. The iteration time reported is averaged over ten thousand times.

We have conducted this study on multiple multicore single-node platforms, including AIX running on IBM Power5 and Linux running on both Intel and AMD processors. Those platforms are summarized below:

- Platform A: AIX 6.1/IBM Power 5, a 16-core (SMT=2) node

- Platform B: Ubuntu 8.04/Intel Nehalem Xeon E5520, a 8-core (SMT=2) node

- Platform C: Ubuntu 8.04/Intel Harpertown Xeon E5405, a 8-core node

- Platform D: Ubuntu 8.04/AMD Barcelona Opteron 2356, a 8-core node

- Platform E: CentOS 5.4/Intel Dunnington Xeon E7450, a 24-core node

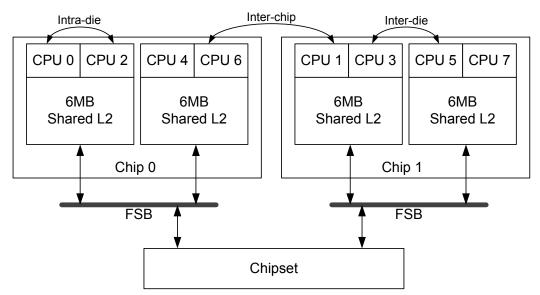

The hardware configurations of those platforms are representative of current large-scale parallel machines. Based on our study, we have found the results are similar for all the architectures, so we refer only to platform C in the following discussions unless there are some different results on other platforms. The eight cores of the representative platform C are illustrated in figure 4.1 together with their topology viewed by the OS. We categorize data transfers between cores as "intra-die", "inter-die" and "inter-chip", ordered by

increasing data transfer latency. In our experiments, we have generally left one core free to accommodate noise from OS daemons.

Figure 4.1: The CPU Topology of the Single-node Platform

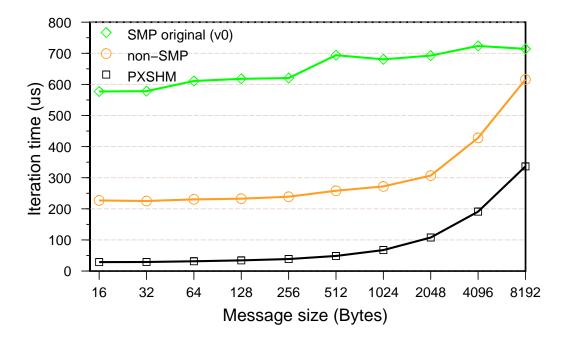

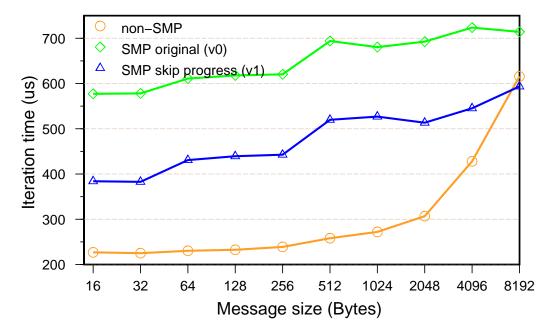

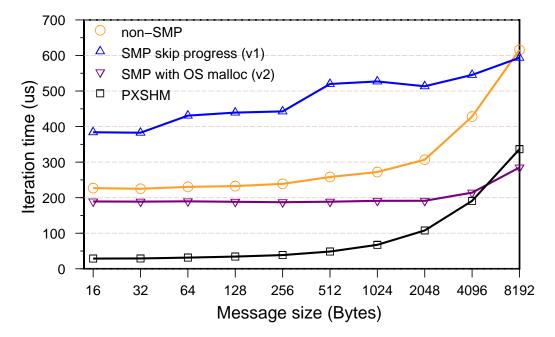

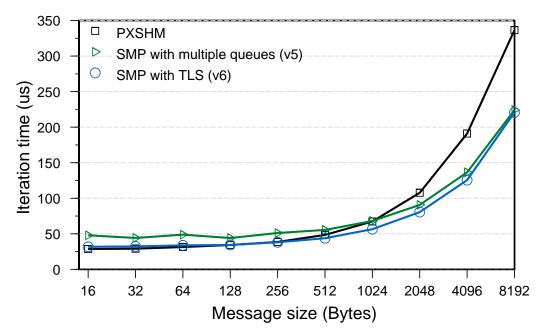

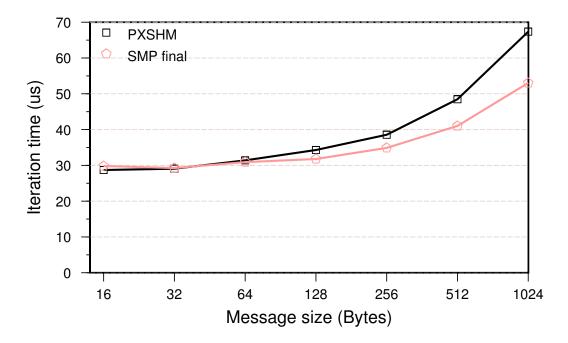

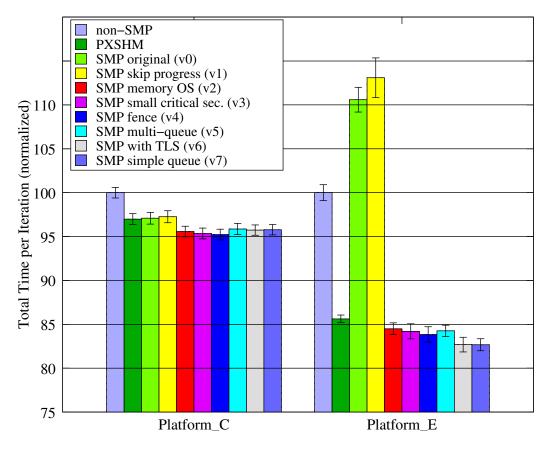

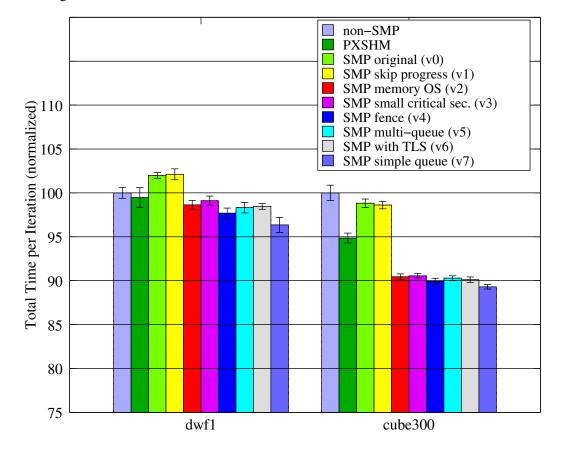

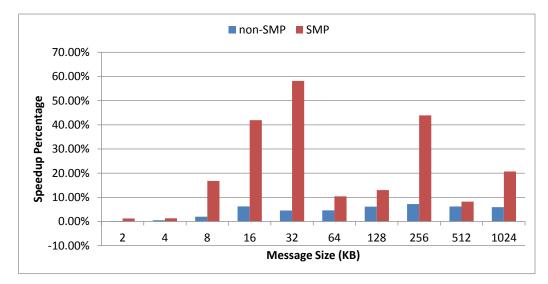

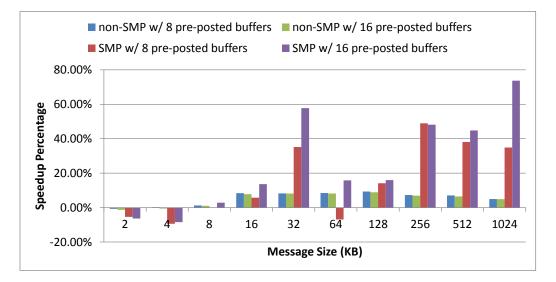

We describe each identified key performance factor followed by the corresponding optimization technique. The effectiveness of each optimization is illustrated by reporting the performance before and after on the *k*Neighbor benchmark. Figure 4.2 shows the performance comparison between the non-SMP modes and the very initial SMP mode implementation in CHARM++ for the *k*Neighbor benchmark running on the representative platform C with varying message sizes. Note "PXSHM" in the figure indicates the non-SMP mode that have used posix-shared memory to optimize the inter-process communication within a physical node, while the "non-SMP" represents the general non-SMP mode that uses the underlying message-passing library (TCP/IP in this case) to do the inter-process communication. It is clear that the performance of SMP mode surprisingly lags far behind that of the non-SMP modes (i.e., ~10X slower compared with "PXSHM", and ~3X slower compared with "non-SMP") in spite of the better intra-node communication mechanism via threads which should entail that the SMP mode outperforms non-SMP modes.

Figure 4.2: Performance Comparison between non-SMP Mode and Initial SMP Mode

### 4.2 Removing Extra Invocations of Network Progress Engine

A parallel language runtime has to handle network communication work in order to run on distributed-memory parallel machines. As a design choice, each control flow (i.e., a PE in CHARM++ or a rank in MPI) calls the network progress engine after sending a message to make sure the outgoing messages gets put on the network right away, and to check for incoming messages for responsiveness. The implementation of the non-SMP mode of CHARM++ adopts such a design. In the initial implementation of the multithreaded CHARM++ runtime (i.e., the SMP mode), we kept this design and focused on ensuring the thread-safety of the runtime. Through running the *k*Neighbor benchmark, we observed a very high overhead due to expensive network progress engine calls. Realizing that the message-passing within a single node involves no network communication as they are performed via memory pointers, we reduce the overhead caused by the network progress engine by skipping its invocations for intra-node messages but keep the calls for network messages. The results of this optimization as compared to the original scheme are shown in figure 4.3. On average, we see about 35% improvement. Observing the figure, we find that *k*Neighbor performs better in SMP node than in non-SMP mode for message sizes larger than 8KB, but the performance in SMP mode is still worse for message sizes below 8KB, which leads to further investigation.

Figure 4.3: Performance before/after Skipping Network Calls

It is worth mentioning that this particular performance optimization reminds us that transforming a parallel language runtime system into a multithreaded one to take advantage of multicore chips does not just involve engineering the whole runtime to be thread-safe. It also invites us to re-think the design of the multithreaded runtime, especially in the trade-off of dividing work responsibility among different threads. Such design space exploration will be discussed in details in section 6.1.1.

### 4.3 Reducing Contention in Making Runtime Multithread-Safe

We looked at performance issues in the approach we take to make the SMP mode of CHARM++ thread-safe as we intended to optimize the intra-node communication. We concluded that efficiently handling locking and synchronization among threads in the runtime is the key factor for obtaining fast, fine-grained intra-node communication, which are reflected in three aspects as described in the following subsections.

#### 4.3.1 Memory management

In CHARM++, we found that the self-implemented default memory allocator has used a lock to protect every *malloc* and *free* call to have robust support for multithreading in the runtime. It was no surprise that *k*Neighbor performed very poorly because of the severe lock contention due to message allocation, amplified by the intensive communication. After switching to the memory allocator provided by OS, which is robustly thread-safe to be directly used in CHARM++ SMP mode, we see a significant performance improvement as 2.4 times on average for *k*Neighbor's iteration time illustrated by the third curve in figure 4.4. According to figure 4.4, it is obvious that the performance of *k*Neighbor in the current SMP mode becomes much better than the initial one after switching to OS-provided memory module (the third curve vs. the first curve), and it even exceeds the performance in the non-SMP mode (the second curve). However, compared with PXSHM (the fourth curve), the performance of SMP mode is still worse by 4.3 times on average for message sizes below 4KB. As a result, the challenges of investigating performance issues in SMP mode on a single node still remain for beating the performance of the PXSHM mode.

Figure 4.4: Performance Comparison before/after Using a Better Memory Allocator

The above finding that the contention in the memory management plays an important

| #threads | A(us)  | A/M(us) | B(us) | C(us) | D(us) | E(us) |

|----------|--------|---------|-------|-------|-------|-------|

| 1        | 1.06   | 1.03    | 0.78  | 0.80  | 1.13  | 0.68  |

| 2        | 2.23   | 1.02    | 1.30  | 1.44  | 1.53  | 2.03  |

| 4        | 6.06   | 1.05    | 3.95  | 2.14  | 2.36  | 2.73  |

| 8        | 15.35  | 1.03    | 8.71  | 3.69  | 4.72  | 7.06  |

| 16       | 36.89  | 1.06    | 22.63 | n/a   | n/a   | 14.58 |

| 24       | n/a    | n/a     | n/a   | n/a   | n/a   | 21.31 |

| 32       | 210.96 | 1.02    | n/a   | n/a   | n/a   | n/a   |

Table 4.1: Memory Allocation Time on Different Platforms.

role in the performance of the multithreaded runtime led us to investigate how the OSprovided memory allocator performs when the number of threads increases in a process. We synthesized a benchmark that every thread continuously allocates memory of the same size and deallocates at the end for 100,000 times. We run the benchmark with the varying number of threads, and take the average memory allocation time on 5 different multicore platforms mentioned earlier.

Table 4.1 shows that the default OS memory allocators tend not to scale when the number of threads increases up to the maximum number of logical CPUs on each platform. However, we should be cautious to interpret these results as real applications may not involve a great number of simultaneous memory allocations. The results here are very likely to imply the upper-bound of overhead in memory management under the multithreaded environment. Based on table 4.1, among all the five platforms, the AIX 6.1/Power 5 platform A, illustrated by the second column, did the worst with the default setting. Setting system environment variable "MALLOCMULTIHEAP" under AIX, however, improves the performance significantly as shown in the third column. In this case, the time for each memory allocation remains almost identical, indicating there is no more contention. The idea behind this setting is to use multiple heaps, one serving several threads to reduce contention on heap allocation. Although this mechanism will increase the overall memory usage and memory fragmentation, it is still a good optimization to consider thanks to the significant performance improvement it results in. Observing that the memory allocation does not scale well either on Linux plaforms, and Linux itself by default does not provide an alternative as AIX does to the best of my knowledge, we suggest a better default memory management be adopted on parallel machines running Linux. This will not only benefit multithreaded programs but also the language runtime discussed in this work.

In summary, as threads share the same memory address space, it is critical to deal with multiple, simultaneous memory allocation or deallocation requests in order to achieve thread-safety with low contention while keeping a high memory utilization (i.e., low internal/external fragmentation) at the same time. In the context of a message-passing based parallel language runtime system, the message latency includes the time spent on the memory allocation for this message. Consequently, it is necessary to check whether the overhead introduced by the contention in memory management on a particular platform slows down the runtime performance. We have noticed that much work has been done to address this issue [26, 27, 28], and we will evaluate that work in the context of the multithreaded runtime in the future.

#### 4.3.2 Granularity of critical sections

It is easier to use a big critical section to make runtime thread-safe. However, this leads to a serialization of program and poor performance. After carefully reviewing the code base of CHARM++ runtime, we removed unnecessary locks and reduced the granularity of critical sections to minimize synchronization overhead, e.g., we put the lock only around the part of the function that is not thread-safe instead of blindly putting it around the whole function body. Indeed, this is a trade-off between productivity and performance, because larger critical sections tend to be safer, while reducing their scope requires analyzing complex interactions for race conditions, and tedious debugging efforts. However, for a runtime that is at the foundation of a parallel programming system, and one that is used very often, the effort to improve performance is worthwhile.

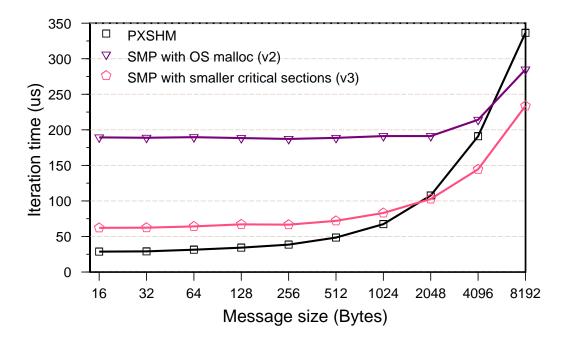

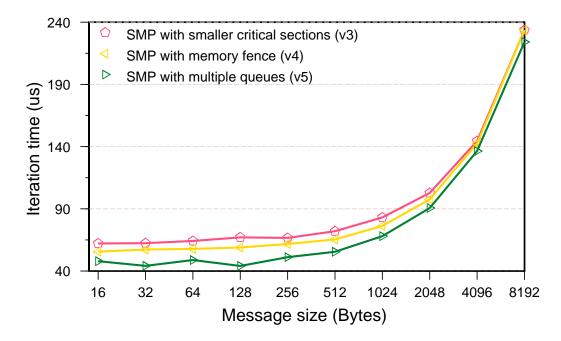

This turned out to be a significant performance improvement as indicated by figure 4.5. Compared with the previous SMP version, *k*Neighbor benchmark speeds up by an average of 2.7 times up to message size 2KB. Beyond that, we can observe a trend that the performance gain is diminishing, but still with 35.1% improvement on average for message sizes 4KB and 8KB. We believe such performance trend is caused by the fact that the execution

Figure 4.5: Performance before/after Reducing Granularity of critical sections.

time of *k*Neighbor begins to be dominated by touching every byte of the message on the receiver side. Comparing with the PXSHM version, we can see now the two performance lines cross at a message size smaller than 2KB. Additionally, it is clearly shown that the PXSHM mode has a steeper execution time increase rate than that in SMP mode. This is because we cannot avoid an extra copy from the POSIX-shared memory region to the user space for receiving the message, while such a copy is not needed in SMP mode as only the message pointer is passed to the receiver. However, due to the Non-Uniform Memory Access (NUMA) effect exhibited by an increasing amount of multicore nodes on parallel machines and the "first-touch" memory allocation policy, if the message receiver accesses the data often, it may be better to make a message copy instead of only sending a memory pointer. This will be left to be examined in the future work. The single-node performance issues examined in this chapter are restrained within one NUMA node where every core has the same memory access latency.

#### 4.3.3 Message queues

Producer-Consumer Queue (PCQueue) is a commonly used data structure in parallel language RTS to synchronize multiple threads. For example, it is used in the Cilk [29] scheduler for work-stealing. CHARM++ RTS uses PCQueue for various purposes to synchronize the worker threads and communication thread with messages. For example, the communication thread as a producer pushes a message into a worker thread's message queue for processing. The simplest way to ensure correctness is to enforce a lock every time a thread accesses the queue. This was the original implementation in CHARM++, and it suffered severe thread contention, especially when the number of producers increased.