### MITIGATING VARIABILITY IN HPC SYSTEMS AND APPLICATIONS FOR PERFORMANCE AND POWER EFFICIENCY

#### BY

#### BILGE ACUN

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

Urbana, Illinois

#### Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor Tarek Abdelzaher Professor Josep Torrellas Dr. Pete Beckman, Argonne National Laboratory

### Abstract

Power consumption and process variability are two important, interconnected, challenges of future generation large-scale High Performance Computing (HPC) data centers. For example, current production petaflop supercomputers consume more than 10 megawatts of machine and cooling power that costs millions of dollars every year [1]. As HPC moves towards exascale computing, these costs will increase and power consumption is expected to become a major concern. Not solely dynamic behavior of HPC applications but also dynamic behavior of HPC systems makes it challenging to optimize the performance and power efficiency of large scale applications. Dynamic behavior of applications include irregular or imbalanced applications. Dynamic behavior of HPC systems include thermal, power, and frequency variations among processors. Smart and adaptive runtime systems have great potential to handle these challenges transparently from the application.

In this dissertation, I first analyze frequency, temperature, and power variations in large-scale HPC systems using thousands of cores and different applications. After I identify the cause of each of these variations, I propose solutions to mitigate these variations to improve performance and power efficiency. When analyzing frequency variation, I attribute manufacturing related intrinsic differences in the chips' power efficiency as the culprit behind frequency variation under dynamic overclocking. I propose speed-aware dynamic load balancing strategies to mitigate the performance overhead due to frequency variation. When analyzing temperature variation, I focus on inefficiencies in fan-based air cooling systems. I propose proactive and decoupled fan control mechanisms that reduce temperature varia-

tions and reduce cooling power consumption by predicting core temperatures using a learning based model. When analyzing power variations, I identify manufacturing related sources of power variation that are static and dynamic. I propose different variation aware node assembly methods to mitigate the power variation. Finally, I propose a fine-grained runtime based technique to mitigate application level variations that are caused by the characteristics of the application itself (for example, applications with different kernel types or phases) in order to reduce the energy consumption.

To my family.

### Grants

This work was supported by multiple generous funding sources, and it made use of resources from several supercomputing centers. I would like to thank all of the following sources that contributed towards:

Fellowship sources: The Saburo Muroga Endowed Fellowship by the Department of Computer Science at University of Illinois at Urbana-Champaign (UIUC) provided support for academic year 2012-2013.

Assistantship sources: This work was supported by the National Institutes of Health (grant number PHS-5-P41-RR05969) and by Cisco Systems Inc. with their gift award (CG 587589).

Supercomputing centers and allocations: This work would not be possible without the Cori and Edison supercomputers at National Energy Research Scientific Computing Center (NERSC), Stampede at Texas Advanced Computing Center (TACC), Cab at Lawrence Livermore National Laboratory (LLNL), Blue Waters at UIUC, National Center for Supercomputing Applications (NCSA), and Minsky at IBM T.J. Watson Research Center.

This research used resources of NERSC, which is supported by the Office of Science of the U.S. Department of Energy (DOE) (contract number DE-AC02-05CH11231). This work used the Extreme Science and Engineering Discovery Environment (XSEDE), which is supported by National Science Foundation (grant number OCI-1053575). This research is part of the Blue Waters sustained-petascale computing project, which is supported by the National Science Foundation (award number OCI 07-25070) and the State of Illinois. Blue Waters

is a joint effort of UIUC and NCSA. This research also used computer time on Livermore Computing's high performance computing resources, provided under the M&IC Program. Finally, I am thankful to Prof. Tarek Abdelzaher for letting me use the testbed at UIUC for experimentation (grant number NSF CNS 09-58314).

## Table of Contents

| ist of Figures                         | 1                                      |

|----------------------------------------|----------------------------------------|

| ist of Tables                          | 5                                      |

| ist of Algorithms                      | 6                                      |

| sist of Abbreviations and Acronyms     | 6                                      |

| CHAPTER 1 Overview                     | 7<br>10                                |

| 2.1 An Adaptive Runtime System for HPC | 12<br>15<br>19<br>22<br>24<br>26<br>27 |

| 3.1 Experimental Setup                 | 28<br>29<br>36<br>45<br>50             |

| 4.1 Disable Turbo Boost                | 53<br>54<br>55<br>57<br>58<br>68       |

| 4.J DUIIIII. AI V                      | UO                                     |

| СНАРТ | TER 5 Mitigating Temperature Variation            | 69  |

|-------|---------------------------------------------------|-----|

| 5.1   | Motivation and Observations                       | 72  |

| 5.2   | Neural Network-Based Temperature Prediction Model | 76  |

| 5.3   | Model-Guided Proactive Fan Control                | 81  |

| 5.4   | Mitigating Intra-Chip Temperature Variation       | 91  |

| 5.5   | Related Work                                      | 93  |

| 5.6   | Summary                                           | 95  |

| СНАРТ | TER 6 Mitigating Across Component Power Variation | 96  |

| 6.1   | Understanding the Sources of the Power Variation  | 97  |

| 6.2   | Power Variation Analysis of Node Components       | 99  |

| 6.3   | Variation Aware Node Assembly                     | 103 |

| 6.4   | Summary                                           | 109 |

| СНАРТ | TER 7 Mitigating Application-Level Variability    | 110 |

| 7.1   | Motivation                                        | 112 |

| 7.2   | Runtime Guided Frequency Regulation               | 117 |

| 7.3   | Experimental Results                              | 126 |

| 7.4   | Related Work                                      | 129 |

| 7.5   | Summary                                           | 130 |

| СНАРТ | TER 8 Conclusion                                  | 131 |

| 8.1   |                                                   | 132 |

| REFER | ENCES                                             | 134 |

# List of Figures

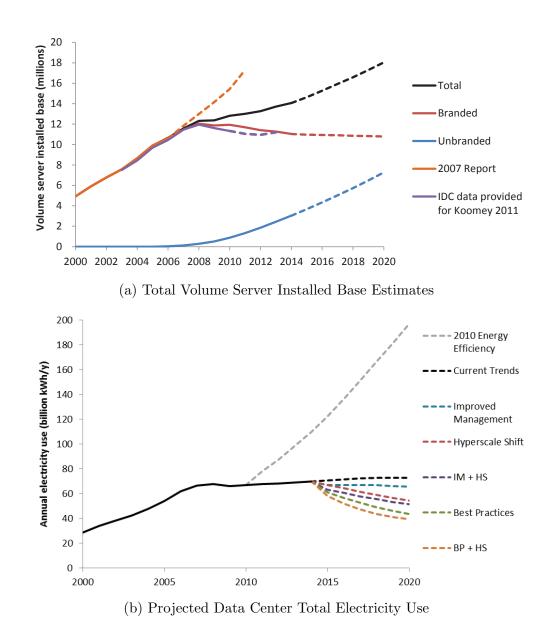

| 1.1 | Figures are taken from "United States Data Center Energy Usage Report" published by the Lawrence Berkeley National Laboratory in 2016 [3]              |   | 8                               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------|

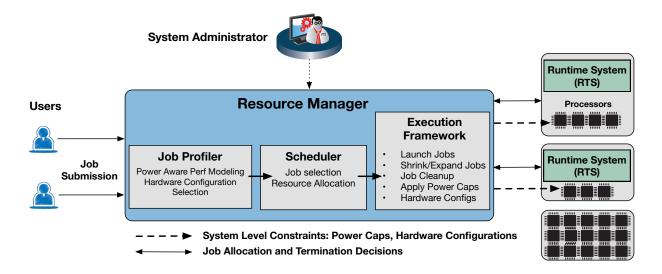

| 2.1 | Figure shows overall system design with two major components interacting with each other: Resource Manager and the Runtime System                      |   | 13                              |

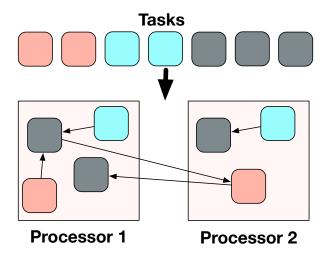

| 2.2 | Illustration of overdecomposition with migratable objects and message driven execution in runtime system                                               |   | 16                              |

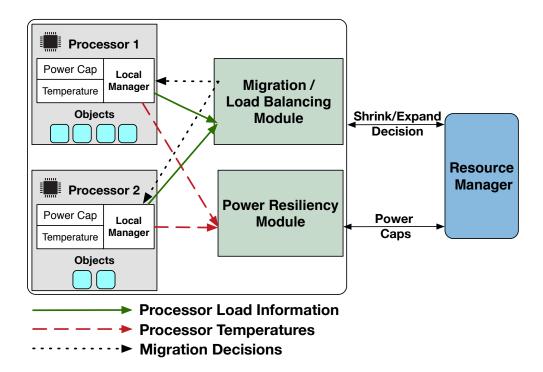

| 2.3 | Various components of adaptive runtime system and their interaction with the resource manager.                                                         |   | 18                              |

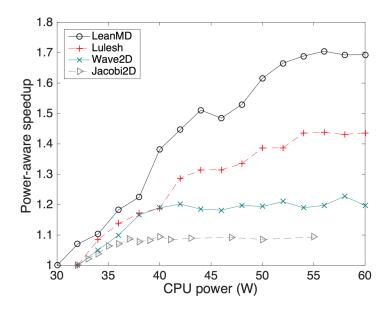

| 2.4 | Power-aware speedups of four applications running on 20 nodes. The applications vary from being CPU intensive to memory intensive                      |   | 20                              |

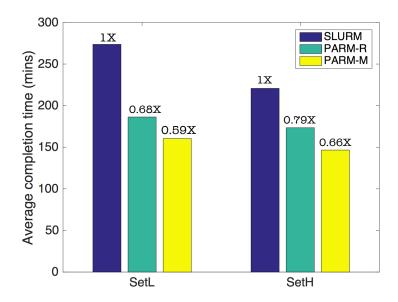

| 2.5 | Comparison of average completion time of jobs with SLURM and PARM, in Rigid(R) and Malleable(M) variants. SetL has jobs that have low sen-             | • |                                 |

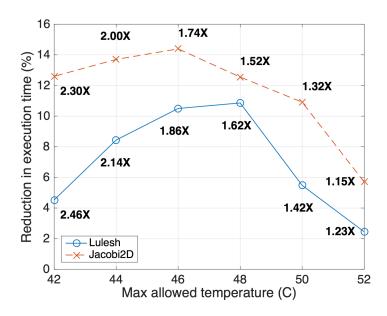

| 2.6 | sitivity to CPU power and SetH has jobs that have high sensitivity Reduction in execution time and change in MTBF for different temperature thresholds |   | <ul><li>21</li><li>23</li></ul> |

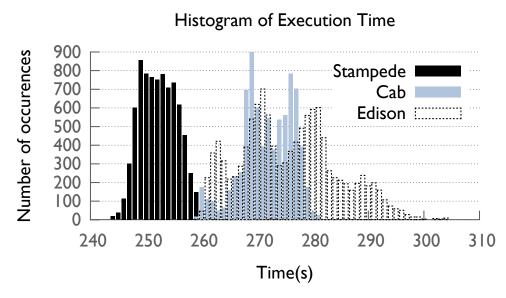

| 3.1 | The distribution of benchmark times on 512 nodes of each machine looping MKL-DGEMM a fixed number of times on each core                                |   | 36                              |

| 3.2 | Average frequency shows a negative correlation with total execution time on both Edison, Cab and Stampede when running MKL-DGEMM                       |   | 37                              |

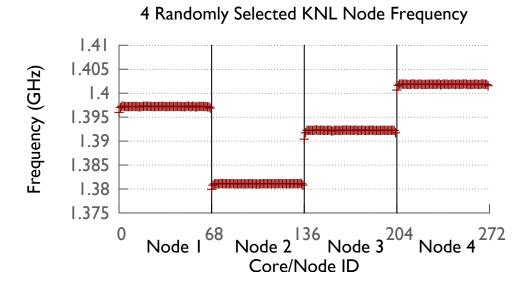

| 3.3 | KNL execution time variability of 256 nodes 17408 cores. Overall variation is 53.4%. Frequency variation is almost 200 MHz                             |   | 38                              |

| 3.4 | Plots show the execution time and frequency of four randomly selected nodes sorted by the core and node IDs                                            |   | 40                              |

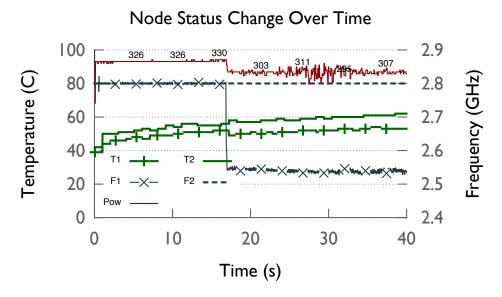

| 3.5 | Plot shows the power (Pow (W)) of a randomly selected node, temperature (T1, T2) and frequency (F1, F2) of the two chips on the node                   |   | 41                              |

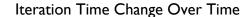

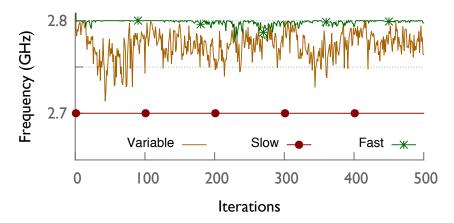

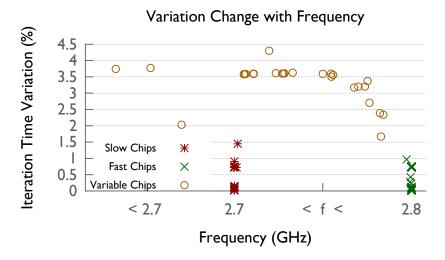

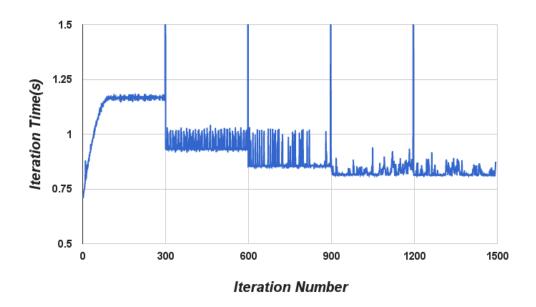

| 3.6 | Iteration time (top plot) and frequency (bottom plot) over iterations are shown from cores selected from 3 chips showing distinct behavior: slow,      | • |                                 |

| 3.7 | variable, and fast                                                                                                                                     |   | 42                              |

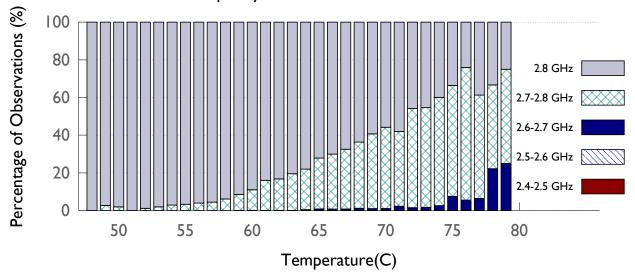

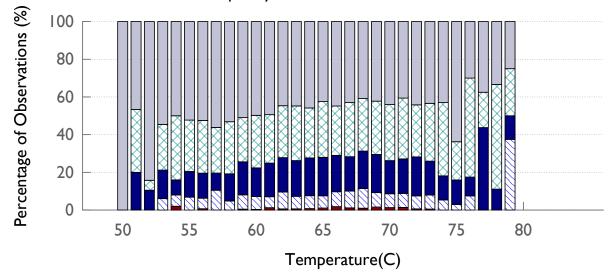

| 3.8        | Plots show what percentage of the chips run at what frequency in each temperature level for NAIVE-DGEMM (left plot) and MKL-DGEMM (right plot) benchmarks. The data points are collected from the whole execution of the benchmarks and classified according to their temperature bins. The chips' operating temperatures are not directly correlated with their frequency under the heavier load of MKL-DGEMM | 46       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

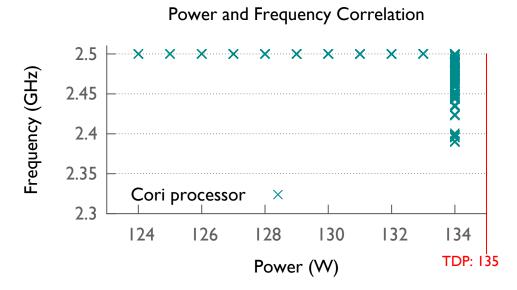

| 3.9        | Processors that reach TDP drops their frequency and stay at 134 W level, just under 1 W than TDP. 512 Haswell processors in Cori platform are shown.                                                                                                                                                                                                                                                           | 49       |

| 3.10       | The processors that hit the power cap, the ones circled, have a wide range of temperatures similar to the ones that do not hit. Temperature does not                                                                                                                                                                                                                                                           |          |

|            | directly correlate with power                                                                                                                                                                                                                                                                                                                                                                                  | 50       |

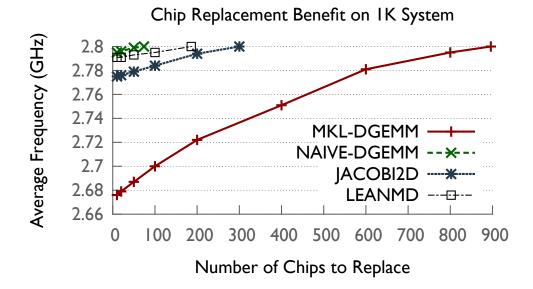

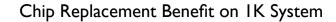

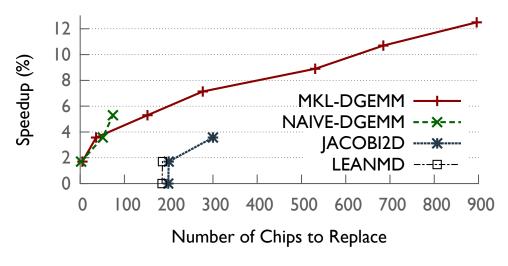

| 4.1<br>4.2 | How many chips we should replace to get performance benefit? Throughput of all cores when 1 core is left idle from chips starting from                                                                                                                                                                                                                                                                         | 56       |

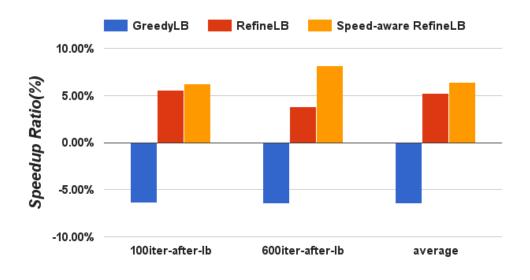

| 4.3        | the slowest chip                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>60 |

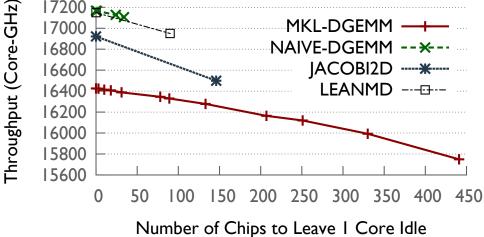

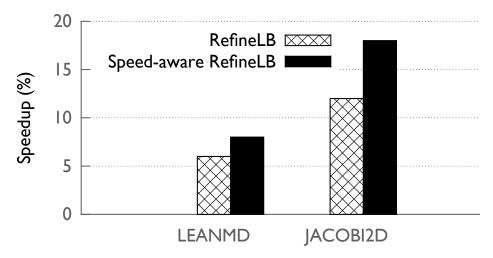

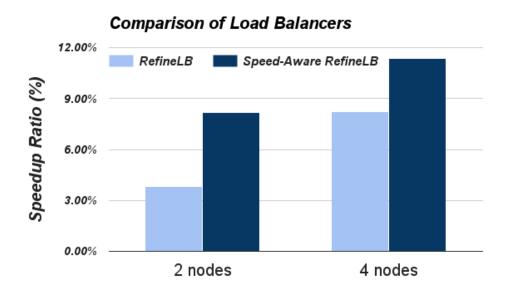

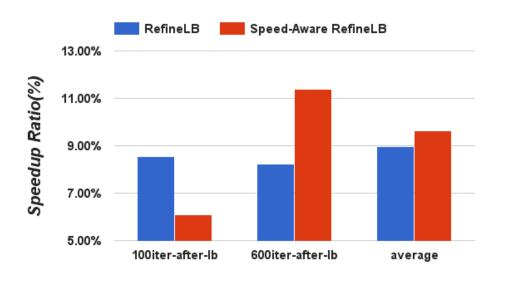

| 4.4<br>4.5 | Homogeneous Processors under Turbo-Boost using Speed-aware RefineLB RefineLB and Speed-aware RefineLB performance compared to without                                                                                                                                                                                                                                                                          | 61       |

|            | load balancing case                                                                                                                                                                                                                                                                                                                                                                                            | 62       |

| 4.6        | Comparing RefineLB and Speed-aware RefineLB                                                                                                                                                                                                                                                                                                                                                                    | 65       |

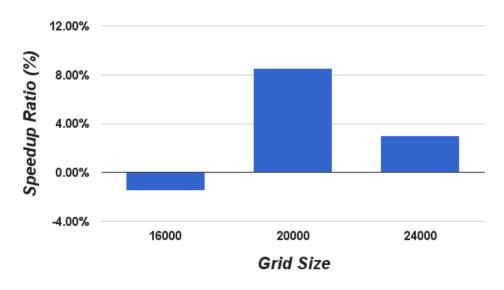

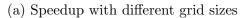

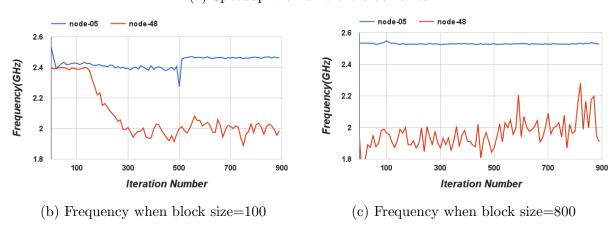

| 4.7<br>4.8 | Speed-aware RefineLB performance on Jacobi-2D with different grid sizes. Speed-aware RefineLB performance on Jacobi-2D with varying block size.                                                                                                                                                                                                                                                                | 66       |

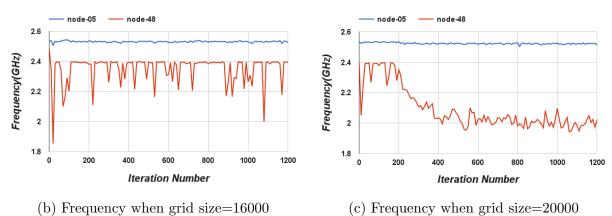

|            | Load balancer is triggered at iteration 800                                                                                                                                                                                                                                                                                                                                                                    | 67       |

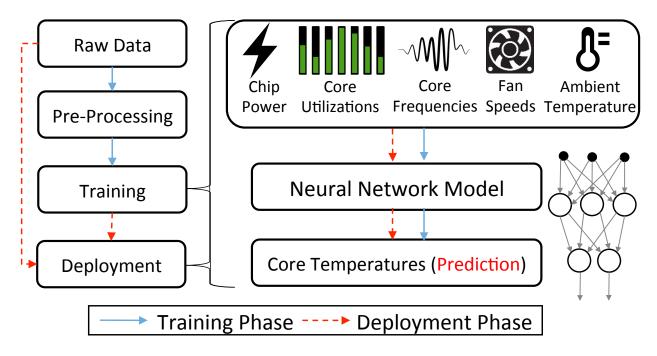

| 5.1        | Neural network-based thermal prediction approach                                                                                                                                                                                                                                                                                                                                                               | 71       |

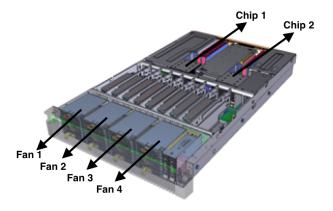

| 5.2        | POWER8 server node architecture illustration                                                                                                                                                                                                                                                                                                                                                                   | 72       |

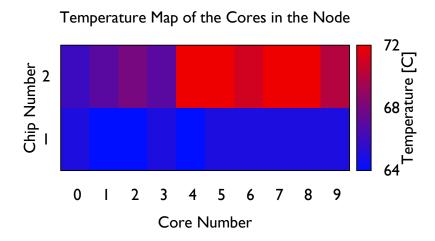

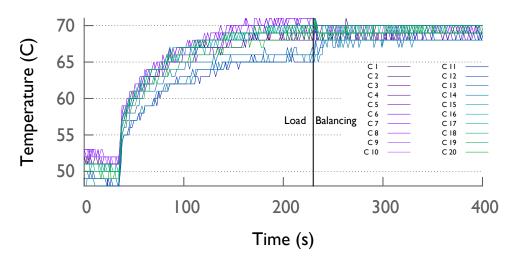

| 5.3        | There is an 8°C steady-state temperature variation among the cores within a node running a balanced benchmark, LeanMD                                                                                                                                                                                                                                                                                          | 73       |

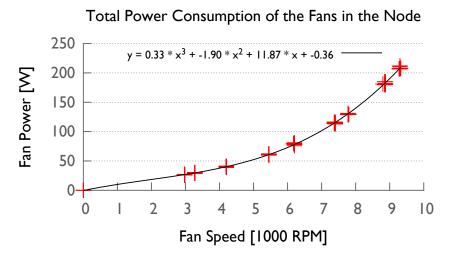

| 5.4        | Fan power grows cubic polynomially with respect to fan speed                                                                                                                                                                                                                                                                                                                                                   | 74       |

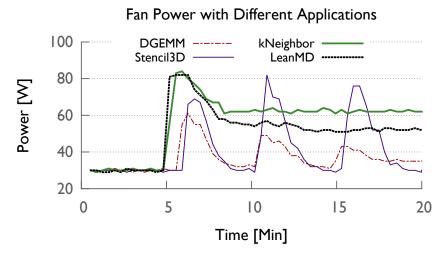

| 5.5<br>5.6 | Fans show different behavior for different applications                                                                                                                                                                                                                                                                                                                                                        | 74       |

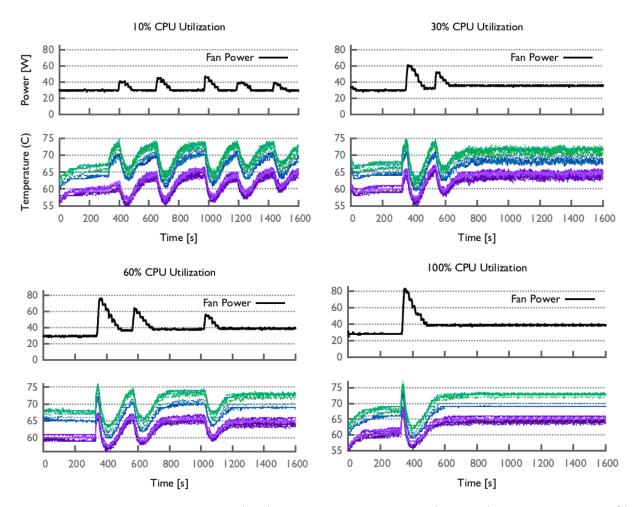

| 5.7        | plots represent cores in Chip-1 and Chip-2 respectively                                                                                                                                                                                                                                                                                                                                                        | 75       |

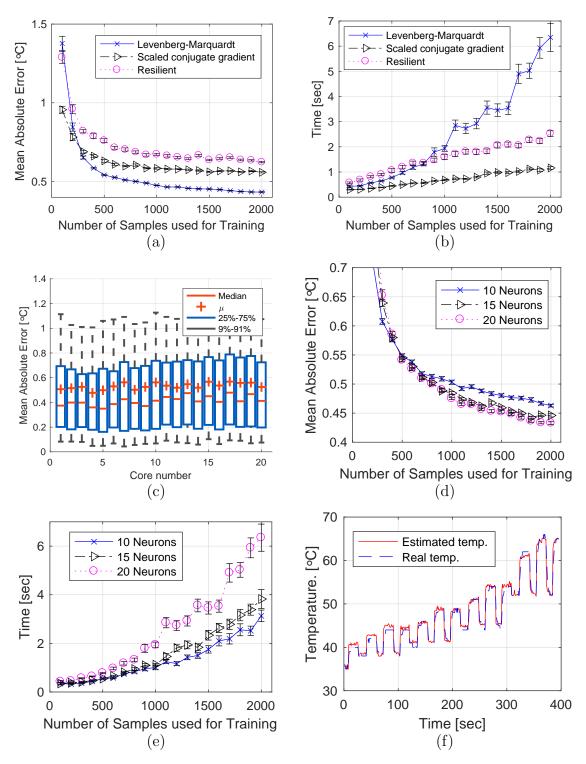

|            | solute error per core using Levenberg-Marquardt algorithm; (d) Mean absolute error using different number of neurons; (e) Training time using different number of neurons; and (f) Model validation while increasing CPU frequency. Plots are shown with 95% confidence interval                                                                                                                               | 80       |

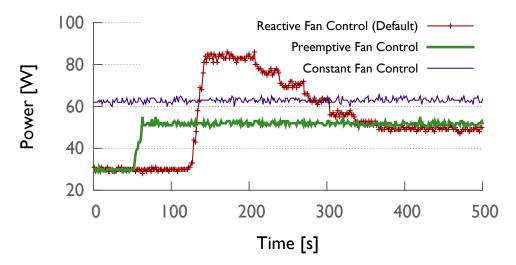

| 5.8        | Power and temperature comparison of the three fan control mechanisms with <i>LeanMD</i> benchmark starting at 100s. (Preemptive cooling has been started 50s ahead of time for clarification of the plots and the idea. It can achieve a similar effect if triggered within few seconds of the application                                                                                                     |          |

|            | start as well.)                                                                                                                                                                                                                                                                                                                                                                                                | 87       |

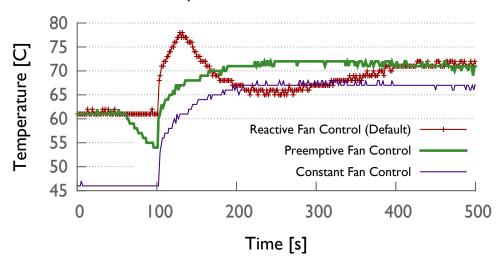

| 5.9  | The difference between the maximum and the stable fan gives the power            |            |

|------|----------------------------------------------------------------------------------|------------|

|      | reduction that preemptive cooling can achieve with LeanMD                        | 88         |

|      | Precooling should start within a few seconds of application start at the latest. | 88         |

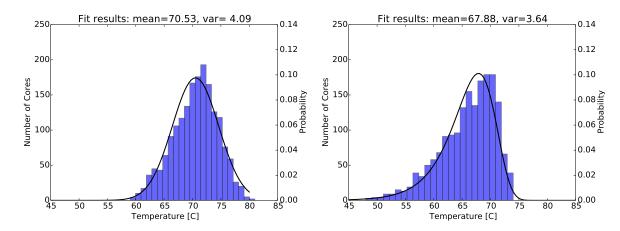

| 5.11 | , , , , , , , , , , , , , , , , , , ,                                            |            |

|      | nel in two different architectures: Cori (left) with Intel Xeon Haswell pro-     |            |

|      | cessors and Minsky (right) with IBM POWER8 processors                            | 89         |

| 5.12 | Steady-state temperature distribution of different applications on Minsky:       |            |

|      | kNeigbor, LeanMD, Stencil3D (in order). Despite their different character-       |            |

|      | istics, applications show almost the same temperature distribution when          |            |

|      | the cores are used in balance                                                    | 89         |

| 5.13 | The top plot shows steady-state temperature distribution of the DGEMM            |            |

|      | benchmark with decoupled fans on Minsky. (Notice the range change in             |            |

|      | the y-axis.) Independent fan control cannot remove temperature variations        |            |

|      | fully overall, because of the intra-chip variations                              | 90         |

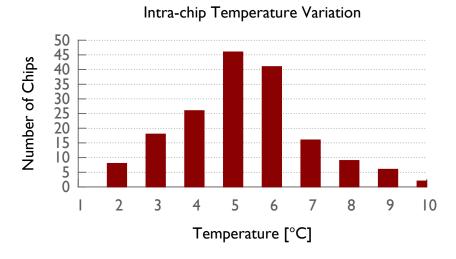

| 5.14 | The distribution of intra-chip temperature variation among cores                 | 90         |

| 5.15 | Load balancing reduces within chip temperature variations from 5°C to            |            |

|      | 2°C. (Inter-chip variation is mitigated by decoupled fans.)                      | 92         |

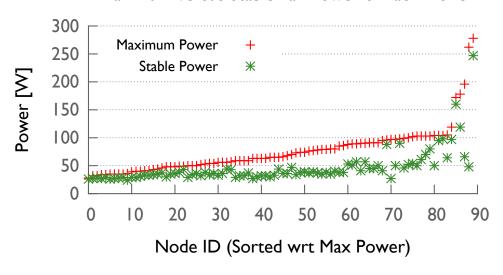

| 0.1  | N. I                                                                             |            |

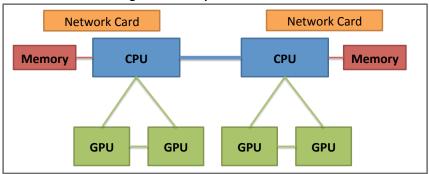

| 6.1  | Node architecture of Oak Ridge National Laboratory (ORNL) Summit-                |            |

|      | Dev Supercomputer with IBM Power8 CPUs, NVIDIA Tesla P100 GPUs,                  | o <b>-</b> |

|      | DDR4 memory and Mellanox EDR Infiniband network adapter                          | 97         |

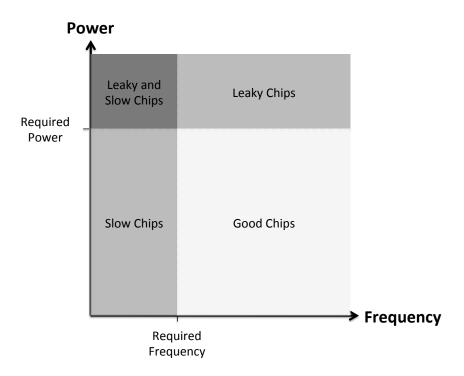

| 6.2  | Power and frequency characterization of a manufacturing yield. Note that         |            |

|      | the distribution ratios in the figure do not represent actual numbers            | 98         |

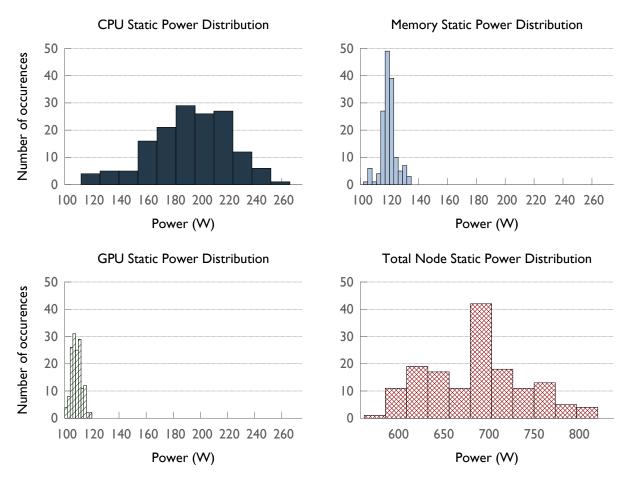

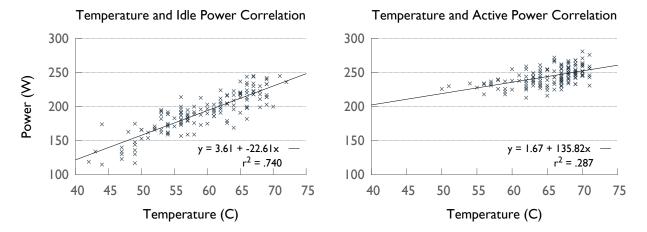

| 6.3  | Static (idle) power distribution of node components (notice the x axis           |            |

|      | 0 0                                                                              | 101        |

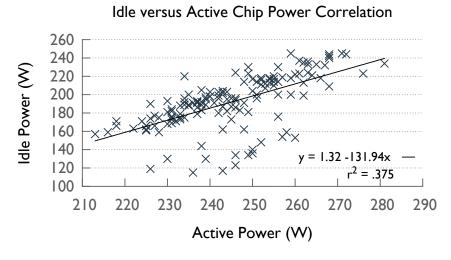

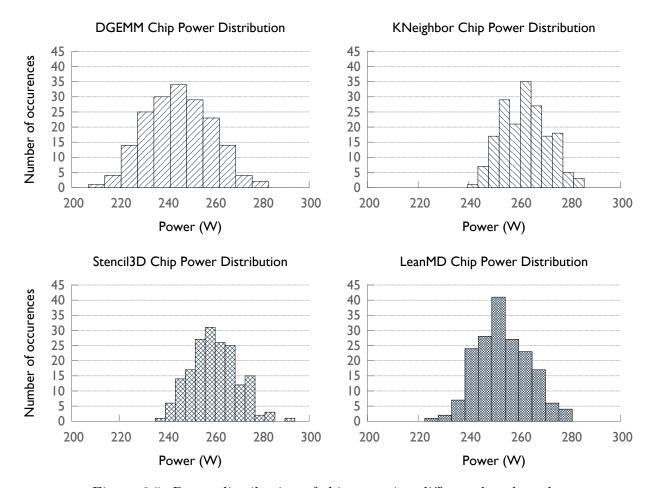

| 6.4  | 1 0                                                                              | 101        |

| 6.5  | 1 0                                                                              | 102        |

| 6.6  |                                                                                  | 102        |

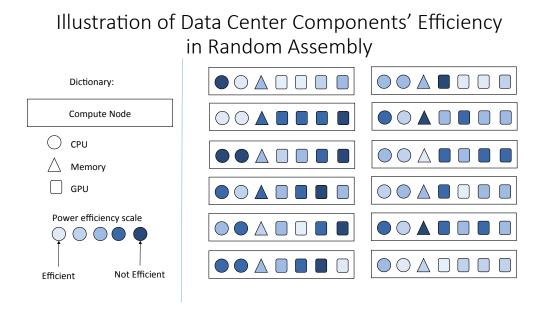

| 6.7  | V VI                                                                             | 103        |

| 6.8  | V VI                                                                             | 104        |

| 6.9  | Distribution of the active power of node components: CPU, GPU, Memory            |            |

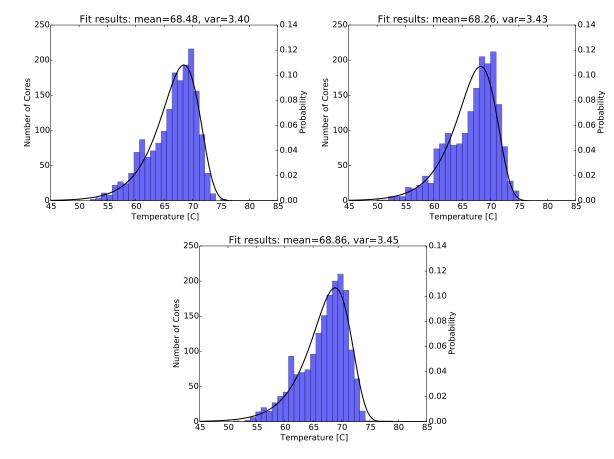

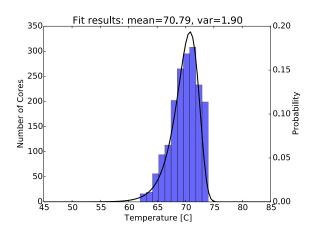

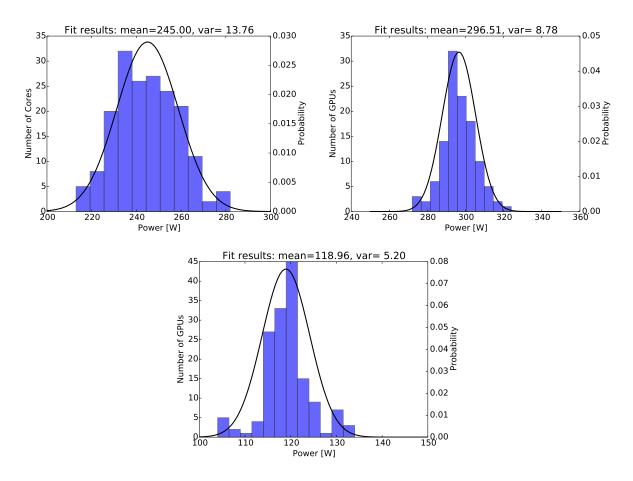

|      | (in order) fit to Gaussian distribution                                          | 107        |

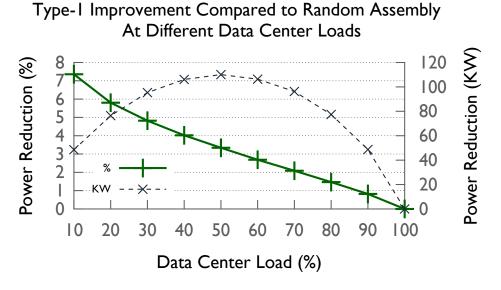

| 6.10 | Power reduction with Type-1 node assembly compared to random assem-              |            |

|      | bly at different data center loads with a size of 5,000 nodes. The nodes         |            |

|      | that are not active are assumed to be turned-off                                 | 107        |

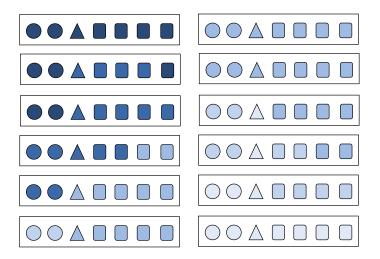

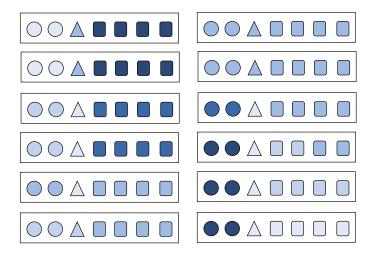

| 6.11 | Illustration of node assembly Type-2: Application characteristics aware          |            |

|      | V                                                                                | 108        |

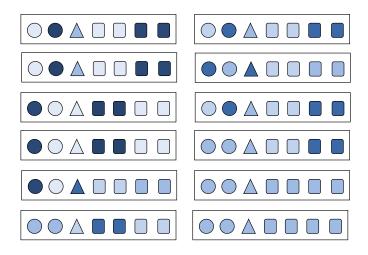

| 6.12 | Illustration of node assembly Type-3: Balanced power node assembly               | 108        |

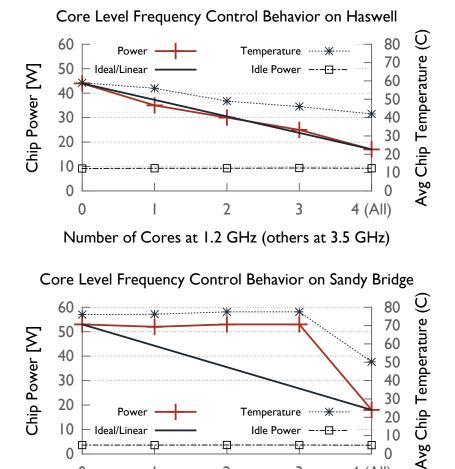

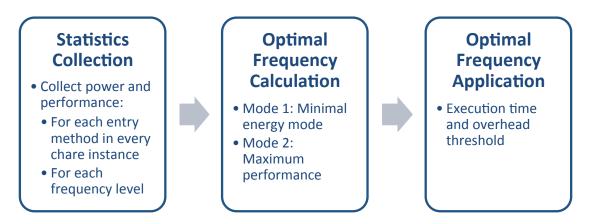

| 7.1  | Core level Dynamic Voltage and Frequency Scaling (DVFS) on Haswell               |            |

| 1.1  | architecture shows proportional/linear decrease in power when core fre-          |            |

|      | quencies are dropped one by one. On the other hand, since Sandy Bridge           |            |

|      | do not have per core voltage regulators, all core frequencies needs to be        |            |

|      |                                                                                  | 113        |

| 7 2  |                                                                                  |            |

| 7.2  | Core level frequency scaling on IBM Power8 chip                                  | 114        |

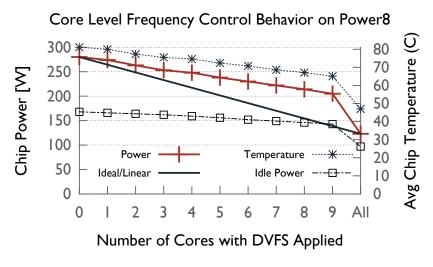

| 7.3  | Timeline of two processors running the OpenATOM benchmarks. Each                |     |

|------|---------------------------------------------------------------------------------|-----|

|      | color represents a Charm++ entry method. Notice how different entry             |     |

|      | methods are executed on the two processes at the same time range                | 117 |

| 7.4  | Code snippet from Charm++ stencil application                                   | 119 |

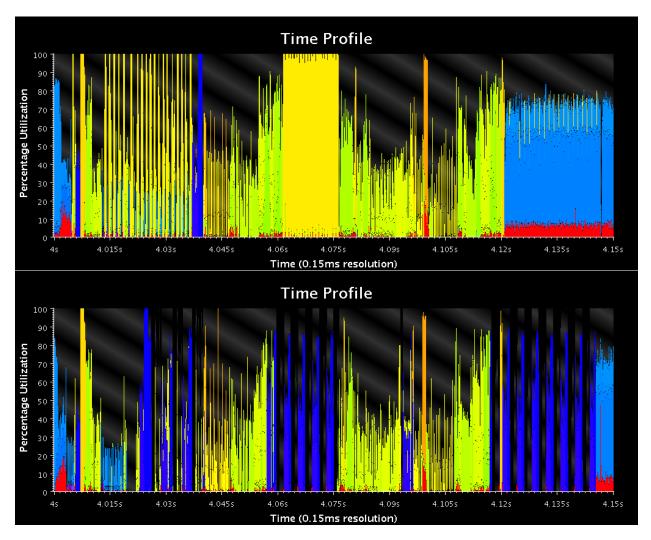

| 7.5  | Runtime control flow                                                            | 120 |

| 7.6  | Optimal frequency of DGEMM kernel remains more or less stable despite           |     |

|      | the number of active cores running the kernel, wheres optimal frequency         |     |

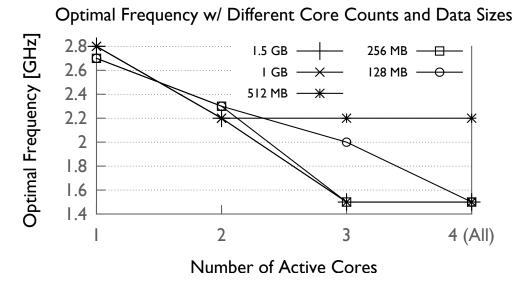

|      | of the MEMOPS kernel drops significantly as more cores are activated            | 122 |

| 7.7  | Optimal frequency of the MEMOPS kernel depends more on the number               |     |

|      | of active cores than the data size                                              | 122 |

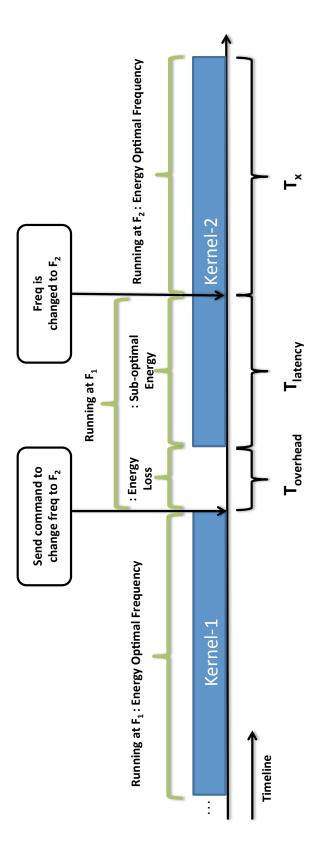

| 7.8  | Timeline of two kernels executing one another where the runtime applies         |     |

|      | optimal frequency.                                                              | 124 |

| 7.9  | Timeline of the synthetic benchmark having two kernels (represented by          |     |

|      | light blue and dark blue colors) randomly overlapping. Each line represents     |     |

|      | a process, in this case four processes are running in parallel                  | 124 |

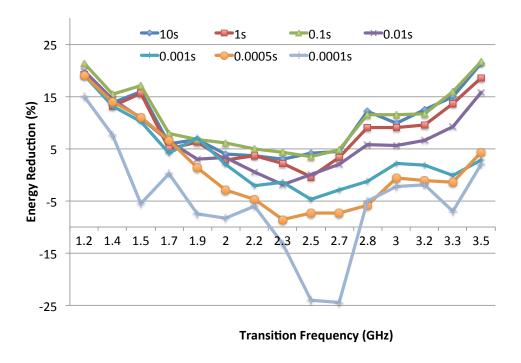

| 7.10 | Plots shows how much energy can be reduced if a kernel that has an en-          |     |

|      | ergy optimal frequency of 2.3 GHz is transitioned from different frequency      |     |

|      | levels. Different lines represent different kernel durations                    | 126 |

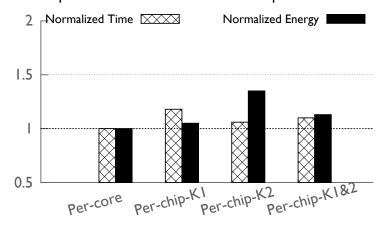

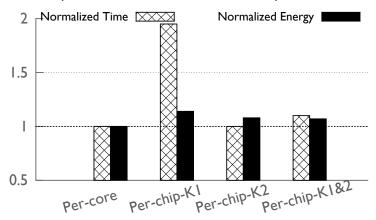

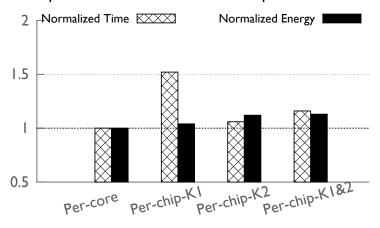

| 7.11 | Per-core: Uses energy optimal frequency for each kernel in core level.          |     |

|      | Per-chip-K1: Uses per-chip DVFS with optimal frequency of kernel-               |     |

|      | 1 which is 2.2 GHz, <b>Per-chip-K2:</b> Uses per-chip DVFS with optimal         |     |

|      | frequency of kernel-2 which is 3.3 GHz, <b>Per-chip-K1&amp;2:</b> Uses per-chip |     |

|      | DVFS with optimal frequencies of kernel 1 and 2 running together which          |     |

|      | is 2.7 GHz                                                                      | 128 |

### List of Tables

| 2.1        | Desired access to hardware-level measurement and controls. ✓: There is support and access. ✗: There is no support. ○: Hardware has support, but the system's software lacks support or forbids access |   | 26       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|

| 3.1        | Platform hardware and software details                                                                                                                                                                |   | 35       |

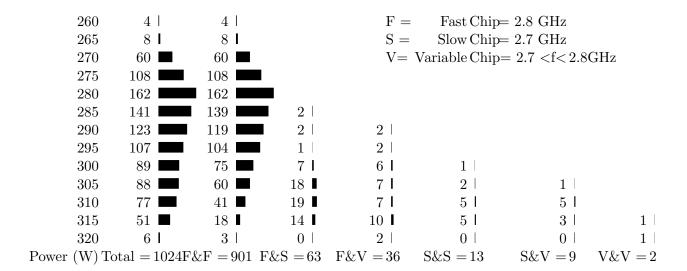

| 3.2        | Distribution of observed steady-state frequencies of 1K Chips on Edison                                                                                                                               |   | 44       |

| 3.3        | Frequency distribution of MKL-DGEMM on Cab                                                                                                                                                            |   | 44       |

| 3.4<br>3.5 | Frequency distribution of MKL-DGEMM on Stampede                                                                                                                                                       |   | 44       |

| 4.1        | Percentage slowdown of applications when the frequency is fixed at maxi-                                                                                                                              |   |          |

| 4.0        | mum frequency of 2.4GHz                                                                                                                                                                               |   | 54       |

| 4.2        | Platform hardware details                                                                                                                                                                             |   | 62       |

| 4.3        | Object Migration with Different Load Balancers                                                                                                                                                        | • | 63       |

| 5.1        | Peak fan power and energy consumption of different fan control mecha-                                                                                                                                 |   |          |

| ۲.0        | nisms and benchmarks                                                                                                                                                                                  |   | 83       |

| 5.2        | Decoupling the left two and the right two fans reduces chip-to-chip tem-                                                                                                                              |   | 0.5      |

| 5.3        | perature variations, power, and energy consumption                                                                                                                                                    |   | 85<br>85 |

| 7.1        | Platform hardware and software details                                                                                                                                                                |   | 112      |

# List of Algorithms

| 1 | Refinement Load Balancing Algorithm | 59 |

|---|-------------------------------------|----|

| 2 | Speed-Aware Refinement Algorithm    | 59 |

### List of Abbreviations and Acronyms

CMOS Complementary Metal-Oxide-Semiconductor. 28, 70, 97

**DOE** Department of Energy. v, 7, 12, 69

**DVFS** Dynamic Voltage and Frequency Scaling. 3, 4, 9, 91, 94, 110–117, 123, 126, 128–130

FIVR Fully Integrated Voltage Regulator. 112

**HPC** High Performance Computing. ii, vii, 7, 9, 10, 12–15, 19, 22, 24, 25, 27–29, 32, 38, 50, 51, 53, 91, 93, 94, 96, 111, 131, 133

ILP Integer Linear Program. 20

LBM Load Balancing Module. 17

LLNL Lawrence Livermore National Laboratory. v, 9, 30

LM Local Manager. 17, 25

NCSA National Center for Supercomputing Applications. v, vi, 30

NERSC National Energy Research Scientific Computing Center. v, 29, 30, 48

ORNL Oak Ridge National Laboratory. 3, 9, 69, 96, 97

PARM Power Aware Resource Manager. 19, 20

PRM Power Resiliency Module. 17, 18, 21, 23, 24

RAPL Running Average Power Limit. 19, 47, 110

RM Resource Manager. 25

RTS Runtime System. 17, 53, 76

TACC Texas Advanced Computing Center. v, 30

**TDP** Thermal Design Power. 19, 35, 47, 48, 97

UIUC University of Illinois at Urbana-Champaign. v, vi, 7, 62

CHAPTER 1

### Overview

Just as no two people are alike, the same can be said for processors. Just as an ideal relationship should accommodate for differences, an ideal system should accommodate the same at scale.

As the size of the data centers and HPC centers keeps growing, power consumption grows as well. Current petascale systems, such as Blue Waters supercomputer at UIUC, consume tens of megawatts of power leading to millions of dollars in energy bills, significant power strains on local, state, or regional energy grid systems, and the environmental impact on natural resources that provide the power for the supercomputer. As the scale has been growing rapidly over the last few decades, the extrapolations of the trends has shown that each data-center may need their own nuclear power plants for operational energy needs in near future. This has made scientists and engineers take action to improve power and energy efficiency of data centers. For example, the DOE set a 20 MW power goal for an exascale system to be built [2]. Fortunately, the efforts to improve the design and operation of the data centers have been paying off. A 2016 report by Lawrence Berkeley National Laboratory shows that the total energy consumption of United States data centers has been flat-lined despite the increased volume of installed servers [3]. As shown in Figure 1.1, the predictions show that the energy usage may remain constant until 2020, as the in-efficient practices are replaced with more efficient technologies. These efficient practices include not only hardware related advancements, such as optimizing the idle power consumption

Figure 1.1: Figures are taken from "United States Data Center Energy Usage Report" published by the Lawrence Berkeley National Laboratory in 2016 [3].

of the processors, but also improved operations of the data center, such as increasing the average utilization of the servers. However, for beyond 2020, the report cautions that further technological advancements are necessary to ensure that the energy demand does not grow at the rate proportional to the growth of the data centers as once it used to be in early 2000s.

It is important to note that the majority (as much as 80%) of the data center electricity is spent by servers and infrastructure divided equally among them [3]. Servers and infrastructure costs, which includes cooling, are the focus of this dissertation. The rest of the electricity is consumed by network and storage, which is about less than 20% [3].

It is also important to note the motivations behind reducing the energy versus power consumption which may not necessarily be the same. Some supercomputing facilities, such as LLNL, only pay energy charge per kWh, despite they have a contracted maximum power capacity [4]. Therefore, reducing the energy consumption directly reduces the costs. On the other hand, some other facilities, such as ORNL that hosts the largest supercomputer in the United States – Titan, is charged based on its maximum power usage [4]. Moreover, power line infrastructure of the data center can have a maximum draw limit. Therefore, reducing the maximum power usage or increasing the throughput under a strict power budget can be a motivation to reduce the costs. Hence, power and energy efficient system design have both their own merits.

This dissertation proposes novel software and hardware techniques to improve power and energy efficiency of data centers specifically by mitigating various kinds of variability in processors. A unified model where the runtime dynamically interacts with the data center's resource manager is also introduced for this purpose. DVFS and power capping are common approaches to reduce the energy consumption or power consumption. Naive usage of these methods can lead to performance degradation which is unfavorable by HPC users. Not only the dynamic behavior of HPC applications (such as irregular or imbalanced applications) but also the dynamic behavior of HPC systems (such as thermal, power variations among processors) can cause high overhead when DVFS, and power capping methods are applied naively. Smart and dynamic runtime systems have great potential handling these challenges and improving performance and power efficiency transparent from the application under user

or administrator supplied constraints.

To understand the system variability, first, this dissertation gives a detailed analysis and identification the sources of temperature, power, and frequency variation in large-scale HPC systems. Then, novel ways to reduce the different types of variation are proposed to improve performance, power, and energy efficiency with minimal or no performance overhead.

#### 1.1 Dissertation Organization

The dissertation is organized as follows:

Chapter 2 gives a high level overview of a data center system design where the resource manager interacts with the runtime of the application dynamically to do performance, power and energy optimizations. This chapter contains materials from my co-authored article "Power, Reliability, and Performance: One System to Rule them All" published in the IEEE Computer journal [5].

Chapter 3 gives a detailed analysis of frequency, power and temperature at large-scale using top supercomputers. It also shows how manufacturing related variations cause performance variations if the processors are running under dynamic-overclocking. This chapter revises and adds upon my paper "Variation Among Processors Under Turbo Boost in HPC Systems" published in International Conference on Supercomputing [6].

Chapter 4 provides evaluations of different solutions to mitigate the frequency variation. Frequency variation can degrade the performance of tightly coupled HPC applications. Solutions to mitigate the performance degradation include: disabling Turbo Boost, replacing slow chips, idling cores, and dynamic task redistribution. This chapter uses data from my articles "Variation Among Processors Under Turbo Boost in HPC Systems" published in International Conference on Supercomputing [6] and "Mitigating Processor Variation through Dynamic Load Balancing" published in IEEE International Parallel and Distributed Processing Symposium Workshops [7].

Chapter 5 focuses on temperature variation. First, it provides a temperature prediction model using neural networks. Then, it gives solutions to mitigate temperature variation with the help of the prediction model. The solutions include: a proactive fan control mechanism and a model-guided temperature balancing algorithm. This chapter includes work from my paper "Support for Power Efficient Proactive Cooling Mechanisms" published in IEEE International Conference on High Performance Computing, Data and Analytics [8] as well as my paper "Neural Network-Based Task Scheduling with Preemptive Fan Control" published in International Workshop on Energy Efficient Supercomputing [9].

Chapter 6 proposes techniques address power variation. Two techniques are analyzed to mitigate the power variation. These are a power-variation aware node assembly method and a variation-aware job scheduler that accompanies it. The ideas proposed in this chapter are patent pending [10].

Chapter 7 addresses application related variations during the execution. Unstructured or irregular application behavior contributes to the variability in the system. In this section, we propose and evaluate a runtime based function-level optimization approach to do fine-grained optimizations.

Finally, **Chapter 8** summarizes the main contributions and provides a discussion of future research.

# $^{\circ}$

# A Dynamic Runtime Interacting with Data Center's Resource Manager

DOE set a 20 MW power budget for an exascale supercomputer to be built in the next few years [2]. It is anticipated that such a system will face major challenges with reliability, power management, and thermal variations. We believe smart runtime systems have a great potential in overcoming the barriers toward exascale computing.

This chapter gives the high-level design of a unified adaptive runtime system where different modules such as job scheduler, resource manager and the job runtime system interact with each other to optimize for performance and power consumption under user or administrator supplied constrains in an environment with system failures.

Traditionally, the emphasis of HPC data centers and applications has been on performance. However, it is anticipated that future generation supercomputing systems will face major challenges in reliability, power management, thermal variations. Disruptive solutions are required to optimize performance in the presence of these challenges. For each job, a smart parallel runtime system that interacts with the whole machine's resource manager is key to overcome the challenges of next generation supercomputing data centers. In the past, it has been demonstrated that a smart and adaptive runtime system can:

- $\bullet$  improve efficiency in a power-constrained environment [11],

- increase performance with load balancing algorithms [12,13],

Figure 2.1: Figure shows overall system design with two major components interacting with each other: Resource Manager and the Runtime System.

- control the reliability of supercomputers with substantial thermal variations [14],

- configure hardware components to save power [15, 16].

Although these research directions were developed in isolation, they indicate that smart runtime systems have a great potential to overcome barriers towards exascale computing. What the HPC community lacks is an integrated solution that combines past research into a single system that optimizes across multiple dimensions. We propose a comprehensive design in which the data center resource manager dynamically interacts with the individual runtime systems of jobs to optimize performance and power consumption in an environment with system failures under constraints supplied by users or administrators.

At the heart of the proposed solution for power-efficiency, reliability and performance of a HPC data center lies an adaptive and dynamic parallel runtime system. An adaptive runtime system can migrate tasks and data from one processor to any other processor allocated to the job. This ability can solve many challenges that upcoming supercomputers face - application load imbalance across processors, high fault rates, power and energy constraints, and thermal variations. These challenges are often contradictory in terms of their requirements. For example, applying power and temperature constraints can compromise performance and lead to load imbalance across processors. We strive to achieve a healthy balance where we

try to maximize performance in presence of the known as well as contingent constraints and events.

In Figure 2.1, we show a unified diagram of several important components of a data center, their functions and interactions with each other in order to address the challenges of power, reliability and performance. Currently, a data center user is primarily concerned the performance of his or her job. In the future, however, power consumption of their jobs will become a major concern. On the other hand, data center administrators have different and more complex concerns - while they want to guarantee good performance to individual jobs, they need to ensure that the total power consumption of the data center does not exceed its allocated budget and that the job throughput of the data center remains high despite node failures and thermal variations. We achieve the objectives of both the user and the system administrators by allowing dynamic interaction between the system resource manager or scheduler and the job runtime system. While the job scheduler ensures that at any time the system resources are optimally allocated to the jobs based on their power and performance characteristics, the job runtime system implements the decision of the job scheduler by being malleable to shrink or expand itself to the nodes assigned by the scheduler and by doing dynamic load balancing whenever beneficial.

Furthermore, the runtime system can turn on/off or reconfigure various hardware components without impacting application performance, if adequate hardware control is provided by vendors. Our evaluations demonstrate that these runtime capabilities result in greater power efficiency for common HPC applications.

For the rest of this chapter, we first give background information on an adaptive runtime system that serves perfectly for our design needs in Section 2.1. Then, we summarize and demonstrate the past work that fits in the context of dynamic runtime that interacts with data center's resource manager in Sections 2.2, 2.3, 2.4. Finally, in Section 2.5, we discuss the architecture and system needs that are required to enable our design.

#### 2.1 An Adaptive Runtime System for HPC

An adaptive runtime is an essential component of a system optimized for power efficiency, reliability and performance. Adaptive runtime systems enable dynamic collection of performance data, dynamic task migration (load balancing), temperature restraint and power capping with optimal performance.

Charm++ is a C++ based parallel programming framework supported by an adaptive runtime system, which enhances user productivity and allows programs to run portably from small multicore computers (e.g., laptops and phones) to the largest supercomputers [17]. It enables users to easily expose and express much of the parallelism in their algorithms while automating many of the requirements for high performance and scalability. Charm++ has been in production use for over fifteen years and it has thousands of users across a wide variety of computing disciplines with multiple large scale applications including: NAMD for molecular dynamics, ChaNGa for cosmology and OpenAtom for quantum chemistry simulations, and many others [17].

Charm++ has three main attributes: over-decomposition, asynchronous message-driven execution, and migratability. Over-decomposition entails dividing the computation in an application into small work and data units so that there are many more such units than the number of processors. Message-driven execution involves scheduling work units based on when a message is received for them. Migratability refers to the ability to move data and work units between processors. These attributes enable the Charm++ adaptive runtime system to provide many useful features including dynamic load balancing, fault tolerance, and job malleability.

An application written in Charm++ contains a collection of parallel objects that are distributed among processors and communicate via messages. These objects form the basic unit of computation and data that can be assigned and re-assigned to processors. The programmer over-decomposes the problem into many more objects than the number of processors. The Charm++ runtime system handles the assignment of these objects to processors, and it may dynamically migrate objects to balance the load, handle faults, or to shrink-expand the number of processors the application is running on.

Figure 2.2: Illustration of overdecomposition with migratable objects and message driven execution in runtime system.

Charm++ collects information about the application and the system in a distributed database including load of processors, load of each object, communication pattern, and core temperatures. When the number of processors are large, then the centralized data collection becomes a performance bottleneck. Therefore, data collection and decision making are done in a hierarchical fashion. This information is used by different modules of the adaptive runtime to make decisions such as improving load balance, handling faults, and enforcing power constraints.

Load balancing: Charm++ uses a measurement-based mechanism for load balancing. It relies on a heuristic known as the principle of persistence, which states that for over-decomposed iterative applications, the computation load and the communication pattern of tasks or objects tend to persist over time. It uses the load statistics of the application code collected by the runtime system. This has the advantage that it provides an automatic, application independent way of obtaining the load statistics without any input from the user. Using the load statistics, Charm++ executes a chosen load balancing strategy to determine a mapping of objects to processors and then carries out migrations based on this mapping. Charm++ consists of a suite of load balancers including several centralized, distributed and hierarchical strategies. The runtime system can also automate the decision of when to call the load balancer [18]. It can use the instrumented load information to predict the future load

and make load balancing decisions. It automatically triggers load balancing when imbalance is detected and when the benefit of load balancing is more than its overhead.

Fault tolerance: The Charm++ runtime system implements both proactive and reactive strategies for reliability [19]. In the proactive techniques, the runtime system evacuates all objects from a node that a monitoring system predicts is going to crash soon. Since failure prediction is not completely accurate, the reactive techniques recover the information lost after a failure brings down one node of the system. Those latter strategies are mostly based on checkpoint and restart. Therefore, the global application's state is routinely stored and recovery implies retrieving a prior global state.

Shrink-expand: The migratability of Charm++ objects enables a unique ability called *job malleability*; during runtime, a job can shrink (decrease) or expand (increase) the number of nodes it is running on. This feature does not require any additional code from the application developer [20]. Shrink or expand operations can be triggered by an external command or it could be an internal decision made by the runtime. During a shrink operation, the runtime system reduces the number of processors that the application is running on. First, it moves the objects away from the processors that are not going to be used anymore. The unused processors can then be returned back to the resource manager. For an expand operation, the runtime launches new processes on the additional processors that the resource manager has allocated and distributes objects from current processors to the newly allocated processors.

Figure 2.3 shows the internal components and functioning of the Charm++ Runtime System (RTS). There are three important components of the RTS - Local Manager (LM), Load Balancing Module (LBM), and Power Resiliency Module (PRM). Each processor has an LM that is responsible for managing the objects residing on that processor and for interacting with other components of the RTS. The LM of each processor periodically sends its total compute load and compute load of each of its objects to the LBM, and the CPU temperature is sent to the PRM. LBM makes the load balancing decisions using MetaBalancer and it also redistributes load in response to shrink-expand commands from the resource manager. Object migration decisions are communicated to the respective LM by the LBM. PRM, on the other hand, is responsible for ensuring that the CPU temperatures remain below the

Figure 2.3: Various components of adaptive runtime system and their interaction with the resource manager.

job specific temperature threshold. The PRM controls CPU temperature by adjusting the power cap of the CPU. When a processor's temperature is above the threshold, then its power cap is lowered. And when the temperature is well below the desired threshold, then the corresponding power cap is increased while ensuring that the total power of the job remains below the power budget allocated to the job (the determination of this budget is described in the next section). Jobs may not have administrator rights to constrain the power consumption of their CPUs. Therefore, the new power caps are communicated to the resource manager which applies them to each CPU.

### 2.2 Throughput Maximization Under A Power Budget

Recent advances in processor hardware design allow users to control the amount of power consumed by the processor using software with Running Average Power Limit (RAPL) driver [21]. Processors can be power capped to run below their Thermal Design Power (TDP) value, where TDP is the maximum amount of power a processor can consume. The maximum number of nodes in a data center with a power budget is determined by the TDP of the nodes. Power capping makes it possible to control the power consumption of nodes and thus have additional nodes while remaining within the power budget of the data center. This is called an overprovisioned system [22]. Earlier research shows that an increase in the power allocated to a processor does not yield a proportional increase in job's performance [11]. Different jobs react differently to an increase in power allocated to the CPU. The idiosyncrasies in jobs performance based on allocated CPU power, points to the possibility of running different applications at different power levels. Overprovisioned systems can significantly improve performance of applications that are not sensitive to CPU power by capping CPU powers to values below their TDP and adding more nodes to get benefits from strong scaling. The Power Aware Resource Manager (PARM) [11] leverages this capability by optimally distributing the available resources to the jobs - the total power budget of the data center and the compute nodes.

The response of an application to CPU power can be captured by its power-aware speedup. The power-aware speedup is the ratio of the execution time of a job running on a CPU capped at a certain power level compared to the execution time of the same job when running on the lowest allowed power level allowed by the CPU [11]. A higher value for power-aware speedup implies that the application is sensitive to changes in the amount of power allocated to the CPU.

Figure 2.4 shows power-aware speedups of four HPC applications having different characteristics under different CPU power caps [11]. LeanMD, which is a molecular dynamics application has the highest power-aware speedup since it is the most CPU intensive one. Whereas Jacobi2D, which is a stencil application, has the lowest since it is memory intensive. PARM makes scheduling decisions by selecting jobs and their resource configurations

Figure 2.4: Power-aware speedups of four applications running on 20 nodes. The applications vary from being CPU intensive to memory intensive.

(e.g., power budget and compute nodes) such that the total power-aware speedup of running jobs is maximized.

PARM is an essential part of the overall system we propose in this work. It dynamically interacts with the adaptive runtime system of jobs, the system hardware, the user and the system administrator to perform several critical tasks (Figure 2.1). There are three important components of PARM:

- Job Profiler: Before a job is added to the scheduler queue, it is profiled to develop a power-aware strong scaling model that is used to calculate the power aware speedups. This profiling mechanism has negligible overhead as it is sufficient to run the application for a few iterations to get the necessary data points.

- Scheduler: PARM implements its resource allocation optimization strategy as an Integer Linear Program (ILP) with the objective of maximizing power-aware speedup of running jobs under power constraints. Whenever a new job arrives or a running job terminates, PARM's scheduler is triggered, and re-optimizes scheduling and resource allocation decisions. PARM's ILP is fast enough to run frequently with negligible overhead.

Figure 2.5: Comparison of average completion time of jobs with SLURM and PARM, in Rigid(R) and Malleable(M) variants. SetL has jobs that have low sensitivity to CPU power and SetH has jobs that have high sensitivity.

• Execution Framework: This component implements the scheduler decisions by launching jobs, sending shrink or expand decisions to the runtime system of the jobs, and by applying power caps on compute nodes. Job runtime systems interact with the execution framework to convey job termination, completion of shrink or expand operation and any changes to CPU power caps as determined by PRM module of the runtime system.

Figure 2.5 shows the benefits of using PARM as compared to power-unaware SLURM which is an open source resource manager used in many supercomputers. Two versions of PARM are compared - PARM-Rigid and PARM-Malleable. In PARM-Rigid, node allocation decision to any job is rigid, that is it cannot be changed once the job starts running. PARM-Malleable, on the other hand, has an additional degree of freedom that allows it to change the nodes allocated to a running job which is made possible by the shrink and expand feature of Charm++. The number at the top of each bar in Figure 2.5 represents average completion time as a percentage of the average completion time using SLURM scheduler. PARM-Malleable was able to reduce average completion time of jobs by up to 41%.

# 2.3 Improving Reliability Through Temperature Restraint and Load Balancing

Checkpoint and restart is the most popular mechanism to provide fault tolerance in HPC. The total execution time T of an application, on an unreliable system, is given by the equation:

$$T = T_{solve} + T_{checkpoint} + T_{recover} + T_{restart}$$

where  $T_{solve}$  represents the total effort required to solve the problem;  $T_{checkpoint}$  accumulates all the time spent on saving the checkpoints of the system;  $T_{recover}$  stands for the total work that is lost and must be recovered as a result of failures in the system;  $T_{restart}$  is usually constant and represents the amount of time required to resume execution after a crash. A system using checkpoint and restart has to choose an appropriate checkpoint period (denoted by  $\tau$ ). There is a delicate balance in the value of  $\tau$ . A long value of  $\tau$  (low checkpoint frequency) decreases  $T_{checkpoint}$ , but may increase  $T_{recover}$ . Conversely, a short value of  $\tau$  (high checkpoint frequency) means a reduced  $T_{recover}$ , but may enlarge  $T_{checkpoint}$ . The optimum value of  $\tau$  strongly depends on the mean-time-between-failures (MTBF) of the system.

The MTBF of an electronic component is directly affected by its temperature. That relation is usually exponential and there is some experimental evidence that a  $10^{\circ}C$  increase on a processor's temperature decreases its MTBF in half [14]. Therefore, the reliability of a system can be controlled by restraining the temperature of its components. The cooler the system runs, the more reliable it is, but the slower it runs. That is because temperature constraints are realized by restraining the power of the CPU. The runtime allows each core to work at the maximum possible power as long as it is within the maximum temperature threshold. If any of the cores goes above the maximum temperature threshold, then their power is further reduced causing its temperature to fall. However, this can cause a performance degradation for tightly coupled applications due to thermal variations. The LBM will automatically detect any load imbalance and will make the load balancing decisions [12, 13].

The runtime system must strike a balance in the temperature at which each component should be restrained. Moreover, that balance depends on the application. Different codes generate different thermal profiles on the system at different stages of the application. Some codes are more computationally intensive and tend to heat-up the processors more quickly. Appropriate application-based temperature thresholds are stored as part of the Job Profiler in Figure 2.1. In the end, the runtime system aims at reducing the total execution time of an application, considering the MTBF of the system and subject to the power limitations [14].

Figure 2.6: Reduction in execution time and change in MTBF for different temperature thresholds

Figure 2.6 shows percentage reduction in execution time after constraining core temperatures to different thresholds for two different applications. The reduction in execution time shown in Figure 2.6 is calculated compared to the baseline case where processor temperature is not constrained. Figure 2.6 also shows the ratio of MTBF for the machine using our scheme relative to the baseline case where core temperatures are not constrained. For example, by restraining core temperatures to 42°C in case of Jacobi2D, the MTBF for the machine increased 2.3 times while the execution time reduced by 12% compared to the baseline case where core temperatures are not constrained. The inverted U-shape of both of the curves strongly suggests a trade-off between reliability (MTBF) and the slowdown induced by the temperature restraint.

The resource manager sends the PRM of the runtime system (Figure 2.3) the upper bounds of the temperatures that honor the power envelope of the system. Those temperature values

are used as input to an internal resilience component in PRM and they will be changed according to the algorithms that optimize performance and consider the MTBF of the system and the characteristics of the application running. The output will be propagated to further components in PRM that will later consolidate the final power limits and they will be communicated back to the resource manager. A dynamic runtime system is fundamental in controlling the reliability of the system and honoring the power envelope at the same time. Since thermal variations are dynamic, a reactive runtime system efficiently responds to those changes and provides a healthy balance between performance and reliability in the system.

#### 2.4 Dynamic Configuration of System Components

The runtime system can take advantage of the currently available hardware "knobs" for controlling power such as frequency scaling and power capping. However, greater power savings are possible if there is more runtime control over hardware components. We demonstrate, via cycle accurate simulations, that the runtime system can turn-off or reconfigure many components without significant performance penalty based on the properties of the running HPC application.

HPC systems should ideally be energy proportional; the hardware components should consume power and energy only when their functionality is being used. However, network links are always "on", independent of their utilization. In addition, processor caches consume large amounts of power, even when they are not improving the performance of the running application. We propose a runtime system approach that can save this wasted energy by dynamically re-configuring the hardware based on the application needs.

Caches consume up to 40% of a processor's power [15]. A large fraction of cache power consumption can be saved by turning-off some cache banks in cases where the application performance would not be degraded. Many common HPC applications cannot take advantage of the caches effectively. For example, molecular dynamics applications typically have small working data sets and do not need the large last level caches (LLC). On the other hand, grid-based physical simulation applications typically have very large data sets that do not fit in caches and the data reuse in cache is minimal. However, the hardware is not

able to predict the application behavior. Therefore, we propose a runtime system approach where the runtime uses profiling data to reconfigure the cache to save power without significant performance loss. Using a set of representative HPC applications, our previous study demonstrates that on average, 67% of cache energy can be saved with only 2.4% performance penalty [15].

A similar approach applies to HPC networks as well. Networks consume up to 30% of system power even when there is no communication since the links are always on. Our previous study demonstrates that typical HPC applications do not use a large fraction of the links in most of their execution time [16,23]. The reason is that HPC topologies such as Dragonfly are designed to handle the most challenging communication patterns such as all-to-alls in FFT modules. However, typical applications have sparse communication patterns such as nearest neighbor that cannot exploit the massive number of links in HPC networks like Dragonfly. We propose using the runtime system to turn the links on and off adaptively. This hardware configuration case is harder to handle since the usage of network links can be impacted by features such as adaptive routing. Therefore, the runtime system should handle different hardware designs based on their exact specification. Our results demonstrate that up to 80% of the power consumption of network links can be saved using our adaptive runtime strategy [16].

In our unified design, the best hardware configuration is determined by the Job Profiler in Resource Manager (RM) before running each job. Using this information, LM is responsible for applying the configuration. Power models are built using the best configuration as well. As a hypothetical example, RM might know that turning-off half of LLC does not affect performance, but it reduces the maximum power from 70W to 60W. Hence, 60W is used by RM for making scheduling decisions instead of 70W. Tighter incorporation of power-performance trade-offs of hardware configuration in scheduling decisions of the resource manager is the subject of future work.

Table 2.1: Desired access to hardware-level measurement and controls.

$\checkmark$ : There is support and access.  $\checkmark$ : There is no support.

: Hardware has support, but the system's software lacks support or forbids access.

| Platform Need                       | Cori       | Edison     | Cab        | Stampede   |

|-------------------------------------|------------|------------|------------|------------|

| Measurements                        |            |            |            |            |

| Frequency Data                      | ✓          | ✓          | ✓          | ✓          |

| Temperature Data                    | ✓          | ✓          | $\bigcirc$ | $\bigcirc$ |

| Node Level Power Data               | ✓          | ✓          | Ŏ          | $\circ$    |

| Chip Level Power Data               | ✓          | $\bigcirc$ | Ō          | Ō          |

| Core Level Power Data               | X          | X          | X          | X          |

| Controls                            |            |            |            |            |

| Application-level Frequency Scaling | ✓          | ✓          | $\bigcirc$ | $\bigcirc$ |

| Per-chip Frequency Scaling          | $\bigcirc$ | $\bigcirc$ | Ö          | $\circ$    |

| Per-chip Power Capping              | Ō          | Õ          | Ó          | Ó          |

| Per-core Frequency Scaling          | Ō          | X          | X          | X          |

# 2.5 Architecture and System Needs

As supercomputing platforms are becoming more heterogeneous with thousands of processors, forecasts predict challenges in power, energy consumption and process variation in the future. Therefore, it is important that applications, or runtime systems underneath the applications, be aware of the characteristics of the undelying architecture and do necessary optimization to reduce the power, energy consumption and mitigate the effect of performance variations.

Many supercomputing platforms do not give users access to power or temperature measurements or rights to control the frequency of the processors or to apply power-capping algorithms. Access to these measurements and controls would give researchers the opportunity to understand the behavior of the hardware and hence improve power and energy consumption, application performance.

Table 2.1 summarizes the support for the desired user access to hardware-level measurement and controls in four top supercomputing platforms that are used in this dissertation. Cori plaform provides the greatest support among the four platforms. It provides all of the measurement data and as well as application-level frequency control. Such access avail-

able to all end-users without restriction is rare among supercomputing platforms. Edison provides read-access to node-level power and core-level temperature measurements. However, node-level power measurements are not fine-grained enough to make detailed studies – CPU-level power measurements are necessary. Edison also provides control of frequency and power the the level of job allocations, i.e., all nodes participating in a job have the same frequency or power settings for the duration of the job. This also is too coarse-grain. Given the variation we observe among chips, every chip can have a different optimal power and frequency setting. Therefore, dynamic chip level power and frequency control is necessary. Cab and Stampede do not provide access to either power or temperature measurements and do not provide any frequency or power control mechanisms.

Most current power and energy related studies are usually done either in small experimental clusters or using only a few processors. Access to power related controls and measurements on large-scale production supercomputers would enable researchers to extend their studies to much larger platforms, to the benefit of the whole HPC community.

# 2.6 Summary

Important challenges, such as power, reliability, and thermal variations, loom in the future of supercomputing. Addressing these concerns is imperative to harness the next generation of high performance machines. We propose a unified system design with a smart runtime which interacts with the system resource manager.

The combined system offers several important features. First, it honors the power constraints by wisely scheduling jobs and re-allocating their resources when utilization changes. Second, it controls the reliability by a temperature-aware module that cools down the system to an application-based optimal level. Third, it can re-configure the hardware via the runtime without sacrificing performance.

CHAPTER 3

# Analyzing Large Scale Processor Variability

Heterogeneity in supercomputer architectures is often predicted as a characteristic of future exascale machines with non-uniform processors. For example, this could include machines with GPGPUs, FPGAs, or Intel Xeon Phi co-processors. However, even today's architectures with nominally uniform processors are not homogeneous, i.e., there can be performance, power, and thermal variation among them. This variation can be caused by the Complementary Metal-Oxide-Semiconductor (CMOS) manufacturing process of the transistors in a chip, physical layout of each node, differences in node assembly, and data center hot spots.

These variations can manifest themselves as frequency difference among processors under dynamic overclocking. Dynamic overclocking allows the processors to automatically run above their base operating frequency since power, heat, and manufacturing costs prevent processors from constantly running at their maximum validated frequency. The processor can improve performance by opportunistically adjusting its voltage and frequency within its thermal and power constraints. Intel's Turbo Boost Technology is an example of this feature. Overclocking rates are dependent on each processor's power consumption, current draw, thermal limits, number of active cores, and the type of the workload [24].

High performance computing (HPC) applications are often more tightly coupled than server or personal computer workloads. However, HPC systems are mostly built with commercial off-the-shelf processors (with exceptions for special-purpose SoC processors as in the IBM Blue Gene series and moderately custom products for some Intel customers [25]).

Therefore, HPC systems with recent Intel processors come with the same Turbo Boost Technology as systems deployed in other settings, even though it may be less optimized for HPC workloads. Performance heterogeneity among components and performance variation over time can hinder the performance of HPC applications running on supercomputers. Even one slow core in the critical path can slow down the whole application. Therefore heterogeneity in performance is an important concern for HPC users.

In future generation architectures, dynamic features of the processors are expected to increase, and cause their variability to increase as well. Thus, we expect variation to become a pressing challenge in future HPC platforms. Our goal in this work is to measure and to characterize the sources of variation, and to propose solutions to mitigate their effects.

The main contributions of this work include:

- Measurement and analysis of performance variation of up to 16% between processors in top five supercomputing platforms: Cori, Edison, Cab, Stampede, Blue Waters on 1K chips

- Measurement and analysis of frequency, power, and temperature of processors on Cori,

Edison

To the best of our knowledge, there is no other work which measures and analyzes performance, frequency, temperature, and power variation among nominally equal processors under Turbo Boost at large scale (See related work in Section 3.4).

# 3.1 Experimental Setup

#### 3.1.1 Platforms

We have used five different top supercomputing platforms in our experiments. We list the detailed specifications of the platforms in Table 3.1.

Cori is a Cray XC40 supercomputer at NERSC [26]. It contains two types of nodes: with Intel Haswell and with Intel Knights Landing processors. Both processor types have Intel's Turbo Boost version 2.0 feature enabled. For Haswell processors, when all cores are

active, cores can peak up to 2.9 GHz from the nominal frequency of 2.3 GHz. Whereas Knights Landing processors can peak up to only 1.5 GHz from their nominal frequency of 1.4 GHz. Users can specify the frequency of their jobs at launch time with srun --cpu-freq command and specify power cap using srun --power command. The specified configuration is applied to all nodes within the job allocation. If no configuration is specified, processors operate under Turbo Boost.

Edison is a Cray XC30 supercomputer at NERSC [27]. Each compute node has 2 Intel Ivy Bridge processors with Intel's Turbo Boost version 2.0 feature enabled. The actual CPU frequency can peak up to 3.2 GHz if there are 4 or fewer cores active within a chip. When all cores are active, the cores can peak up to 2.8 GHz [28]. The platform gives users the ability to change the nominal frequency and the Linux kernel's power governors. It has 14 fixed frequency states ranging from 1.2 GHz to 2.4 GHz and users can specify the frequency at job launch with the aprun --pstate command. The --p-governor flag sets the power governor.

Edison has 5576 compute nodes. We have used up to 1024 randomly allocated nodes in our experiments. Thus, we believe our results are representative of the whole machine.

Cab is a supercomputer at LLNL [29]. Each computer node has dual Intel Sandy Bridge processors with Intel Turbo Boost version 2.0 enabled. The actual CPU frequency can peak up to 3.3 GHz if there are 1 or 2 cores active within a chip. When all cores are active, the cores can peak up to 3.0 GHz.

Stampede is TACC's supercomputer [30]. Each compute node of Stampede has two Intel Sandy Bridge processors and one Xeon Phi coprocessor. We do not use the coprocessor in our experiments. The processors have Intel Turbo Boost version 2.0 enabled. The actual CPU frequency can peak up to 3.5 GHz if there are 1 or 2 cores active within a chip. When all cores are active, the cores can peak up to 3.1 GHz.

Blue Waters is a Cray XE/XK system at NCSA. For our experiments we use the XE nodes which have two AMD processors with 16 Bulldozer cores [31]. The processors in this system do not have a dynamic overclocking feature like Intel's Turbo Boost.

#### 3.1.2 Applications

#### **Matrix Multiplication**

Dense matrix multiplication is a relatively compute-bound operation that simultaneously stresses a broad subset of a system's hardware. We run the sequential matrix multiplication kernels in a loop on each core with data which fit in the last level cache (L3), i.e., we use three 296x296 double-precision matrices, which requires around 2MB data per core and 24MB per chip where the L3 cache is 30MB on Ivy Bridge cores. Using data which fits in cache eliminates the effect of memory and cache related performance variation in our timings.

MKL-DGEMM: This kernel comes from Intel's Math Kernel Library (Intel MKL) version 13.0.3 on Edison and 13.0.2 on Stampede. Specifically, we call the cblas\_dgemm function. We use this as a representative of a maximally hardware-intensive benchmark.

**NAIVE-DGEMM:** This kernel is a simplistic hand-written 3-loop sequential, double-precision dense matrix multiply. We use this as a representative of application code with typical compiler optimization settings, but that has not been hand-optimized or auto-tuned for maximum performance on a given system architecture.

Data alignment, padding, compiler flags We use 2MB alignment using mkl\_malloc() or posix\_memalign() (respectively) with 0, 64, or 128 bytes of padding for the data buffers to avoid cache aliasing. Preliminary experiments showed that neglecting this effect created substantial performance perturbations. We do not explore that issue both because it has been addressed by substantial previous research and because more realistic applications are much less likely to encounter it as consistently as our micro-benchmark. We use Intel's *icc* compiler (version 15.0.1 on Edison, and 13.0.2 on Stampede) with -O3 and -march=native flags.

#### **LEANMD**

This is a mini-app version of NAMD, a production-level molecular dynamics application for high performance biomolecular simulation systems [32]. It does bonded, short-range, and

long-range force calculations between atoms. In our experiments, we use the benchmark size of around 1.8 million atoms. This benchmark is written in the Charm++ parallel programming framework.

#### JACOBI2D

This is a 5-point stencil application on a 2D grid. The application uses the Charm++ parallel programming framework for parallelization. The grid is divided into multiple small blocks, each represented as an object. For each iteration, the application executes in 3 stages, i.e., local computation, neighbor communication and barrier-based synchronization.

#### 3.1.3 Measurement Methodology