© 2012 by David M. Kunzman. All rights reserved.

## RUNTIME SUPPORT FOR OBJECT-BASED MESSAGE-DRIVEN PARALLEL APPLICATIONS ON HETEROGENEOUS CLUSTERS

ΒY

### DAVID M. KUNZMAN

### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2012

Urbana, Illinois

Doctoral Committee:

Professor Laxmikant V. Kale, Chair Professor William Gropp Associate Professor Craig Zilles Professor David A. Bader, Georgia Institute of Technology

# Abstract

In the last several years, there has been an increased interest in using various accelerator technologies in the realm of high performance computing (HPC). Some of these technologies include the Cell processor (Cell), many integrated cores (MIC), the single chip cloud (SCC), field programmable gate arrays (FPGAs), and graphics processing units (GPUs). Considerable effort has been put forth in harnessing the computing power of these technologies for more general purpose programming. However, making use of these technologies is typically considered hard for various reasons, including their parallel nature and the architecture-specific details involved in programming them.

In this work, we would like to explore (1) how the various pieces of accelerator hardware can be abstracted within a programming model and (2) how an underlying runtime system can assist programmers in making use of accelerators. In other words, how can we make accelerators more accessible to programmers and allow them to focus on the problem at hand, rather than focusing on the hardware itself? What role can/should runtime systems play in making accelerator technologies more accessible to programmers? [[ TODO: Dedication goes here ]]

# Acknowledgments

TODO : Acknowledgments go here

# **Table of Contents**

| List of | f Tables                                              | viii            |

|---------|-------------------------------------------------------|-----------------|

| List of | f Figures                                             | ix              |

| List of | f Abbreviations                                       | xii             |

| Chapte  |                                                       | 1               |

| 1.1     | Send in the Cores                                     | 1               |

| 1.2     | Heterogeneity                                         | 1               |

|         | 1.2.1 Advantages of Heterogeneous Systems             | 3               |

|         | 1.2.2 Challenges of Heterogeneous Systems             | 4               |

| 1.3     | The Scope of This Work                                |                 |

|         | 1.3.1 Considering the Cell Processor                  | 7               |

|         | 1.3.2 Considering GPGPUs                              | 8               |

| 1.4     | Contributions of this Work                            | 9               |

| Chapte  | er 2 Background                                       | 10              |

| 2.1     | The Cell Broadband Engine Architecture (CBEA or Cell) | 10              |

|         | 2.1.1 Architecture                                    | 11              |

|         | 2.1.2 The Offload API                                 | 12              |

| 2.2     | CUDA-Based GPGPUs                                     | 13              |

|         | 2.2.1 Architecture                                    | 14              |

|         | 2.2.2 GPU Manager                                     | 17              |

| 2.3     | Charm++ Basics                                        | 18              |

|         | 2.3.1 Interface Files                                 | 20              |

|         | 2.3.2 Projections                                     | 21              |

| Chapte  | er 3 Approach                                         | 23              |

| 3.1     | Building Upon Charm++                                 |                 |

| 0.1     | 3.1.1 Advantages of Charm++                           | $\frac{20}{25}$ |

|         | 3.1.2 Disadvantages of Charm++                        | $\frac{20}{27}$ |

|         | 3.1.3 Our Work Withing the Larger Charm++ Context     | 28              |

| 3.2     | Programming Model Extensions                          | $\frac{20}{31}$ |

| 0.2     | 3.2.1 Accelerated Entry Methods (AEMs)                | 31              |

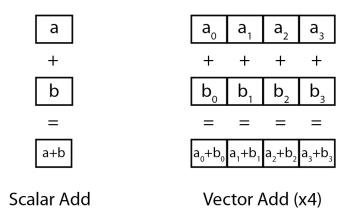

|         | 3.2.2 SIMD Instruction Abstraction (SIMDIA)           | 41              |

| 3.3     | Runtime System Modifications                          | 44              |

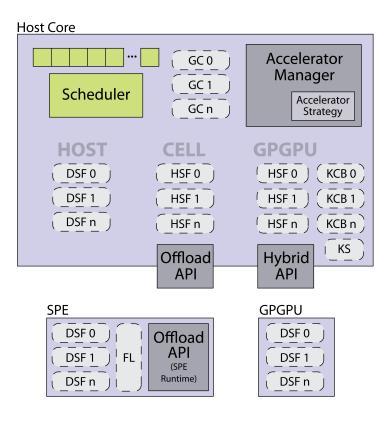

| 0.0     | 3.3.1       Accelerator Manager                       | 44              |

|         | 3.3.2 Architecture-Specific Code Generation           | 49              |

|         |                                                       | <b>ч</b> J      |

| Chapt                                     | er 4 Static Load Balancing 57                                     |

|-------------------------------------------|-------------------------------------------------------------------|

| 4.1                                       | Description of Molecular Dynamics Code                            |

| 4.2                                       | Heterogeneous Cluster Description                                 |

| 4.3                                       | Results                                                           |

|                                           | 4.3.1 Establishing a Performance Baseline                         |

|                                           | 4.3.2 Homogeneous Scaling                                         |

|                                           | 4.3.3 Heterogeneous Scaling                                       |

| 4.4                                       | Static Load Balancing Summary                                     |

| 1.1                                       |                                                                   |

| Chapt                                     | er 5 Dynamic Load Balancing 70                                    |

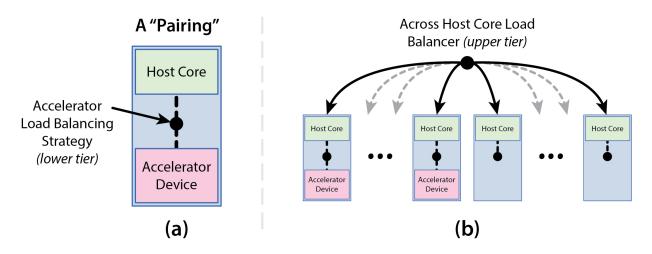

| 5.1                                       | Accelerator Load Balancing Strategies and the Accelerator Manager |

|                                           | 5.1.1 Modeling Workload Balance                                   |

|                                           | 5.1.2 Base Class for Accelerator Load Balancing Strategies        |

|                                           | 5.1.3 List of Accelerator Load Balancing Strategies               |

| 5.2                                       | Across Host Core Load Balancing (AccelEvenLB)                     |

| $5.2 \\ 5.3$                              | Description of Hardware                                           |

| 0.0                                       | 5.3.1 Forge (GPGPU Cluster)                                       |

| 5.4                                       |                                                                   |

| 5.4                                       |                                                                   |

|                                           | 0                                                                 |

|                                           | 5.4.2 Molecular Dynamics                                          |

| 5.5                                       | Adapting to Interference                                          |

|                                           | 5.5.1 Overlapping Execution                                       |

|                                           | 5.5.2 Partial Interference                                        |

| 5.6                                       | Effects of Host Splitting                                         |

| 5.7                                       | Revisiting the Cell Processor                                     |

|                                           | 5.7.1 Sampling (centralized)                                      |

|                                           | 5.7.2 AdjustBusy                                                  |

| 5.8                                       | Summary of Dynamic Load Balancing                                 |

| ~ ~                                       |                                                                   |

| Chapt                                     | 0                                                                 |

| 6.1                                       | Automatic Modification of Data Crossing Processor Boundaries      |

|                                           | 6.1.1 Programmer Impact                                           |

|                                           | 6.1.2 Method                                                      |

| 6.2                                       | Data Within GPGPU Batch Sets                                      |

|                                           | 6.2.1 Data Alignment of Streamed Parameters on GPGPUs             |

|                                           | 6.2.2 Shared Buffers                                              |

| 6.3                                       | Persistent Data                                                   |

|                                           | 6.3.1 Description                                                 |

|                                           | 6.3.2 Application Code Example (5-Point Stencil Modification)     |

|                                           | 6.3.3 Results                                                     |

| 6.4                                       | Integration with Fault Tolerance Support                          |

| 6.5                                       | Summary of Data Management                                        |

| 0.0                                       |                                                                   |

| Chapt                                     | er 7 Related Work                                                 |

| 7.1                                       | Native Programming Models                                         |

| 7.2                                       | Extensions to OpenMP                                              |

| 7.3                                       | Extensions to MPI                                                 |

| 7.4                                       | Other Approaches                                                  |

| $7.4 \\ 7.5$                              | Previous Work Within Charm++                                      |

| 1.0                                       |                                                                   |

| Chapt                                     |                                                                   |

|                                           | er 8 Conclusions                                                  |

|                                           |                                                                   |

| 8.1                                       | Summary of Content                                                |

| $\begin{array}{c} 8.1 \\ 8.2 \end{array}$ | Summary of Content    178      Concluding Remarks    180          |

| 8.1                                       | Summary of Content                                                |

| References | . 186 |

|------------|-------|

|------------|-------|

# List of Tables

| 1.1 | Number of supercomputers including accelerators on the top 10 systems on the Green500 list<br>by year [21] |

|-----|------------------------------------------------------------------------------------------------------------|

|     | Differences between the core types in the cluster                                                          |

| 5.1 | Scaling performance of the simple MD application from one to six nodes on Forge with GPGPU sharing         |

| 8.1 | The top 10 systems on the Green500 list by year [21]                                                       |

# List of Figures

| 2.1<br>2.2<br>2.3 | Architecture overview of the Cell Processor                                                                                                                                              | $     \begin{array}{c}       11 \\       15 \\       22     \end{array} $ |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

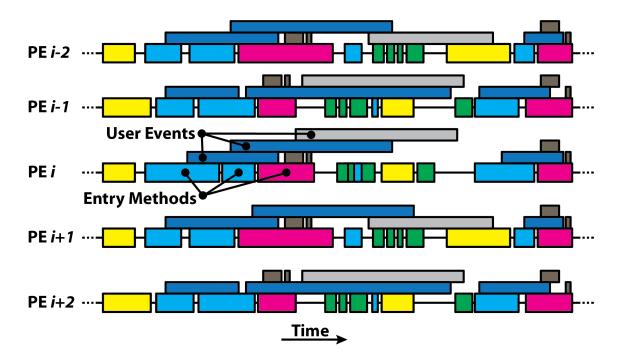

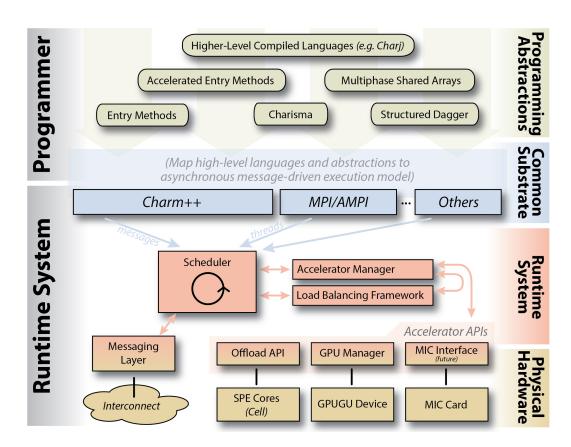

| 2.3               | Overview of the runtime system structure, along with programming abstractions.                                                                                                           | 22<br>29                                                                  |

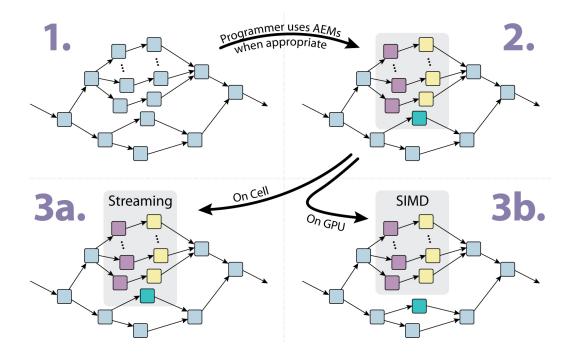

| $3.2 \\ 3.3$      | Structure of an accelerated entry method (AEM)                                                                                                                                           | 31                                                                        |

| 3.4               | Charm++ interface file                                                                                                                                                                   | $\frac{33}{35}$                                                           |

| 3.5               | Example code for a splittable accelerated entry method                                                                                                                                   | 39                                                                        |

| 3.6               | A comparison of a scalar addition to a SIMD addition.                                                                                                                                    | 42                                                                        |

| 3.7               | Example code illustrating the use of SIMDIA                                                                                                                                              | 43                                                                        |

| 3.8               | The two tiers of load balancing for heterogeneous systems that include accelerator devices                                                                                               | 47                                                                        |

| 3.9               | Overview of the generated code created by charmxi.                                                                                                                                       | 50                                                                        |

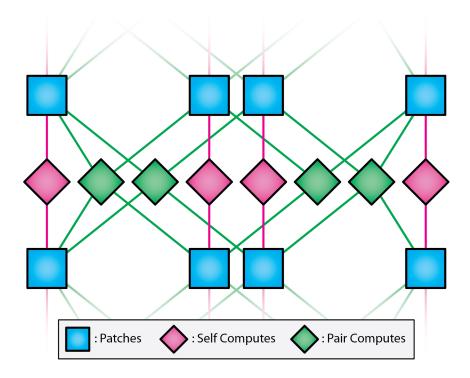

| 4.1               | The interaction of objects, or flow of data between those objects, in a single timestep of the                                                                                           |                                                                           |

|                   | simple MD code.                                                                                                                                                                          | 58                                                                        |

| 4.2               | Integration code from the simple molecular dynamics code.                                                                                                                                | 60                                                                        |

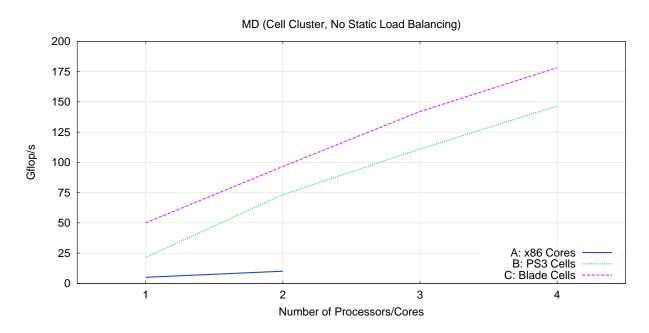

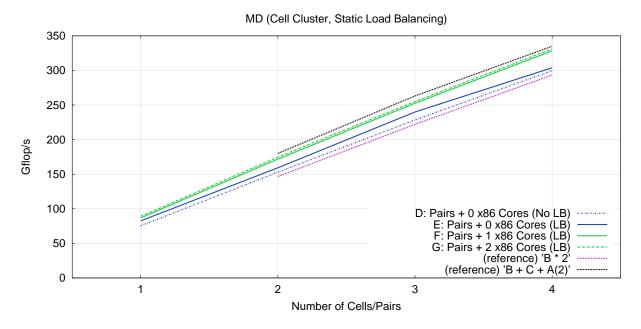

| $4.3 \\ 4.4$      | Performance of the MD application as it is scaled on QS20 Cells, PS3 Cells, and x86 cores<br>Performance of the simple MD application scaled to use all the nodes within a heterogeneous | 64                                                                        |

| 4.4               | cluster, making use of x86-based and Cell-based processors                                                                                                                               | 67                                                                        |

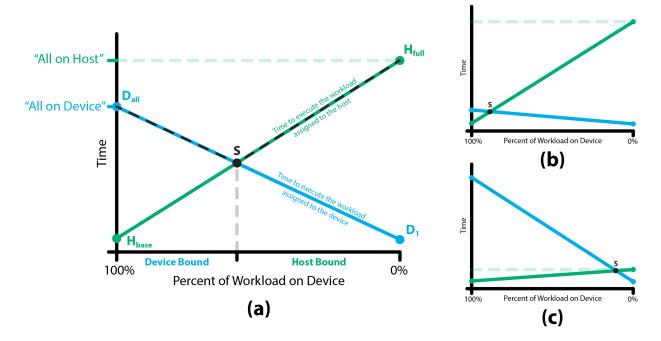

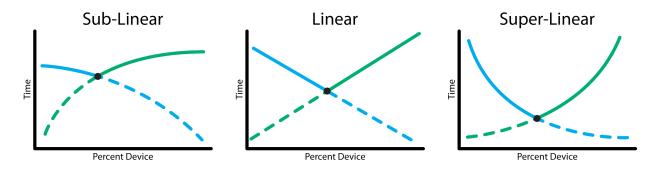

| 5.1               | Balancing a workload across the host and accelerator.                                                                                                                                    | 72                                                                        |

| 5.2               | Balancing a workload across the host and accelerator.                                                                                                                                    | 75                                                                        |

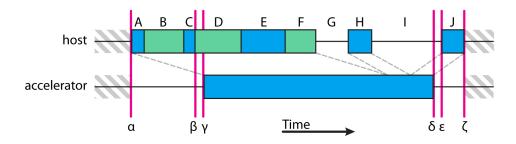

| 5.3               | An example breakdown of one timestep in an arbitrary application                                                                                                                         | 80                                                                        |

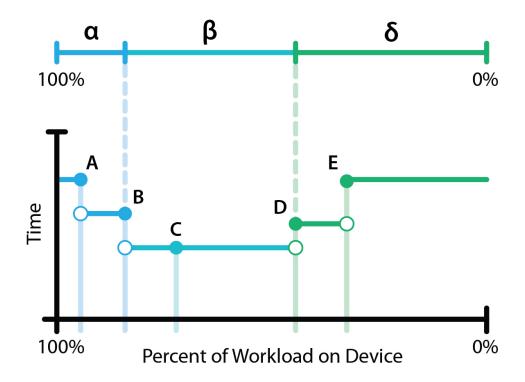

| 5.4               | An example illustrating the construction of the workload balance graph by the Sampling                                                                                                   | 0.4                                                                       |

| 5.5               | accelerator load balancing strategy                                                                                                                                                      | 84<br>98                                                                  |

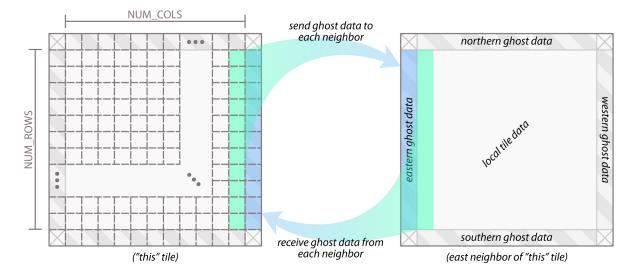

| 5.6               | Interaction of tiles in the 5-point stencil application.                                                                                                                                 | 98                                                                        |

| 5.7               |                                                                                                                                                                                          | 100                                                                       |

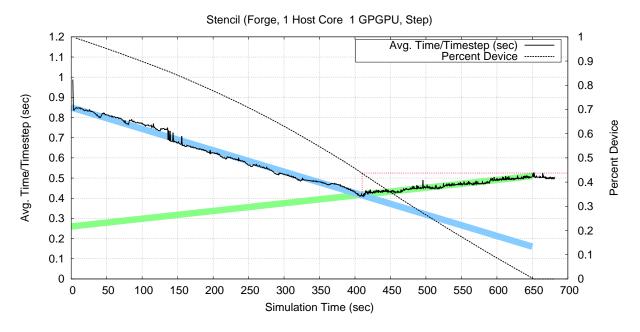

| 5.8               | The 5-Point stencil application executing on a single host core and accelerator device pairing                                                                                           |                                                                           |

|                   | on Forge using the Step accelerator strategy.                                                                                                                                            | 101                                                                       |

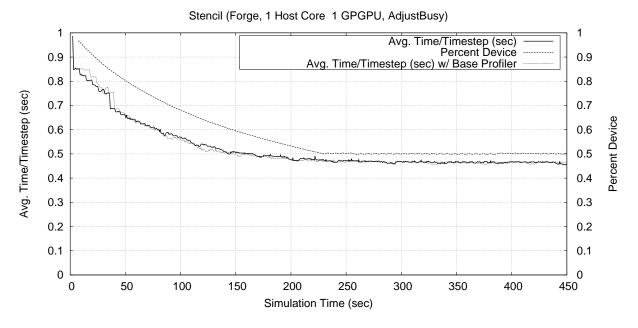

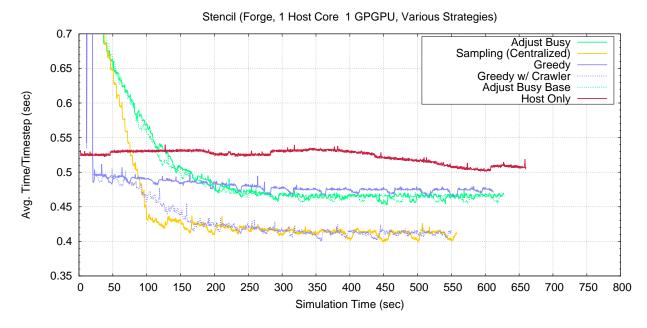

| 5.9               | The 5-Point stencil application executing on a single host core and GPGPU pair on Forge                                                                                                  | 100                                                                       |

| F 10              | using the AdjustBusy strategy                                                                                                                                                            | 102                                                                       |

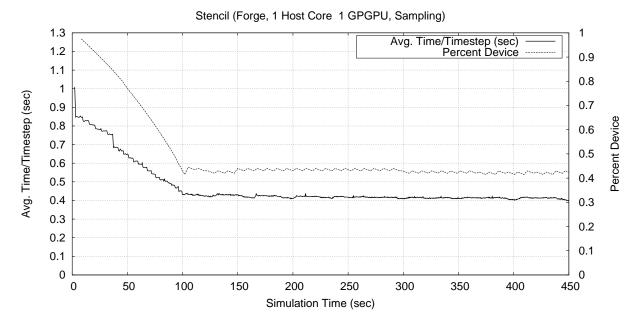

| 5.10              | using the sampling accelerator strategy.                                                                                                                                                 | 103                                                                       |

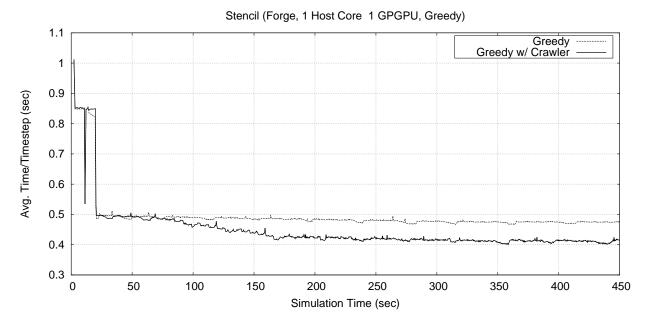

| 5.11              | The 5-Point stencil application executing on a single host core and GPGPU pair on Forge                                                                                                  | 100                                                                       |

|                   | using the Greedy strategy, with and without the Crawler strategy.                                                                                                                        | 104                                                                       |

| 5.12              | The 5-Point stencil application executing on a single host core and GPGPU pair on Forge                                                                                                  |                                                                           |

|                   | using the various accelerator strategies available within the Charm++ runtime system. Note                                                                                               |                                                                           |

|                   | that the vertical axis does not start at zero.                                                                                                                                           | 106                                                                       |

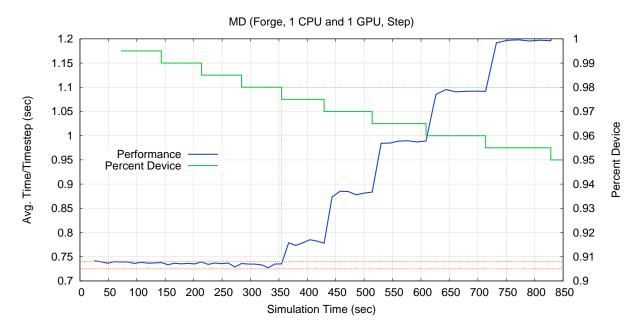

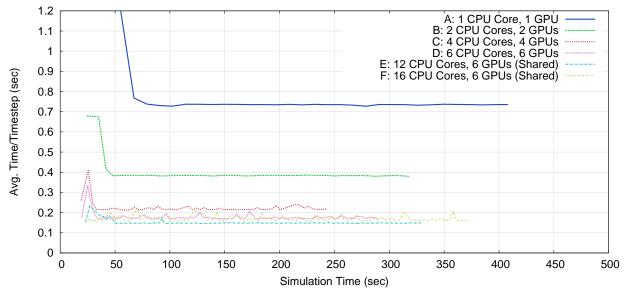

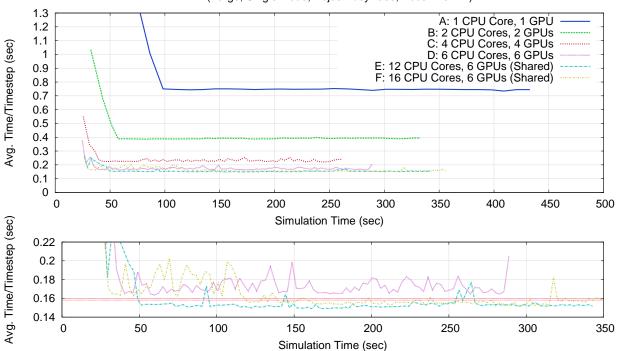

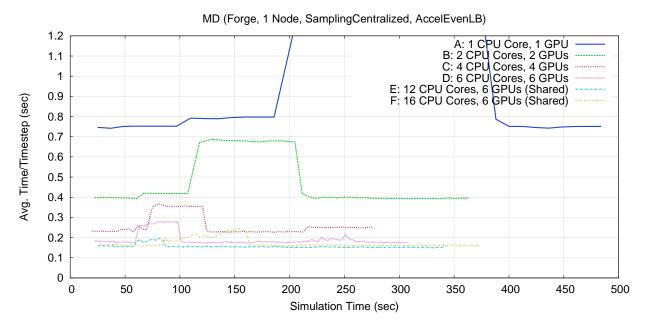

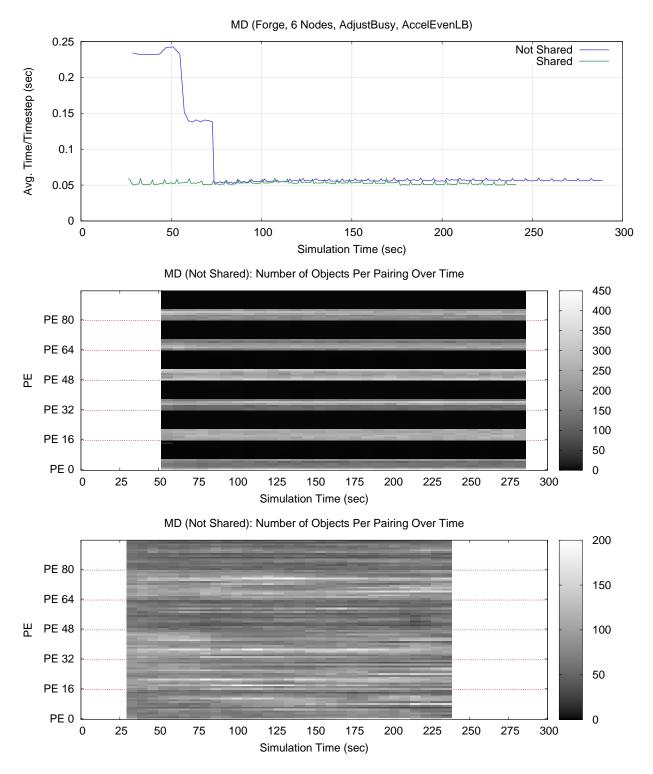

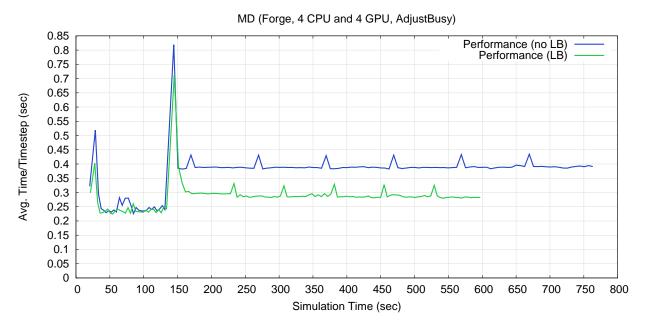

| 5.13        | The molecular dynamics application scaled to a single node of Forge and using the Step accelerator strategy.               | 108   |

|-------------|----------------------------------------------------------------------------------------------------------------------------|-------|

| 5.14        | The molecular dynamics application scaled to a single node of Forge and using the Step                                     |       |

| F 1F        | accelerator strategy                                                                                                       | 110   |

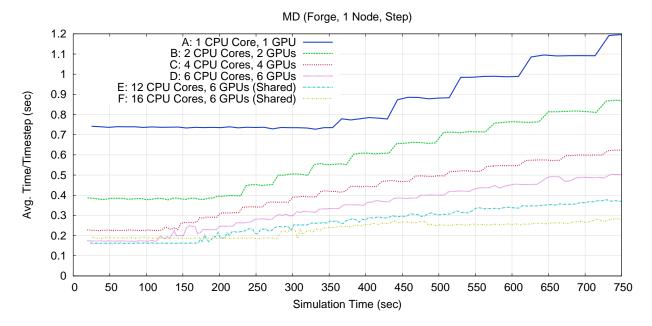

| 9.19        | accelerator strategy.                                                                                                      | 111   |

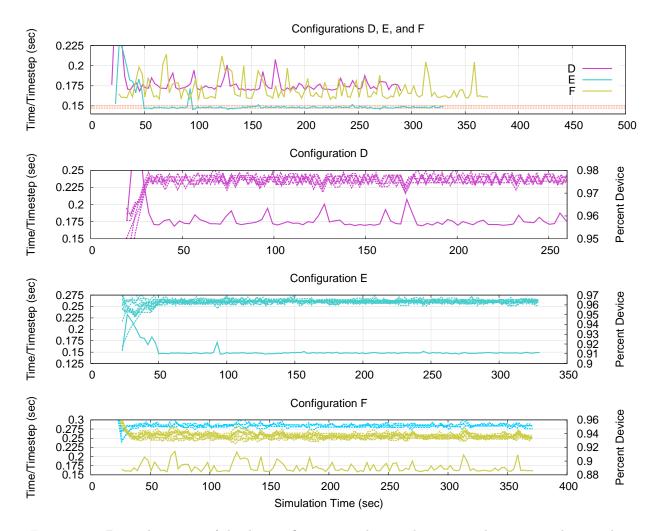

| 5 16        | Zoomed in views of the data in figure 5.15, along with corresponding percent device values.                                |       |

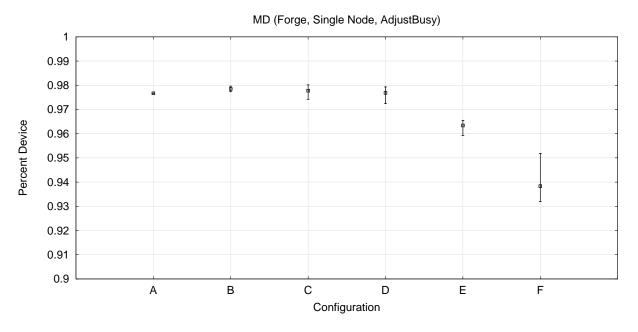

|             | The final percent device values for the various configurations used in figure 5.15                                         |       |

|             | The molecular dynamics application scaled to a single node of Forge and using the AdjustBusy                               | 114   |

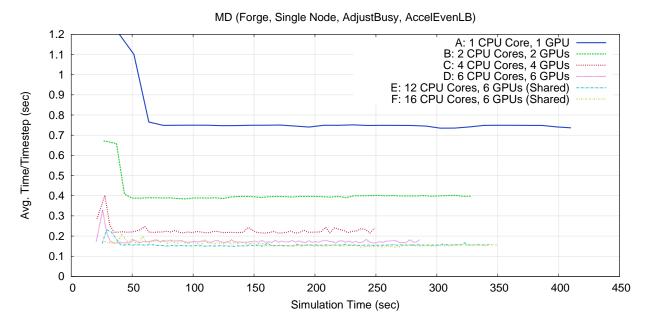

| 0.10        | accelerator strategy along with the AccelEvenLB load balancing strategy.                                                   | 115   |

| 5.19        | The molecular dynamics application scaled to a single node of Forge and using the BaseLoad                                 | 110   |

| 0.10        | profiler, AdjustBusy accelerator strategy, and the AccelEvenLB load balancing strategy                                     | 115   |

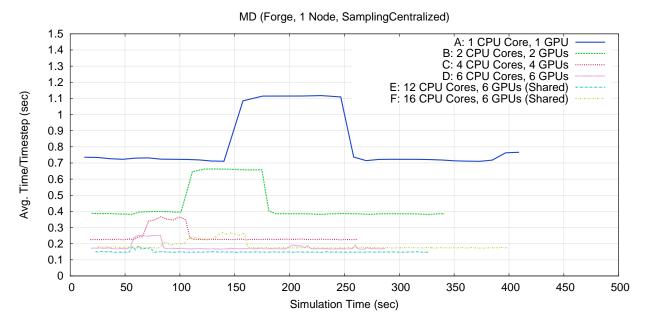

| 5.20        | The molecular dynamics application scaled to a single node of Forge and using the Sampling-                                |       |

|             | Centralized accelerator strategy.                                                                                          | 116   |

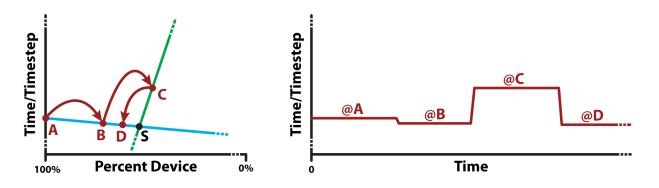

| 5.21        | Illustration explaining the "humps" in figure 5.20.                                                                        |       |

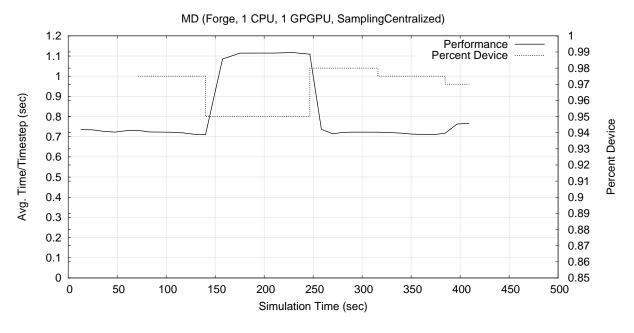

| 5.22        | The molecular dynamics application on a single host core and a single GPGPU using the                                      |       |

|             | Sampling strategy.                                                                                                         | 118   |

| 5.23        | The molecular dynamics application scaled to a single node of Forge and using the Sampling-                                |       |

|             | Centralized accelerator strategy along with the AccelEvenLB load balancing strategy                                        |       |

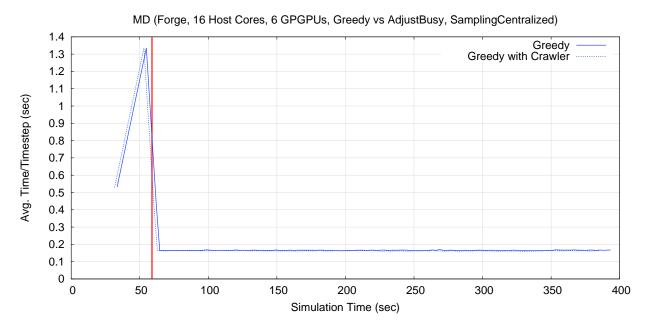

|             | The MD application using the Greedy strategy, with and without the Crawler strategy                                        | 120   |

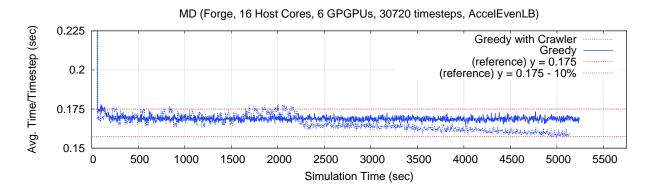

| 5.25        | The MD application executing for 30720 timesteps using the Greedy strategy, with and with-                                 | 101   |

| 5 00        | out the Crawler strategy.                                                                                                  | 121   |

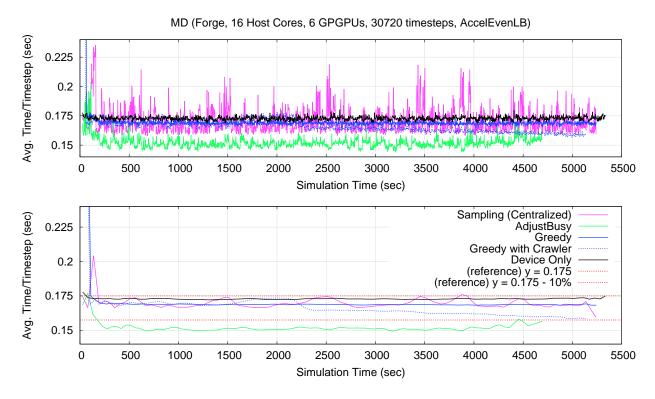

| 5.26        | The MD application executing for 30720 timesteps using a variety of accelerator load balancing                             | 100   |

| E 97        | strategies                                                                                                                 |       |

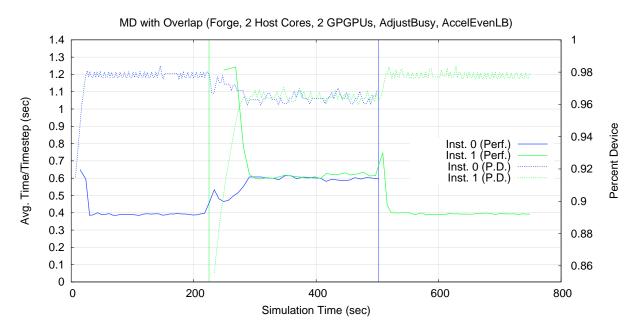

|             | The object distribution and performance of the 6 node execution, with and without GPGPU                                    | 124   |

| 5.20        | sharing.                                                                                                                   | 126   |

| 5.29        | Two instances of the MD application with the same configuration overlapping in time                                        |       |

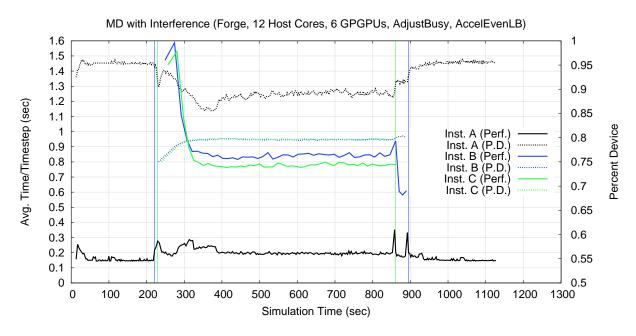

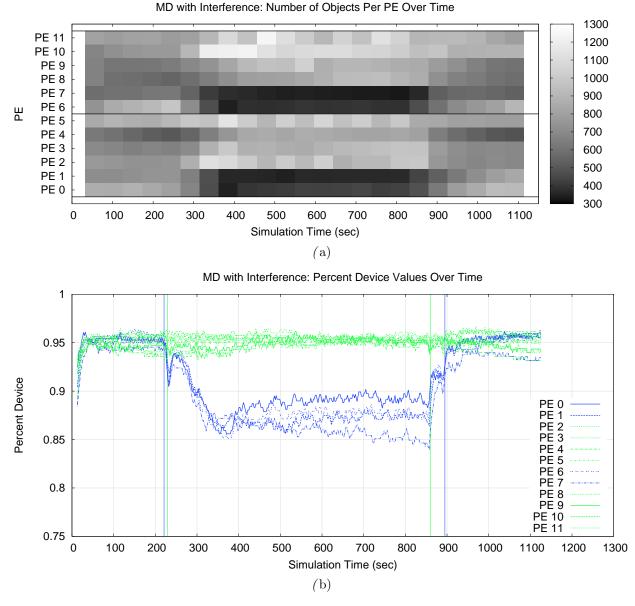

|             | An instance of the MD application executing with interference.                                                             |       |

|             | An instance of the MD application executing with interference.                                                             |       |

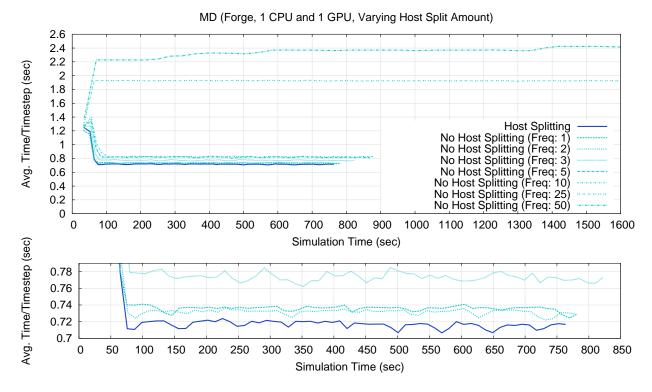

|             | Performance of the MD code using various progress call frequencies, with and without splitting                             |       |

|             | accelerated entry methods on the host core.                                                                                | 135   |

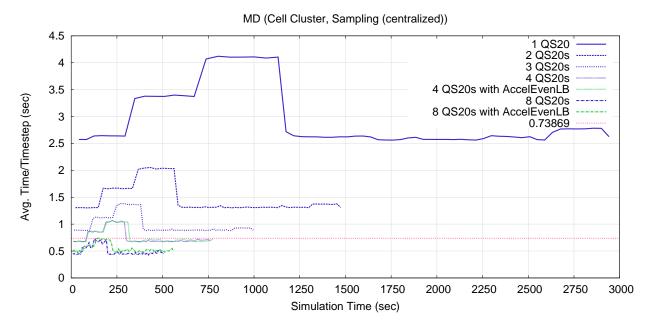

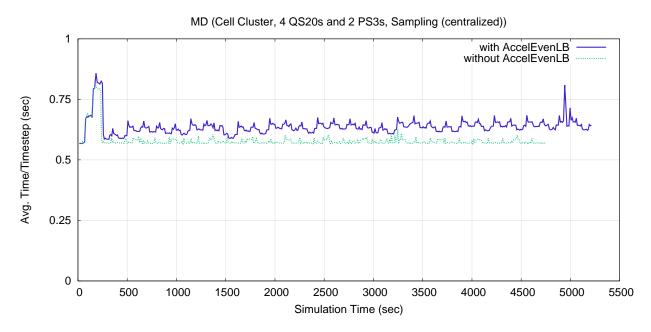

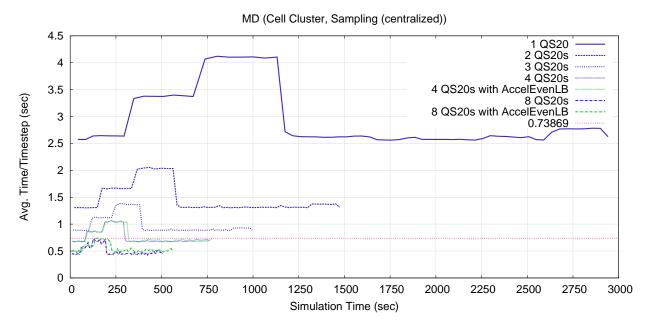

| 5.33        | The MD application executing on QS20 blades in the cell cluster, using the Sampling (cen-                                  |       |

|             | tralized) accelerator load balancing strategy                                                                              | 138   |

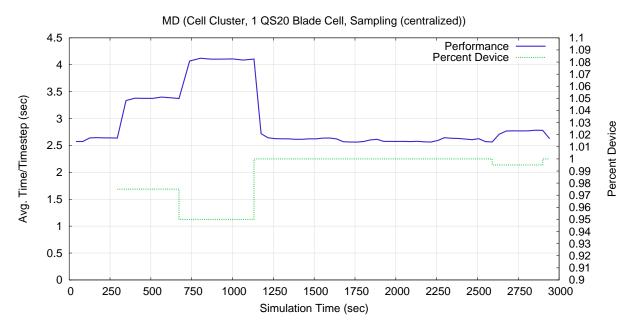

| 5.34        | The MD application executing on 1 QS20 blade in the cell cluster, using the Sampling (cen-                                 |       |

|             | tralized) accelerator load balancing strategy.                                                                             | 139   |

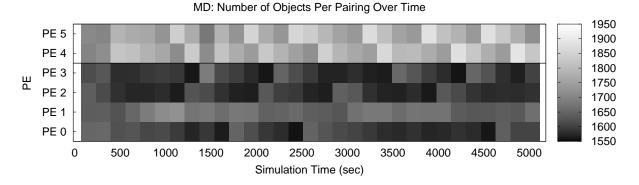

| 5.35        | The MD application executing on 4 QS20 blades and 2 PS3s in the cell cluster, using the                                    |       |

| <b>-</b> 00 | Sampling (centralized) accelerator load balancing strategy.                                                                | 141   |

| 5.36        | The balance of objects as set by AccelEvenLB for the MD application executing on 4 QS20                                    | 1 / 1 |

| 5 97        | blades and 2 PS3s in the cell cluster, using Sampling (centralized)                                                        | 141   |

| 0.57        | The MD application executing on QS20 blades in the cell cluster, using the AdjustBusy accelerator load balancing strategy. | 144   |

|             | accelerator load balancing strategy                                                                                        | 144   |

| 6.1         | Modifications to the send/receive process in a heterogeneous builds of the Charm++ runtime                                 |       |

|             | system.                                                                                                                    | 149   |

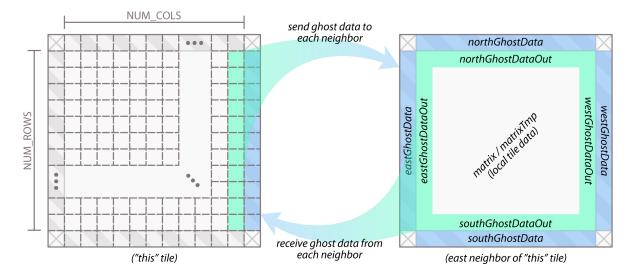

| 6.2         | Example of using shared local parameters (PairCompute from MD code).                                                       | 154   |

| 6.3         | The data patterns of the 5-point stencil application.                                                                      | 157   |

| 6.4         | The calculation accelerated entry method in the 5-point stencil application modified to use                                |       |

|             | persistent buffers                                                                                                         | 159   |

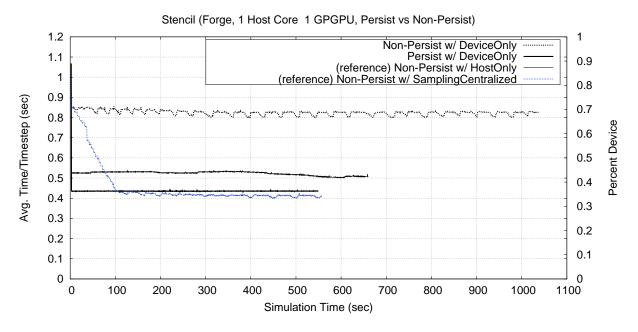

| 6.5         | The 5-point stencil application executing on a single host core and GPGPU pair on Forge,                                   |       |

| 0.0         | with and without the use of the persistent data. $\ldots$                                                                  |       |

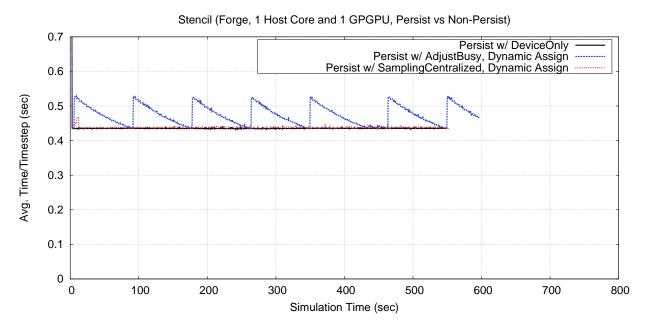

| 6.6         | The 5-point stencil application using persistent buffers and dynamic assignment.                                           |       |

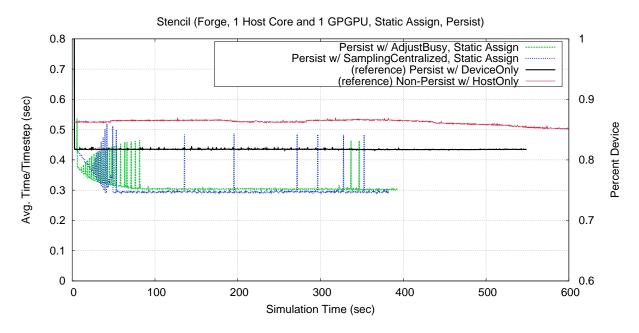

| 6.7         | The 5-point stencil application using persistent buffers and static assignment.                                            | 103   |

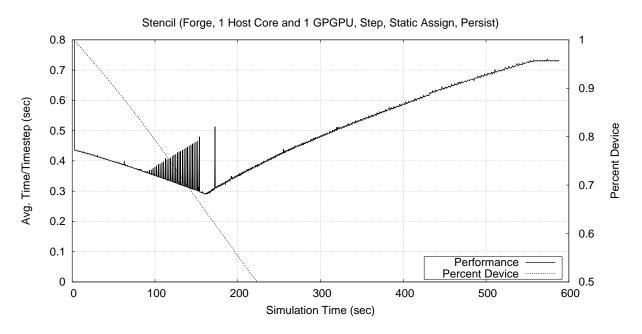

| 6.8  | The 5-point stencil application using persistent buffers, static assignment, and the Step strategy. | 164 |

|------|-----------------------------------------------------------------------------------------------------|-----|

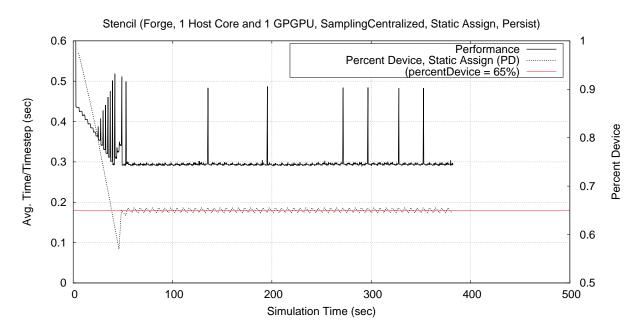

| 6.9  | The 5-point stencil application using persistent buffers, static assignment, and the Sampling       |     |

|      | strategy.                                                                                           | 165 |

| 6.10 | The 5-point stencil application using persistent buffers, static assignment, and the Sampling       |     |

|      | strategy.                                                                                           | 166 |

| 6.11 | Performance of the MD application as it recovers from a host core fault.                            | 167 |

|      |                                                                                                     |     |

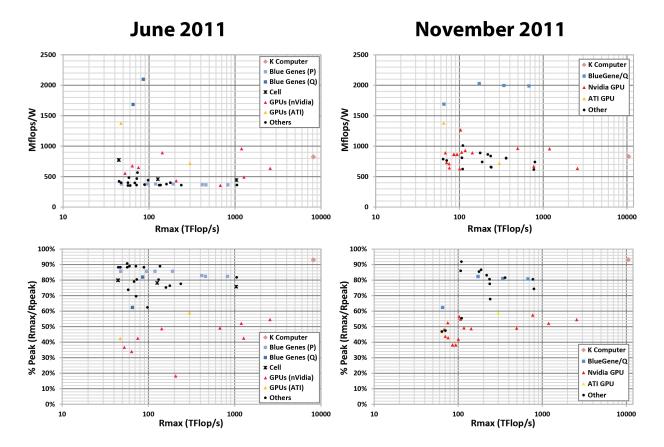

| 8.1  | The top 50 systems from the June 2011 and November 2011 Green500 lists.                             | 184 |

# List of Abbreviations

| accelerator core A core, other than a host core, available to the application |                                                                   |  |  |  |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| accelerator device A set of one or more accelerator cores used collectively   |                                                                   |  |  |  |  |  |

| AccelManager                                                                  | Accelerator Manager                                               |  |  |  |  |  |

| AEM                                                                           | Accelerated Entry Method                                          |  |  |  |  |  |

| Cell                                                                          | The Cell Processor                                                |  |  |  |  |  |

| DMA                                                                           | Direct Memory Access                                              |  |  |  |  |  |

| EM                                                                            | Entry Method                                                      |  |  |  |  |  |

| flop                                                                          | Floating Point Operation                                          |  |  |  |  |  |

| flop/s                                                                        | Floating Point Operations Per Second                              |  |  |  |  |  |

| GPGPU                                                                         | General Purpose Graphics Processing Unit                          |  |  |  |  |  |

| GPU                                                                           | Graphics Processing Unit                                          |  |  |  |  |  |

| host core                                                                     | A core that is executing a complete version of the runtime system |  |  |  |  |  |

| HPC                                                                           | High Performance Computing                                        |  |  |  |  |  |

| Hz                                                                            | Hertz                                                             |  |  |  |  |  |

| ISA                                                                           | Instruction Set Architecture                                      |  |  |  |  |  |

| MD                                                                            | Molecular Dynamics                                                |  |  |  |  |  |

| MIC                                                                           | Many Integrated Core                                              |  |  |  |  |  |

| OS                                                                            | Operating System                                                  |  |  |  |  |  |

| pairing                                                                       | One host core and one accelerator device                          |  |  |  |  |  |

| PCI-E                                                                         | Peripheral Component Interconnect Express (or PCI Express)        |  |  |  |  |  |

| PE                                                                            | Processing Element                                                |  |  |  |  |  |

| PPE                                                                           | Power Processing Element                                          |  |  |  |  |  |

| PS3                                                                           | Playstation 3                                                     |  |  |  |  |  |

| PUP Routines                                                                  | Pack-UnPack Routines                                              |  |  |  |  |  |

| SDK                                                                           | Standard Development Kit                                          |  |  |  |  |  |

|                                                                               |                                                                   |  |  |  |  |  |

- SIMD Single Instruction Multiple Data

- SM Streaming Multiprocessor (in the context of CUDA-based GPGPUs)

- SP Streaming Processor

- SPE Synergistic Processing Element

- SSE Streaming SIMD Extensions

# Chapter 1 Introduction

## 1.1 Send in the Cores

In the not so distant past, each successive generation of a processor saw an increase in clock frequency. This, along with other architectural enhancements, increased the serial performance of single threaded applications running on commodity processors year after year. However, this trend came to a halt as the associated power and cooling requirements became unreasonable. As power and cooling costs placed ceilings on processor frequencies, the number of transistors that can be placed on a die has continued to increase [20]. Historically, the additional transistors available with each generation of processor were typically used to increase the serial performance of individual cores. Over time, this general approach began seeing diminishing returns, with increasingly complicated mechanisms requiring more transistors while providing relatively smaller benefits. Within the last decade, the trend of focusing on the serial performance of a single thread has, to some degree, been reduced. Instead, processor designers have begun using these extra transistors for creating more cores on a single die. This is not to say that single thread performance is no longer important. Rather, there is a recognition that parallelism must be embraced if hardware designs are to continue pushing the performance of processors to higher and higher levels in the face of current power limitations. As a result of this shift, most commodity processors now include multiple cores, with research designs containing (or considering) tens, hundrends, and even thousands of cores [44, 43, 50, 25, 90, 15]. Thus began the multicore era.

### **1.2** Heterogeneity

Moving beyond just the simple duplication of cores to create multicore processors, some specialized hardware designs went a step further by introducing heterogeneity. Specialized hardware designs typically include even more cores than commodity designs, with the individual cores typically being fairly simple in comparison (e.g. in-order pipelines, simple or no branch prediction, etc.). In addition to simply increasing the number of cores, other architecture specific features are usually included within specialized designs, such as direct memory access (DMA) controllers and specialized memories.

Examples of such specialized hardware includes graphics processing units (GPUs) [94], the Cell processor (Cell) [84], many integrated core (MIC) (based on the previous Larrabee design [90]), field programmable gate arrays (FPGAs) [73], single chip cloud (SCC) [26, 22], Intel Sandy Bridge [95], AMD Fusion [31], and others. Throughout this document, we will collectively refer to the specialized components of these processors and/or devices as "accelerators." Naturally, the exploration of these specialized architectures, along with their success in accelerating certain types calculations, has further lead to the exploration of heterogeneous clusters. Several supercomputers built within the last several years have utilized accelerators to augment the computational power of the cluster's host cores, including Roadrunner at Los Alamos National Lab (LANL) [59, 7], Forge at the National Center for Supercomputing Applications (NCSA) [78], HokieSpeed at Virginia Polytechnic Institute [70], Cray XK6 [30], Tianhe-1A at the National Supercomputing Center in Tianjin [47], and the list goes on. In fact, several heterogeneous systems have begun showing up on both the Top500 [76] and the Green500 [21] cluster rankings. In June of 2008, the Roadrunner cluster, which includes Cell processors, was the first supercomputer to achieve a sustained flop rate of greater than one petaflop/s for the LINPACK benchmark [57, 76]. The latest Top500 list (November 2011, at the time of this writing) includes 39 heterogeneous supercomputing clusters, which is more than double the number a year prior (17 clusters in November of 2010) and over five times the number two years prior (7 clusters in November 2009). Of the top 50 systems on the current Top500 list, 8 systems include accelerators. Of the top 50 systems on the current Green500 list, 29 systems include accelerators.

One way in which heterogeneity has been explored is through the inclusion of specialized hardware in an otherwise standard computing node. The most well-known example of this is the use of graphics processing units (GPUs). GPUs were originally introduced as specialized hardware designed specifically to accelerate video and graphics processing. However, as the flop rates of these specialized processors began increasing, programmers writing computationally intensive applications began searching for ways to exploit these specialized processors [88, 71, 18]. Currently, this trend has become more mainstream through the use of programming languages/models designed to target such specialized hardware, such as CUDA [80], OpenCL [40], and OpenACC [82]. Designers of specialized hardware have embraced general purpose computing on specialized hardware, in so far as some hardware mechanisms are being included in the hardware designs that wouldn't otherwise be required by the computations that the specialized hardware was originally intended for, such as IEEE floating-point support within general purpose GPUs (GPGPUs), which is not generally required for graphics.<sup>1</sup>

#### **1.2.1** Advantages of Heterogeneous Systems

Generally speaking, there are two main advantages to using accelerators, and thus heterogeneous systems: flop rates and power usage. First, the peak theoretical flop rates of accelerators are typically higher than the flop rates of standard hardware cores. For example, all of the cores in the Cell processor (which will be described later in section 2.1), regardless of core's type, actually have the same peak flop rate. However, because the specialized cores are smaller, there are more of them per die, and thus provide more flops in aggregate. As such, depending on how one decides to do the flop rate comparison, one could correctly come to either conclusion. For our purposes, we say that the accelerator cores in aggregate provide a higher peak flop rate. The same holds true of CUDA-based GPUs, which have more functional units per streaming multiprocessor (SM), but slower clock speeds. As a result, SMs are more or less comparable to commodity host cores in terms of their peak flop rates. A modern Intel Sandy Bridge host core can perform 16 flops per cycle, for a peak flop rate of 48 Gflop/s with a clock speed of 3.0 GHz [24, 69]. A Fermi SM can execute 64 flops per cycle, for a peak flop rate of 96 Gflop/s with a clock speed of 1.5 GHz (a factor of 2 greater than a host core). However, also note that GPGPU cores place some restrictions on the code making use of them, such as requiring the use of a SIMD execution model, and are not well-suited for all types of calculations. One should be very cautious about making a direct comparison of these fairly different archtectures as it is not a straight forward comparison, especially if one also considers harder to quantify factors such as programmability and portability of the resulting code. That said, once again, the simple GPGPU cores are smaller and designed to be used in large groups, giving them a higher peak flop rate in aggregate. Currently, host processors typically include 4-6 cores, while GPGPUs include 14-16 SMs, creating peak flop rate for GPGPUs that is approximately a factor of 8 greater than host processors (the actual clock speeds and core counts vary between specific processor models).

Second, the flop per Watt ratio is typically lower for accelerators and/or heterogeneous systems when compared to standard commodity cores. At the high-end, we can see this reflected within the top 10 systems listed on the Green500 list over the past several years, as shown in table 1.1. Note that ties are allowed within the Green500 list, allowing more than 10 systems to occupy the top 10 ranks. The Green500 list is released twice annually, once in November (N) and once in June (J). The column headings for table 1.1 indicate the date of the list by month (letter) and year (20xx, where xx represents the number). Table 1.1

<sup>&</sup>lt;sup>1</sup>Please note that some consider the term GPGPU to be a bit of a misnomer, implying that GPGPUs are well-suited for any type of calculation. This is not the case, as GPGPU designs tend to be well-suited to particular types or classes of calculations. Throughout this document, we will use the term GPGPU, with the understanding that GPGPUs may not be well-suited for all types of computation.

|                | N11 | J11 | N10 | J10 | N09 | J09 | N08 | J08 |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Cell           |     | 3   | 3   | 6   | 6   | 4   | 7   | 3   |

| GPGPU (nVidia) | 4   | 2   | 4   | 2   |     |     |     |     |

| GPGPU (ATI)    | 1   | 2   | 1   |     | 1   |     |     |     |

| GRAPE-DR       |     |     | 1   |     | 1   | 1   |     |     |

| Accelerator    | 5   | 7   | 9   | 8   | 8   | 5   | 7   | 3   |

| Total Systems  | 10  | 10  | 11  | 10  | 14  | 13  | 14  | 11  |

Table 1.1: Number of supercomputers including accelerators on the top 10 systems on the Green500 list by year [21].

shows that, for the last four years, clusters that include accelerator technologies make up at least half the top 10 systems each year, with the exception of June 2009 and June 2008. We also point out that of the clusters that do include accelerators, the great majority of those clusters either include Cell processors or GPGPUs.

In smaller systems, the inclusion of accelerators into otherwise standard multicore systems may increase the flop rate to power ratio, allowing applications to perform more work per unit energy. For example, the inclusion of one or more GPGPUs within a workstation can significantly increase the peak flop rate provided by the workstation (as previously pointed out by the peak flop rate comparisons above). The power of a modern Sandy Bridge processor is on the order of 95W ("high-end desktop" version) [95]. As a point of comparison, the power usage of a Fermi-based M2070 Computing Module from NVIDIA is approximately 225W [29]. Note that the power increase is less than the peak flop rate increase. However, again, a direct comparison is not truly fair, since the characteristics of these processors are fairly different and since the power usage of specific models vary. Additionally, there is the question of programmability and how far programmers are required to (or willing to) go in order to achieve a significant portion of the peak flop rates provided by any architecture (i.e. the portion of the peak flop rate that is commonly achieved using standard practices, rather than what many refer to as *heroic efforts*). We will return to this topic in section 8.4.

#### 1.2.2 Challenges of Heterogeneous Systems

In addition to the advantages presented by accelerators and heterogeneous systems, there are also several challenges that come along with using such systems. The clearest challenge of heterogeneous systems is realized by any programmer as they begin to write application code for such systems. Put simply, writing application for a heterogeneous system is often noticeably more difficult when compared to writing application code for a homogeneous system. There are a variety of reasons for this, some of which are more or less true depending on the particular system in question. In the case of the Cell processor, data movement between the general cores and the specialized cores must be done explicitly within the application code itself. Further, the accelerator cores within the Cell processor have specialized scratchpad memories which the programmer must also explicitly manage as data is streamed through the accelerator cores. In the case of GPGPUs, data must often be aggregated explicitly by application code, in addition to explicitly being transfered to and from the accelerator device by the application code. This is required so that the throughput-oriented GPGPUs have a sufficiently large collection of data parallel tasks to execute, as required by their execution models (more on this below). The explicit manipulation of application data required by accelerators is less than ideal for two reasons. First, it decreases the portability of application code by making the code more architecturally specific. Further, the code used to accomplish this explicit data movement commonly needs to be interleaved throughout the application code. This interleaving of architecture specific code throughout the application code not only makes the code less portable by its mere presence, but also complicates any porting effort by making the architecture specific code harder to isolate from the application code. Note that interleaving is as much a requirement for performance reasons, as it is a requirement of the programming models themselves.

Another challenge of accelerators is that accelerators also tend to have a particular execution model tied to the design of the hardware. The Cell processor is designed to be well-suited for stream processing, while GPGPUs are designed to be well-suited for SIMD processing. As a result, it is often the case that the structure of a given application must be manipulated by the programmer manually, at least to some degree, as to reflect the execution model of the given accelerator that the programmer is targeting. The warping of the application model to a more specific hardware model tends further complicate the process of porting an application to another platform for reasons similar to those discussed in the previous paragraph.

## 1.3 The Scope of This Work

Processor and system architects find themselves with an interesting balancing act on their hands. Having more *simpler* cores (i.e. more functional units and thus shifting focus towards overall throughput, rather than solely focusing on serial performance) can make more efficient use of transistor counts and power (i.e. higher Gflop/s and Gflop/s per Watt rates via increasing the overall throughput of the processor, but not necessarily decreasing the latency of any given calculation). On the other hand, serial performance is also quite important for many applications and typically increases with *heavier* cores that devote more transistors to speculation, out-of-order processing, and so on. Specialized hardware can perform certain types of calculations with high levels of performance, but general cores are still required to handle the wide variety of computing tasks that might be encountered. This is particularly true of applications that have many branches, indirect memory accesses, and/or irregular data structures. It's not hard to begin seeing how a mixture of core types may be advantageous for some applications where the overall workload will vary. However, as the variety of cores increases in a given system, the burden on the programmer also grows by complicating the process of writing codes that make use of all the different cores. Examples of complexities that typically arise include architecture differences between the cores, execution model differences, load balancing issues, explicit data movement between the various cores, and the inclusion of architecture specific code throughout the application code (i.e. portability).

Despite their difficulties, with their higher performance to power ratios, it's not unreasonable to think that heterogeneous systems will become more commonplace. As this occurs, we would like to retain ease of programming and portability. If possible, we would also like to have a runtime system handle many aspects of a parallel heterogeneous application for the programmer, leaving the programmer to focus on the problem they wish to solve, rather than the more focused task of implementing a particular algorithm on a particular hardware configuration. In other words, it would be advantageous if we could use a single programming model to program all of the cores, relieving the programmer of the burden of learning multiple programming models, interfacing those models, learning specific details of the hardware, and so on. While we do not believe that all of the difficulties of heterogeneous systems can be masked from programmers, it is the goal of this work to understand some of the ways in which the programming model and runtime system can at least partially ease such burdens on programmers. At the same time, knowing that our abstractions will not solve all of the issues that programmers face when programming heterogeneous systems, we do not want our approach to get in the way of programmers accomplishing what they want to accomplish, even if that means stepping outside the bounds of our abstractions from time to time. For example, as part of our approach we include a SIMD abstraction called SIMDIA (see section 3.2.2) that programmers can use to help make SIMDized code in a more portable manner. However, the functionality of SIMDIA is continually growing and may not be appropriate for all situations (yet or ever). As such, we provide a mechanism for programmers to easily check what supported platform their code is being compiled for and include architecture specific code if required.

Since there is a significant amount of knowledge and work that goes into adding support for a particular type of accelerator into our abstraction, we must necessarily restrict ourselves to only a small subset of the available accelerator technologies in existence today. In particular, we chose to include support for the Cell processor and CUDA-based GPGPUs. The remainder of this document will focus on applying our approach to these accelerators. It should be noted that we have already done some initial exploration for supporting many integrated core (MIC) technologies from Intel within our approach, but current restrictions surrounding this technology stop us from discussing it as part of this document. As such, support for MIC is still considered to be future work at this point in time.

There are two reasons for choosing to support the Cell processor and GPGPUs within our approach. First, both of these accelerator technologies have been used in production clusters and commercial hardware systems, and thus it is fair to say that both of these accelerator technologies have managed to reach mainstream usage at some point in the recent past (last 6 years). Other accelerator technologies, such as FPGAs, still have relatively limited scopes of application in their usage outside of research systems. Note that we are not trying to say that research systems do not have impact, but rather we just want to point out the popularity of the Cell processor and GPGPUs for a variety of applications relative to other technologies. Further, as previously pointed on in section 1.2.1, both Cell processors and GPGPUs have appeared as components in some of the top supercomputers in the world according to both the Top500 and Green500 lists.

A second reason to choose both the Cell processor and CUDA-based GPGPUs as accelerator technologies to support is because they are quite different from one another, as well as being fairly different from commodity host cores. As such, demonstrating that the same programming model extensions and runtime system modifications can be applied to both types of accelerator technologies demonstrates a certain amount of flexibility and generality in our approach. In particular, host cores tend to make use of several (1-32) relatively long-lived threads (i.e. it is common for a thread to exist throughout the entire lifetime of an application's execution when using pthreads [79] or similar models). The Cell processor streams data through a set of on-die, specialized cores with limited amounts of working memory. GPGPUs make use of thousands of very light-weight, short-lived threads in a highly data parallel manner (i.e. a SIMD execution model).

#### 1.3.1 Considering the Cell Processor

The Cell processor has been incorporated into several clusters, including the Condor, Roadrunner, QPACE, Cerrillos, and MariCel clusters. Playstation 3s (PS3s), which also contain Cell processors, have also been used within smaller clusters, since PS3s are less expensive when compared to typical cluster nodes. Despite these successes, the Cell has seen limited adoption relative to other accelerator technologies, most notably GPGPUs. However, we still consider the Cell to be relevant in the study of heterogeneous systems for a few reasons. First, if history is to be a teacher, architectures that more closely resemble commodity hardware tend to be preferred to specialized hardware as long as performance is comparable. Commodity hardware is well understood and requires no architecture specific code to be included within application code. Second, of the popular contemporary accelerator architectures, Cell is unique in that it has scratchpad memories (referred to as "local stores"). That is, the programmer has complete control over (and responsibility for) the memory used by the Synergistic Processing Elements (SPEs), giving the programmer a degree of control over the data's location and movement that is not seen in other accelerator architectures (see section 2.1). Third, Cell represents a case where the host cores are similar to the accelerator cores (i.e. the code execution and performance characteristics of various core types can be reasoned about in a similar manner, though there are important differences). This is unlike GPGPUs, since GPUs are programmed using a different, more-restrictive execution model (i.e. SIMD). The Cell is also unlike GPGPUs in that all the Cell's cores, regardless of type, are on the same die and communicate through an on-die network. Though, recently, we are beginning to see graphics processing units being incorporated on the same die as host cores, including recent processor designs from Intel [96] and AMD [17], removing the need to transfer data off-die and/or requiring separate address spaces be used by the various cores. With these considerations in mind, we believe that exploring various aspects of heterogeneous systems using Cell processors remains an interesting and relevant area of exploration, despite the Cell's recent decline in popularity.

Background information related to the Cell processor will be discussed in section 2.1. The initial application of our approach to the Cell processor using static load balancing will be discussed in chapter 4. Throughout the remainder of this document, the term "accelerator device," when used in reference to Cell processors, will refer to the set of all physical SPE cores available to application code for the particular *version* of the Cell processor being discussed. Note that different versions of the Cell processor have a different number of physical SPE cores. The PPE cores will be referred to as the "host cores." These PPE and SPE cores will be described further in section 2.1.

#### 1.3.2 Considering GPGPUs

Unlike the Cell, which is decreasing in popularity, GPUs are becoming increasingly popular. This is particularly true for programmers writing applications that require high Gflop/s rates, since GPUs currently provide the highest peak flop rates of any accelerator technology. As we have already mentioned, this added performance comes at the cost of being highly specialized. In particular, GPGPUs target calculations that exhibit a high degree of data parallelism. This is a result of being originally designed to handle heavy graphic workloads, which are themselves highly data parallel in nature. While the architecture of the Cell processor is closer to commodity processors, the higher peak performance offered by GPUs is enticing and should not be ignored. With both the opportunities and challenges in mind, we include GPGPUs as one of the target platforms for our work. Background information about GPGPUs will be covered in section 2.2. Chapters 5 and 6 will cover some of our more recent efforts involving GPGPUs.

# 1.4 Contributions of this Work

In this work, we will demonstrate the use of a message-driven object-oriented programming model on various hardware architectures, including host cores, Cell processors, and CUDA-based GPGPUs. In particular, the Charm++ programming model will be extended to include *accelerated entry methods* (see section 3.2.1) and SIMDIA (see section 3.2.2). The intent of including these extensions within Charm++ is to create a *unified programming model* in which a programmer can express their application code using a single programming model, regardless of the hardware used to execute the application, and thus provide portability. Further, we wish to explore the use of a message-driven (i.e. similar to event-driven) programming model to program both Cell processors and GPGPUs. For GPGPUs in particular, one does not typically think of using non-data-parallel programming models to express application code that targets accelerators.

By taking advantage of the portability provided by a unified programming model, we also plan to explore various ways in which an active, adaptive, and intelligent runtime system can assist the application, and thus the programmer. By performing a variety of tasks automatically (or perhaps with some minimal guidance), the runtime system can actively perform various tasks that a programmer would otherwise be responsible for supporting explicitly within the application code. A runtime system can help address a variety of concerns shared by a wide variety of applications, ranging from high-level tasks such as dynamic load balancing and fault tolerance support, through very detail-oriented and tedious tasks such as endian correction. The two main areas of focus related to runtime system support will revolve around load balancing (see chapters 4 and 5) and data management (see chapter 6).

# Chapter 2 Background

This chapter will review background material that will help the reader better understand the following chapters. There are three main topics that will be covered. First, an overview of the Cell Broadband Engine Architecture (CBEA, or simply "Cell") will be given. The Cell architecture is one of the target architectures that this work targets. Second, an overview of CUDA-based general purpose graphics processing units (GPGPUs) will be given. These GPGPU devices are also a target of our work. Third, an introduction to the Charm++ programming model will be given. This work builds upon the Charm++ programming model and runtime system, so an understanding of how Charm++ operates is important in understanding how our approach operates.

# 2.1 The Cell Broadband Engine Architecture (CBEA or Cell)

The Cell Broadband Engine Architecture (CBEA), commonly referred to simply as *Cell*, was jointly developed by IBM, Toshiba, and Sony [51]. The architecture was popularized with the inclusion of the Cell processor in Sony's Playstation 3 (PS3), but has also been included in other products, including the QS20 and QS22 blade servers from IBM, along with the SpursEngine from Toshiba. IBM designed a supercomputer cluster which included Cell Processors, named Roadrunner, which is located at Los Alamos National Laboratory (LANL). In June of 2008, the Roadrunner cluster topped the Top500 list and was the first supercomputer to achieve a sustained rate of 1 Pflop/s while executing the Linpack benchmark. Based on the Green500 list from the same month, the top 3 systems, in terms of their flop rate per Watt, were also Cell-based systems, providing further support for the idea that heterogeneous systems are one possible avenue for creating power-efficient, large-scale computing systems.<sup>1</sup>

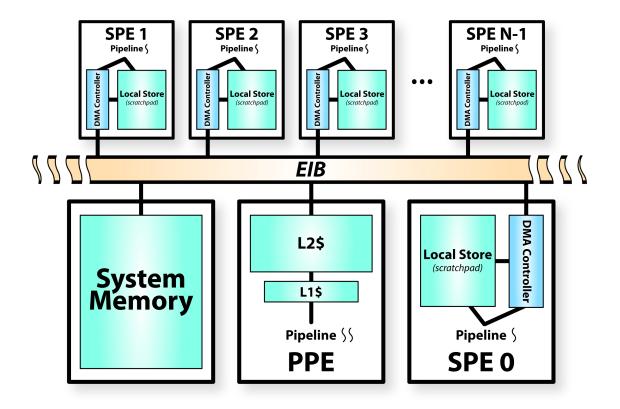

Figure 2.1: Architecture overview of the Cell Processor.

#### 2.1.1 Architecture

The CBEA defines two types of processing cores, the Power Processing Element (PPE) and the Synergistic Processing Element (SPE) [51, 41]. Please refer to figure 2.1 for an overview of the Cell architecture. Note that figure 2.1 does not include all components of the Cell processors, just the components related to this work. Both types of cores are located within a single processor, though in different ratios depending on the particular processor in question.

Generally speaking, the PPE can be thought of as a standard core similar to those included in many commodity multicore processors. In particular, the PPE has direct access to system memory via load/store instructions and full support for virtual memory. The system memory is accessed through a cache hierarchy, similar to other commodity processors.

Unlike the PPEs, the SPEs are specialized cores. In particular, the SPEs are designed to execute computationally intensive code. Typical hardware implementations of the CBEA include several SPEs per PPE. For example, the Cell processors in the IBM blade systems include 1 PPE and 8 SPEs [27], the Sony Playstation 3 includes 1 PPE and 7 SPEs (though, one is dedicated to the OS, so it is effectively 6 SPEs for

$<sup>^{1} \</sup>rm http://www.green500.org/lists/2008/06/top/list.php$

application code) [65, 19], and the SpursEngine includes 1 PPE and 4 SPEs [42].

While the SPEs resemble typical multicore processor cores in many ways, there are several important differences that are worth noting. First, SPEs do not have direct access to system memory. Instead, each SPE has a dedicated scratchpad memory, called the *local store*, which is accessed via load/store instructions issued by the SPE's pipeline. Local stores are 256KB in size and must contain all data required by the SPE, including the application code, the stack, and the heap. The programmer has complete control over the local store (e.g. dereferencing NULL (0x00) is a valid operation on an SPE). Second, each SPE also has a direct memory access (DMA) engine that is used to move data back and forth between system memory and the SPE's local store. The DMA transactions are issued directly by the application code, leaving the programmer to explicitly interleave DMA related code throughout their application. Well established techniques, such as tiling, code overlays, and streaming, can make use of the DMA engine to overcome the challenge of having such a small amount of physical memory per SPE. However, the task of implementing such techniques is left to the programmer and/or library developers. Third, the ISA of the SPEs is not identical to the PPE. As such, code that is compiled for the PPE will not execute on the SPE, and vice versa. Instead, the SPE code is compiled separately and then *embedded* into the PPE executable. Using functions provided in the Cell SDK, the programmer can then transfer the embedded SPE executable down to an SPE's local store and initiate the execution of that executable on the given SPE. Fourth, the different ISAs also result in different SIMD extensions provided by each core. While having different ISAs has only a limited effect on the programmer when compiling the C/C++ code for either the PPE or the SPE, the different SIMD extensions require different intrinsics to be used by the programmer, depending on which core they are targeting. Further, the types of instructions supported by each SIMD extension are not identical [51].

Each of the cores, regardless of type, are connected to one another via an on-chip network called the Element Interconnect Bus (EIB). Other components, including memory controllers and I/O components, are also connected to the cores via the EIB. The EIB is a bi-directional ring network, with a peak bandwidth of 204.8 Gbytes/s [58].

#### 2.1.2 The Offload API

As part of this work, we developed the Offload API to help ease the burden of programming the Cell Processor [61, 62]. The basic idea behind the Offload API is to allow the programmer to stream *work requests* (think *chunks of work*) to the SPEs. In particular, there should be several active work requests per SPE at any given moment. This allows the SPE runtime to overlap the computation of a ready-to-execute work request with the data transfers of other work requests moving data into and out of the same SPE. This overlap of

computation with data transfers helps to hide the latency of the data transfers themselves.

To make use of the Offload API, the programmer provides a set of offloaded functions, each of which takes a programmer-specified number of input and output data buffers (i.e. each buffer can be specified as input and/or output). These functions define the calculations that are available for offloading, from the point-of-view of the PPE. The programmer explicitly creates work requests on the PPE by filling in an associated data structure. Each work request is associated with one of these functions and a number of data buffers, as required by the specific offloaded function. Once the work request is finished being created (code and data specified), the work request is issued to the Offload API. Eventually, at some point in the future, the work request will complete and a programmer specified callback function is called on the PPE to notify the application that any output data that was generated by the work request is ready. The application code can take further actions, such as sending messages, from within the callback function.

As application code issues work requests to the Offload API, the work requests are distributed evenly across the SPEs. Once assigned to a specific SPE, the data associated with a given work request is transferred to the SPE's local store by the SPE's DMA engine. Once all of the data has been transferred to the SPE, the work request is queued for execution. After execution, the output data is transferred back to system memory. Once the output data has been copied to system memory (i.e. is available to the PPE) the Offload API calls the programmer specified callback function. Except for issuing the work request, which occurs directly from within an entry method, and the execution of the callback function, which occurs in-between entry method executions, all of the operations associated with a work request are asynchronous to the application code executing on the PPE (host core). Note, that the explicit use of the Offload API is only required if a Charm++ application *does not* make use of the programming model extensions discussed in chapter 3.

### 2.2 CUDA-Based GPGPUs

Graphic processing units (GPUs) were originally designed to handle the large amount of number crunching associated with real-time graphics for computer games and other graphic intensive applications. However, as the technologies associated with GPUs have matured over time, they have also been extended into more general purpose computations (i.e. not just graphics). This is where the term general purpose GPU (GPGPU) originated from. Some consider this term to be a bit of a misnomer, since it suggests that GPUs are appropriate for all types of computing tasks. In reality though, GPGPUs work very well at accelerating some types of computations (i.e. computations with very regular data structures, regular memory access patterns, and that are highly data parallel in nature) and are not particularly well-suited for others (i.e. computations with irregular data structures, irregular or indirect memory access patterns, or are not particularly data parallel in nature).

In this work, we will focus on CUDA-based GPGPUs in particular. In using the phrase "CUDA-based GPGPUs," we simply mean a GPGPU that can be programmed using the CUDA programming model [80]. There is no technical reason that these particular types of GPGPUs were chosen over any other. The decision mainly stems from existing infrastructure related to CUDA within Charm++ (i.e. the GPU Manager, previously known as the Hybrid API, as described in section 2.2.2) [93, 55], mixed with the limited time and resources to build the required infrastructure for several types of GPGPUs by the time of this writing. In other words, CUDA-based GPGPUs are simply the first type of GPGPUs supported within the context of our work, but are not the only type that could be supported.

#### 2.2.1 Architecture

CUDA-based GPGPUs are fairly different from conventional host processors. Most notably, there are many more hardware threads available to the programmer, and subsets of those threads are executed in a single instruction multiple data (SIMD) manner. Before describing how the threads operate relative to one another, we first give the reader an overview of the architecture itself. In particular, we will be describing the Fermi architecture/generation of CUDA-based GPGPUs since these are the type of GPGPUs that we will using in later chapters for conducting experiments [28].

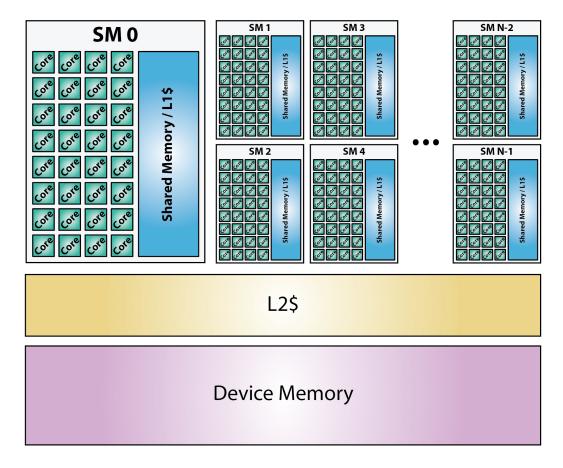

Figure 2.2 gives an overview of CUDA-based GPGPUs based on the Fermi architecture. Note that the Fermi architecture actually has more components than shown in figure 2.2. However, figure 2.2 covers the portions of the architecture that are relevant to our work. Overall, there are many relatively small cores, each of which is capable of executing a single hardware thread. These cores are grouped together into sets of 32 cores which, along with additional resources, are collectively referred to as a streaming multiprocessor (SM). Each SM has a set of resources that are shared/divided amongst the various threads that are executing on the SMs, depending on the exact resource in question. 32 software threads are grouped together into sets called *warps*, with several warps being resident on an SM at any given moment. The exact number of warps an SM can contain depends on the amount of resources that warp requires. Since the resources of an SM are fixed (defined by the particular hardware implementation), the more resources each warp requires, such as registers, shared memory, and so on, the fewer the number of warps that will be able to fit on a given SM at the same time. The threads within the warp are executed using a single instruction multiple data (SIMD) execution model. That is, all of the threads within the warp share the same instruction stream, and the threads within a given warp execute in lockstep with one another. Branches within the

Figure 2.2: Architecture overview of a CUDA-based GPGPU.

instruction stream are handled by causing a subset of the threads to become inactive (think, "executing the instructions, but not committing the results of those instructions" or predication) during the portions of the instruction stream that a particular thread does not need to execute. For example, if at least one thread needs to execute the true block associated with an *if* statement, then all of the threads within the block will executed the true block. The threads that did not evaluate the *if* statement's condition to be true will be marked as inactive during the duration of the *if* statement's true block. In situations where some threads are active and some are inactive, the threads are referred to as being divergent. Threads within a warp being divergent is problematic since it causes hardware cores associated with inactive threads to go unused (i.e. not performing useful work from the point-of-view of the application) as long as those threads remain inactive. This SIMD execution model is a result of the hardware design of GPGPUs. Any application executing code on a GPGPU (of this nature) must adhere to this execution model. The accelerator device as a whole, is made up of several SMs, with current high-end models containing on the order of 16 SMs per device. Across the various generations of hardware, the number of cores has been varied, along with the number of SMs per GPGPU.

Another characteristic of GPGPU hardware is that the threads from one warp can be swapped with the threads in another resident warp within a single cycle. This allows for the instruction latencies experienced within one warp to be overlapped with the execution of instructions from another warp. The overall effect of this fast context switch is that the function units within the cores remain busy for a larger number of cycles (assuming multiple warps per SM). What would otherwise be gaps or bubbles in a core's pipeline cause by data dependencies between instructions from one warp's instruction stream are filled in by instructions from another warp's instruction stream, allowing the application to reach a higher percentage of the accelerator device's peak flop rate that it would otherwise be able to achieve if only a single warp were active per SM. To take advantage of this hardware characteristic, the application typically needs to decrease the granularity of the work associated with each hardware thread, along with keeping the amount of resources required per thread at a minimum, so that the number of warps per SM is maximized (the number of warps per SM is referred to as occupancy). The greater the number of warps per SM, the greater the chance that at least one warp is not stalled on a data dependency, and thus, the greater the chance that an instruction can be issued from one of the warps in the current cycle (i.e. the functional units are kept busy).

However, the SIMD execution model, the fine granularity of the threads, and the separate address space (i.e. device memory) presents extra burden on the programmer. The separate address space is likely a burden that may (or may not, depending on the model of GPGPU being used) be an issue. Some modern processor designs are beginning to include the host processor and the GPGPU cores on a single die, giving both direct access to and a coherent view of system memory (i.e. the same address space). The other two issues, SIMD execution model and thread granularity, in the most general sense, tend to force programmers to create two versions of their code, one version for the host cores and one version for the accelerator device. Otherwise, the programmer's code is not portable between various platforms. There are, of course, ways around this through the use of various third party libraries and/or the use of programming models designed to abstract these hardware differences away from the application code. Our approach will be discussed in chapter 3.

This description of GPGPU architecture is only intended to provide the reader with a high-level overview of the architecture. There are many resources from a variety of sources providing information related to GPGPUs [80, 28, 94].

#### 2.2.2 GPU Manager

The GPU Manager [93, 55, 49] serves a purpose similar to the purpose the Offload API serves for the Cell processors, which is to allow programmers to easily offload pieces of work to the accelerator device. Like the Offload API, the programmer creates work requests. There is a one-to-one correspondence between work requests and CUDA kernel invocations, which means the granularity of a work request is much greater for the GPU Manager compared to work requests within the Offload API.

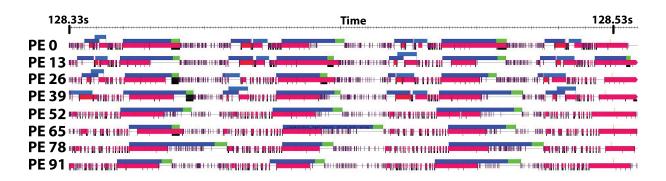

The programmer is responsible for writing the actual CUDA kernels. As a result, the code needs to be duplicated by the programmer if using the GPU Manager directly, one copy for the host core and one copy for the GPGPU. In addition to the kernel functions, the programmer also has to write a *kernel select* function. The kernel select function is called on the host core by the GPU Manager as input data for a given work request becomes ready for use on the device. The kernel select function does the work of invoking the kernel's execution on the GPGPU device.