### TECHNIQUES IN SCALABLE AND EFFECTIVE PARALLEL PERFORMANCE ANALYSIS

BY

CHEE WAI LEE

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2009

Urbana, Illinois

**Doctoral Committee:**

Professor Laxmikant Kale, Chair Professor Marc Snir Professor Michael Heath Doctor Luiz DeRose, Cray Inc.

### Abstract

Performance analysis tools are essential to the maintenance of efficient parallel execution of scientific applications. As scientific applications are executed on larger and larger parallel supercomputers, it is clear that performance tools must employ more advanced techniques to keep up with the increasing data volume and complexity of the performance information generated by these applications as a result of scaling.

In this thesis, we investigate the useful techniques in four main thrusts to address various aspects of this problem. First, we study how some traditional performance analysis idioms can break down in the face of data from large processor counts and demonstrate techniques and tools that restore scalability. Second, we investigate how the volume of performance data generated can be reduced while keeping the captured information relevant for analysis and performance problem detection. Third, we investigate the powerful new performance analysis idioms enabled by live access to performance information streams from a running parallel application. Fourth, we demonstrate how repeated performance hypothesis testing can be conducted, via simulation techniques, scalably and with significantly reduced resource consumption. In addition, we explore the benefits of performance tool integration to the propagation and synergy of scalable performance analysis techniques in different tools.

To my family and towards an age of reason.

### Acknowledgements

First and foremost, I would like to express my deepest gratitude to Professor Kalé for his great patience and guidance throughout the long and oftentimes difficult process of completing the thesis. His talent at managing so many students with so many diverse interests in our field of High Performance Computing is a wonder to behold and a fantastic source of inspiration.

I would also like to thank the rest of my thesis committee: Professor Marc Snir, Professor Michael Heath and Dr. Luiz DeRose, for their kind guidance and constructive feedback.

My very special thanks to Celso Mendes, Isaac Dooley, Eric Bohm, Abhinav Bhatele, Gengbin Zheng and JoAnne Geigner for the immense amount of help and support toward helping me complete the thesis. Also, a big thank-you to the many many hang-out buddies at the Parallel Programming Laboratory over the years for making the lab simply a riot of fun: Eric Bohm, Ramprasad, Esteban Meneses, Filippo, Abhinav, Pritish, Jessie, Rahul Jain, Lukasz, Kumaresh, Phil, Dave, Isaac, Aaron, Esteban Pauli, Chao Mei, Eric Shook, Viraj, Ekaterina, Terry, Sayantan, Rahul Joshi, Chao Huang, Yan, Greg, Orion, Sameer, Hari, Amit, Nilesh, Tarun, Yogesh, Vikas, Sharon, Apurva, Ramkumar, Rashmi, Sindhura, Guna, Mani, Theckla, Jonathan, Josh, Arun, Neelam and Puneet. Special shout-outs go to (you know who you are): my chess buddies, my drinking buddies, my gym buddies and my punching bags (sorry!).

Many thanks for the close friendships with so many people I have met at the University of Illinois at Urbana-Champaign. Your support and company have always been appreciated, even when it contributed to the dreaded "grad student procastination". To the "net party" gang, we sure had many crazy times together: Fredrik Vraalsen, Jim Oly, Chris and Tanya Lattner, Mike

Hunter, Rushabh Doshi, Bradley Jones, Bill Wendling, Howard and Melissa Sun, Nicholas Riley, Andy Reitz, Vinh Lam, Adam Slagell and Joel Stanley. To the "CS 105" gang, thanks for all the fun times working together to teach non-CS majors the joys of Computer Science: Dominique Kilman, Yang Yaling, Marsha and Roger Woodbury, Francis David, Tony Hursh, Reza Lesmana and Shamsi Iqbal. To the other "crazy" grad students of the Computer Science Department, thanks for all the fish!: Lee Baugh and Dmitry Yershov.

To the various faculty and staff of the Computer Science Department who have helped me with so many administrative burdens, special thanks go out to Professor Geneva Belford, Barb Cicone, Mary Beth Kelley, Sheila Clark, Molly Flesner, Shirley Finke and Elaine Wilson.

To Hamid at the Jerusalem restaurant along Wright Street, thank you for the fine food and company. I have enjoyed every moment working on this thesis at your establishment and partaking in the refreshing Turkish coffee you brew.

Last but most certainly not least, to my parents and my grandfather, thank you all for bearing my long absence with such grace, love and unwavering support. To my now-deceased grandmother, thank you for holding out as long as you did in the hope of seeing me graduate. To my sister, thanks for keeping me company over the last few years on Facebook. To my fiancée, thank you for your continued patience and love, and for sticking it out with me long-distance over the thirteen or so years we have been together.

#### Grants and other Acknowledgements:

NAMD was developed at the Theoretical Biophysics Group (Beckman Institute, University of Illinois) and funded by the National Institutes of Health(NIH PHS 5 P41-RR05969-04). Projections and Charm++ are supported by several projects funded by the Department of Energy (subcontract B523819) and the National Science Foundation (NSF DMR 0121695)

This work is supported by grant(s) from the National Institutes of Health P41-RR05969. The author gladly acknowledge supercomputer time provided by Pittsburgh Supercomputer Center and the National Center for Supercomputing Applications via Large Resources Allocation Committee grant MCA93S028.

## **Table of Contents**

| List of 7 | <b>Fables</b> . |                                                                   | ix |

|-----------|-----------------|-------------------------------------------------------------------|----|

| List of I | Figures         |                                                                   | X  |

| Chapter   | r 1 Int         | roduction And Motivation                                          | 1  |

| 1.1       | Paralle         | Performance Tuning Tools                                          | 2  |

| 1.2       | Challer         | nges To Performance Tool Effectiveness Due to Application Scaling | 4  |

| 1.3       | Backgr          | ound                                                              | 6  |

| 1.4       | Thesis          | Objectives And Scope                                              | 8  |

| Chapter   | r 2 Sof         | tware Infrastructure                                              | 10 |

| 2.1       | Charm-          | ++                                                                | 10 |

|           | 2.1.1           | Adaptive MPI                                                      | 13 |

|           | 2.1.2           | Adaptive Overlap                                                  | 14 |

|           | 2.1.3           | Automatic Load Balancing                                          | 16 |

| 2.2       | The Pro         | ojections Performance Analysis And Visualization Framework        | 17 |

|           | 2.2.1           | Charm++ Performance Events                                        | 18 |

|           | 2.2.2           | Projections Event Log Formats                                     | 19 |

|           | 2.2.3           | The Projections Performance Visualization Tool                    | 20 |

|           | 2.2.4           | The Performance Analysis Process Using Projections                | 21 |

| Chapter   | r 3 Sca         | llable Analysis                                                   | 23 |

| 3.1       | Scalabl         | y Finding Object Decomposition With Poor Grainsize Distributions  | 23 |

| 3.2       | Scalabl         | e Idioms Based On Time Profiles                                   | 25 |

|           | 3.2.1           | Time Profile Heuristic: Probable Load Imbalance                   | 27 |

|           | 3.2.2           | Time Profile Heuristic: Comparative Substructure Analysis         | 29 |

|           | 3.2.3           | High Resolution Time Profiles                                     | 31 |

| 3.3       | Finding         | g Interesting Processors                                          | 34 |

|           | 3.3.1           | Case Study: Detecting Bad Multicast Implementation                | 34 |

|           | 3.3.2           | Case Study: Finding Causes For Load Imbalance                     | 35 |

|           | 3.3.3           | Scalable Tool Support For Finding Interesting Processors          | 37 |

|           | 3.3.4           | Conclusion                                                        | 41 |

| 3.4       | Related         | l Work                                                            | 43 |

| Chapter    | 4 Data Volume Reduction                                       | 5 |  |

|------------|---------------------------------------------------------------|---|--|

| 4.1        | Basic Approach                                                | 5 |  |

| 4.2        | Related Work                                                  |   |  |

| 4.3        | Quantifying The Problem                                       | ) |  |

| 4.4        | Applying k-Means Clustering To Performance Data               | 2 |  |

|            | 4.4.1 The $k$ -Means Clustering Algorithm                     | 2 |  |

|            | 4.4.2 Important Choices For k-Means Clustering                | 5 |  |

|            | 4.4.3 Choosing Representative Processors                      | 7 |  |

| 4.5        | Post-mortem Versus Online Data Reduction                      | ) |  |

| 4.6        | Case Study: NAMD Grainsize                                    | 5 |  |

|            | 4.6.1 NAMD - NAnoscale Molecular Dynamics                     | 5 |  |

|            | 4.6.2 Experimental Methodology                                | 7 |  |

|            | 4.6.3 Results                                                 | ) |  |

| 4.7        | Future Work: Extensions To The Basic Approach                 | ł |  |

|            | 4.7.1 Choosing Data Subsets By Phase                          | ł |  |

|            | 4.7.2 Considerations For Critical Paths                       | 5 |  |

| Chanter    | • 5 Online Live Analysis                                      | 2 |  |

| 5.1        | Related Work   78                                             |   |  |

| 5.2        | The Converse Client-Server Interface                          |   |  |

| 5.3        | Continuous Streaming Of Online Performance Data               |   |  |

| 5.4        | Live Parallel Data Collection Of Performance Profiles         |   |  |

| 5.5        | Case Study: Long-Running NAMD STMV Simulation                 |   |  |

| 5.6        | Future Work         95                                        |   |  |

|            |                                                               |   |  |

| Chapter    |                                                               |   |  |

| 6.1        | Related Work                                                  |   |  |

| 6.2        | The BigSim Simulation Framework                               |   |  |

|            | 6.2.1 BigSim Emulator                                         |   |  |

|            | 6.2.2 BigSim Simulator                                        |   |  |

| 6.3        | Performance Analysis Using Fewer Processors                   |   |  |

|            | 6.3.1 Reducing Number Of Procesors Used At Emulation Time 104 |   |  |

| <i>.</i> . | 6.3.2 Number Of Processors Used At Simulation Time            |   |  |

| 6.4        | General Methodology For Hypothesis Testing                    |   |  |

| 6.5        | Analyzing Changes To Network Latency                          |   |  |

|            | 6.5.1 Case Study: Seven-point Stencil Computation             |   |  |

|            | 6.5.2 Validation With Seven-point Stencil Computation         |   |  |

| 6.6        | Analyzing Hypothetical Load Balancing Changes                 |   |  |

|            | 6.6.1 Case Study: Simple Load Imbalance Benchmark             |   |  |

|            | 6.6.2 Validation With Simple Load Imbalance Benchmark         |   |  |

| 6.7        | Future Work: Variations In Object-to-Processor Mapping        | 3 |  |

| Chapter   | 7 Ext      | ending Scalability Techniques To Third Party Tools |  |

|-----------|------------|----------------------------------------------------|--|

| 7.1       | Perform    | nance Call-back (Event) Interface                  |  |

| 7.2       | Integra    | ting An External Performance Module                |  |

|           | 7.2.1      | TAU Profiling Integration                          |  |

|           | 7.2.2      | Instrumentation Overhead Assessment                |  |

|           | 7.2.3      | Experimental Results On Current Machines           |  |

| 7.3       | Scalabi    | lity Benefits Of Integration                       |  |

| Chapter   | 8 Co       | nclusions                                          |  |

| Reference | References |                                                    |  |

## **List of Tables**

| 4.1 | Total volume of trace data summed across all files. <b>ApoA1</b> is a NAMD simu-                                                                          |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | lation with 92k atoms, F1-ATPase simulates 327k atoms while stmv simulates                                                                                |     |

|     | 1M atoms. This data was generated on the XT3 at PSC                                                                                                       | 51  |

| 4.2 | Total volume of trace data summed across all processors in stmv Projections                                                                               |     |

|     | logs with different Particle Mesh Ewald (PME) long-range electorstatics con-                                                                              |     |

|     | figurations. The data was generated on an XT5 at NICS                                                                                                     | 52  |

| 4.3 | Number of non-empty clusters found by clustering algorithm when varying the number of initial seeds uniformly distributed in the sample space The * indi- |     |

|     | cates that processor 0 was alone in its own cluster                                                                                                       | 71  |

| 4.4 | Reduction in total volume of trace data for stmv. The number of processors                                                                                |     |

|     | selected in the subsets are 51, 102, 204 and 409 for 512, 1024, 2048 and 4096                                                                             |     |

|     | original processors respectively.                                                                                                                         | 71  |

| 4.5 | Reduced dataset quality by proportionality based on total height of histogram                                                                             |     |

|     | bars                                                                                                                                                      | 72  |

| 4.6 | Measure of data reduction quality through number of least idle processors re-                                                                             |     |

|     | tained in reduced datasets for 2,048 processors.                                                                                                          | 73  |

| 4.7 | Measure of data reduction quality through number of least idle processors re-                                                                             | 74  |

|     | tained in reduced datasets for 4,096 processors.                                                                                                          | 74  |

| 5.1 | Overhead of collecting utilization profile instrumentation                                                                                                | 92  |

| 6.1 | Experimental setup for baseline latency tolerance experiments executed on 48                                                                              |     |

|     | processors.                                                                                                                                               | 110 |

| 6.2 | Comparison of the SimpleImbalance benchmark average iteration times with a                                                                                |     |

|     | dummy load balancing strategy on 100 processors                                                                                                           | 127 |

| 6.3 | Comparison of the SimpleImbalance benchmark average iteration times with a                                                                                |     |

|     | greedy load balancing strategy on 100 processors                                                                                                          | 127 |

| 7.1 | Overhead of performance modules (microseconds per event)                                                                                                  | 136 |

|     |                                                                                                                                                           | 100 |

## **List of Figures**

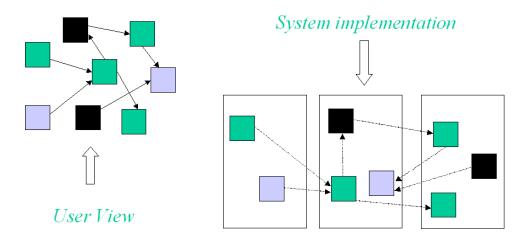

| 2.1        | User view of the CHARM++ adaptive run time system with migratable objects<br>on the left versus a possible system mapping of the same migratable objects on |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | the right                                                                                                                                                   | 11 |

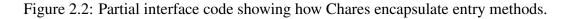

| 2.2        | Partial interface code showing how Chares encapsulate entry methods                                                                                         | 12 |

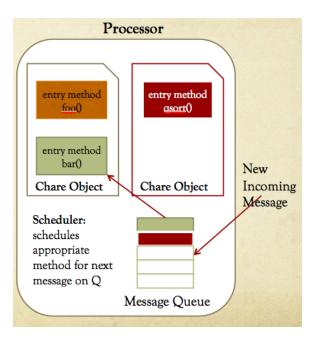

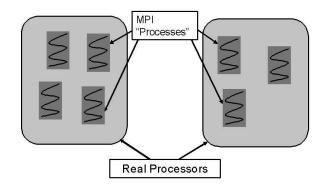

| 2.3<br>2.4 | A basic illustration of the runtime scheduler implementation on each processor.<br>7 AMPI "processes" implemented as user-level threads bound to CHARM++    | 12 |

|            | chare objects which are then bound to 2 actual processors for execution                                                                                     | 14 |

| 2.5        | Adaptive Overlapping                                                                                                                                        | 15 |

| 2.6        | Overview: A summary of overall parallel structure                                                                                                           | 20 |

| 2.7        | Usage Profile: Processor utilization of various activities                                                                                                  | 20 |

| 2.8        | Timeline visualization of processor activity.                                                                                                               | 21 |

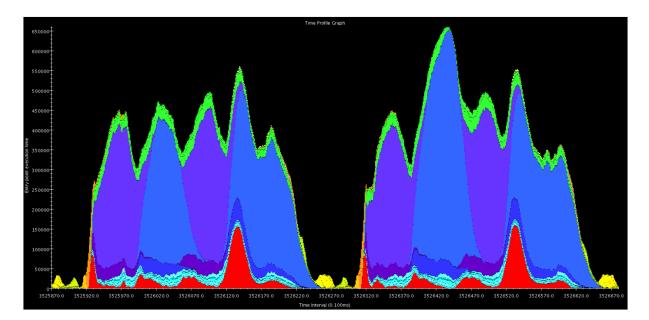

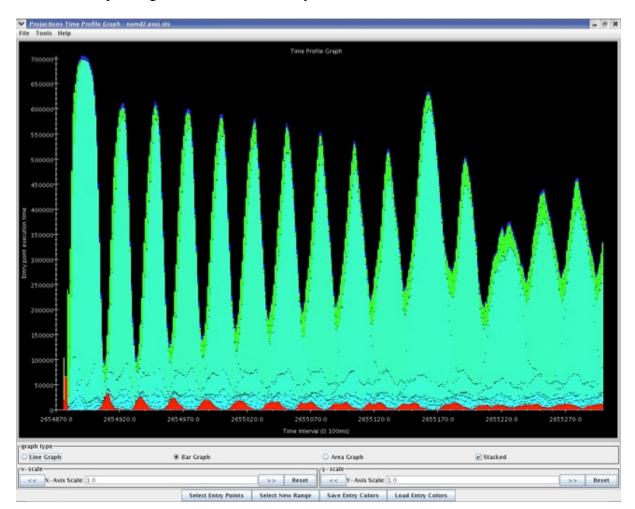

| 3.1<br>3.2 | Histogram of activity grainsizes in a parallel discrete event simulation Low resolution time profile display of the structure of parallel event overlap in  | 25 |

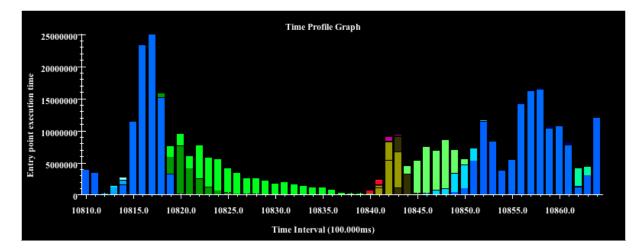

|            | an 8,192 processor run of OpenAtom at 100 ms intervals                                                                                                      | 26 |

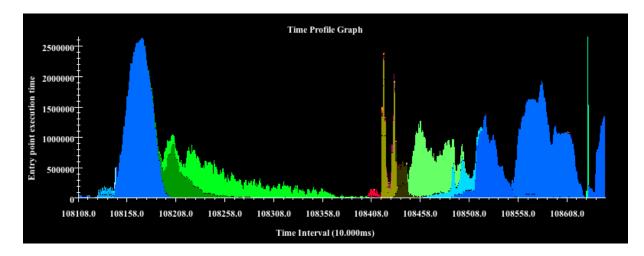

| 3.3        | Higher resolution time profile display of the same 8,192 processor run of Ope-                                                                              |    |

|            | nAtom at 10 ms intervals.                                                                                                                                   | 27 |

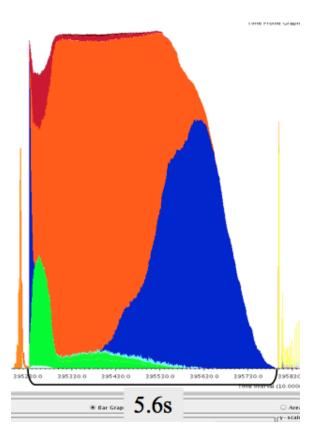

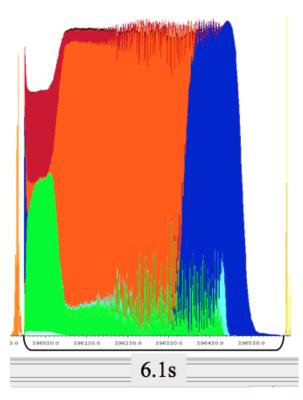

| 3.4        | Time profile of a ChaNGa time step presenting its event-overlap substructure                                                                                |    |

|            | and exhibiting visual cues that point to possible load imbalance                                                                                            | 28 |

| 3.5        | Time profile of ChaNGa time step showing poorer performance after the application of a greedy load balancing strategy. The substructure hints at poorer     |    |

|            | communication performance as a result of the attempt to balance the load                                                                                    | 29 |

| 3.6        | Time profile of ChaNGa time step showing the result of applying a load balanc-                                                                              |    |

|            | ing strategy that also took communication into account.                                                                                                     | 30 |

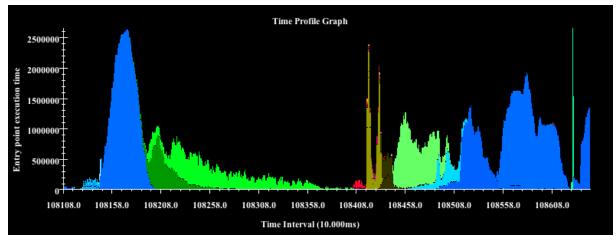

| 3.7        | Very high resolution time profile display of 8 NAMD time steps with high-detail                                                                             |    |

|            | substructure at 100 microsecond intervals.                                                                                                                  | 31 |

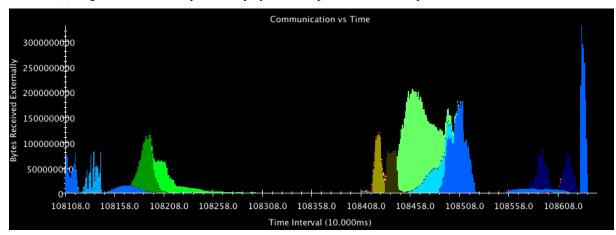

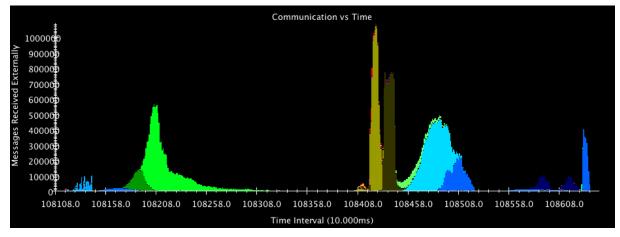

| 3.8        | Correlation of OpenAtom time-profile and communication-over-time graphs.                                                                                    | 33 |

| 3.9        | Zoomed-in view of communication-over-time graph showing the number of                                                                                       |    |

|            | messages received for OpenAtom at 10 ms intervals.                                                                                                          | 34 |

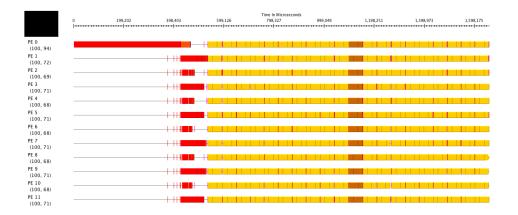

| 3.10       | A small sample of processor timelines out of 1,024 showing (red) events with                                                                                |    |

|            | inefficient multicasts.                                                                                                                                     | 35 |

| 3.11       | A small sample of processor timelines out of 1,024 showing much shorter (red)                                                                               |    |

|            | events with improved multicasts and a corresponding improvement in overall                                                                                  |    |

|            | performance                                                                                                                                                 | 36 |

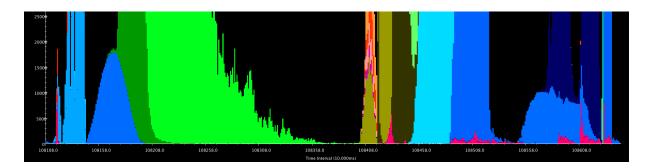

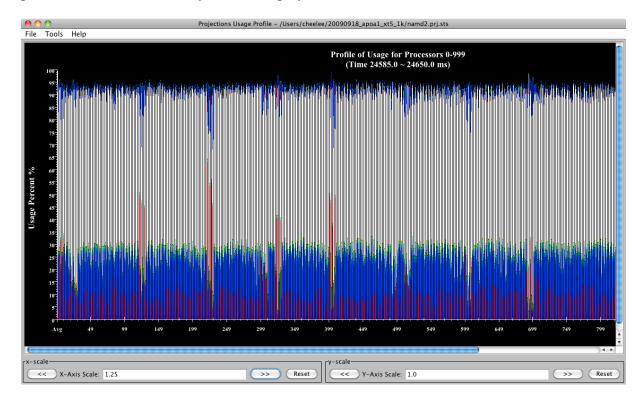

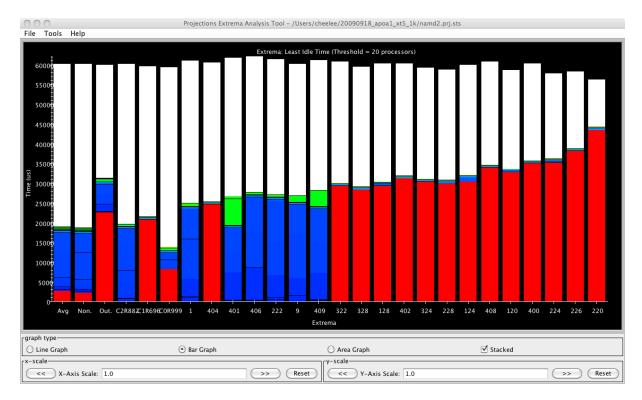

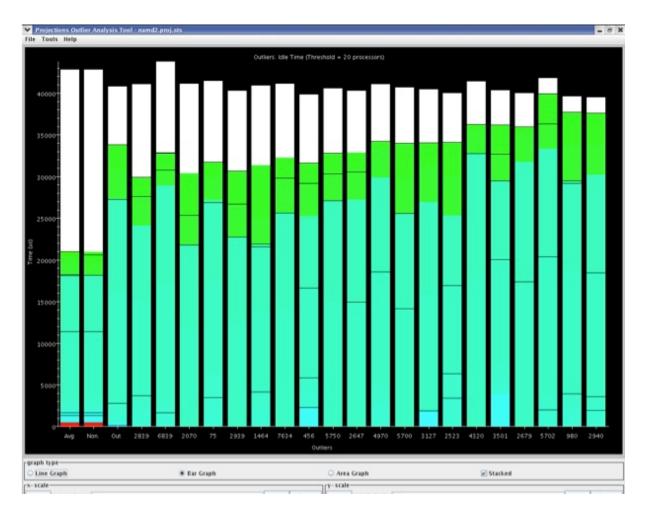

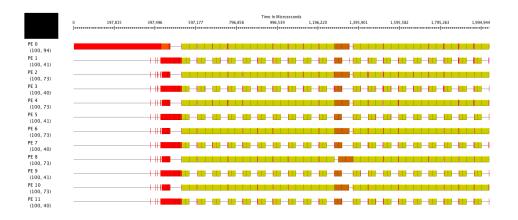

|            | An approximately 800-processor slice of Projections processor usage profiles out of 1,024 processors worth of data.                                                                                                                                                                                                                  | 37       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | An Extrema Tool visualization showing the usage profiles of only the top 20 least-idle processors.                                                                                                                                                                                                                                   | 38       |

|            | Time Profile showing deep troughs between computation iterations, indicating possible load imbalance.                                                                                                                                                                                                                                | 40       |

|            | The Extrema Tool presenting the top list of least idle processors                                                                                                                                                                                                                                                                    | 41<br>42 |

|            |                                                                                                                                                                                                                                                                                                                                      |          |

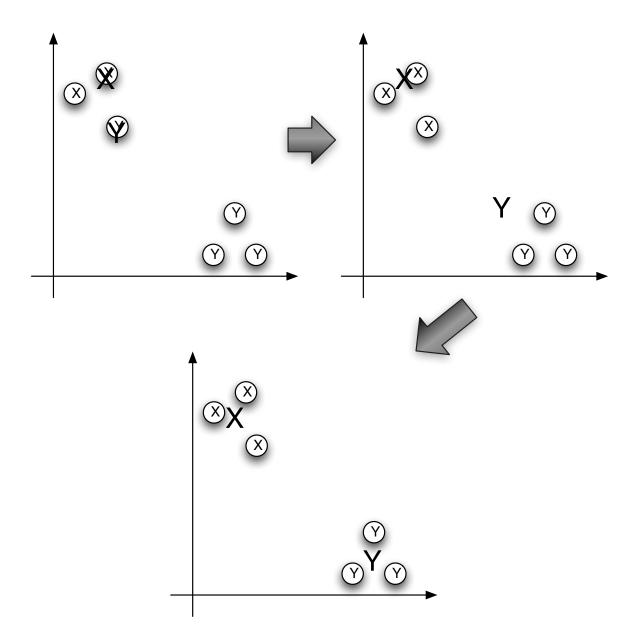

| 4.1<br>4.2 | Basic sequential <i>k</i> -Means Pseudocode                                                                                                                                                                                                                                                                                          | 53       |

| 4.3<br>4.4 | seeds and eventually becoming the cluster centroids                                                                                                                                                                                                                                                                                  | 54<br>60 |

| т.т        | data.                                                                                                                                                                                                                                                                                                                                | 61       |

| 4.5        | Parallel k-Means Iterative Algorithm on the root processor.                                                                                                                                                                                                                                                                          | 62       |

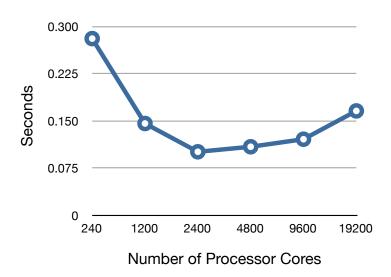

| 4.6<br>4.7 | Parallel <i>k</i> -Means Iterative Algorithm on all processors hosting performance data.<br>Overhead of applying parallel <i>k</i> -Means implementation on NAMD <b>stmv</b> per-                                                                                                                                                    | 63       |

| 4.0        | formance data                                                                                                                                                                                                                                                                                                                        | 64       |

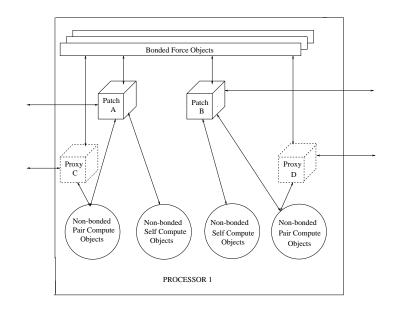

| 4.8        | NAMD 2 hybrid force/spatial decomposition. Atoms are spatially decomposed into <i>patches</i> , which are represented on other nodes by <i>proxies</i> . Interactions                                                                                                                                                                |          |

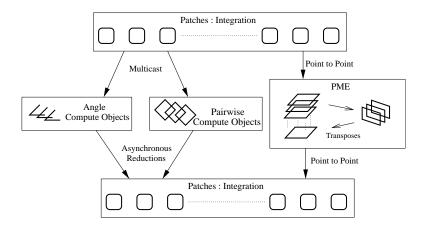

| 4.9        | between atoms are calculated by several classes of <i>compute objects</i> Parallel structure of NAMD                                                                                                                                                                                                                                 | 66<br>67 |

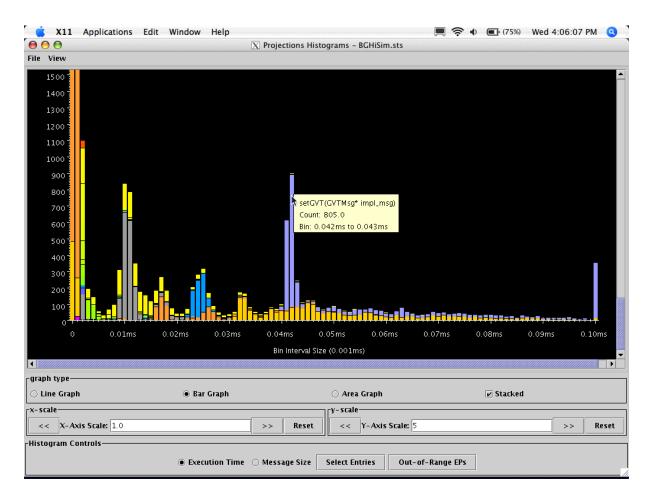

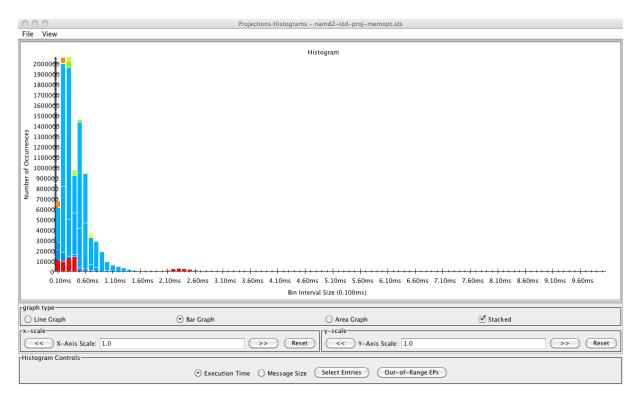

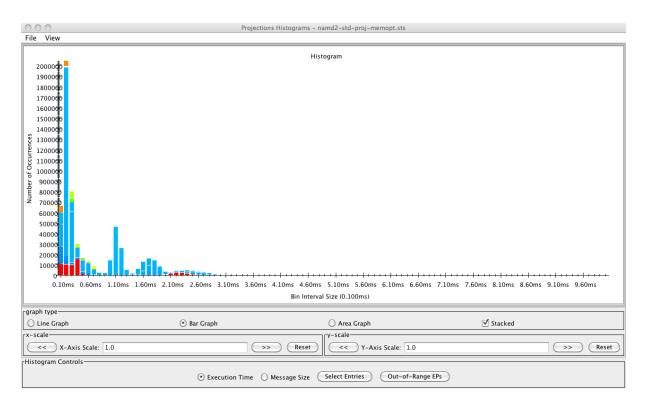

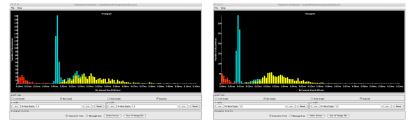

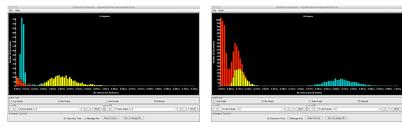

| 4.10       | Histogram plot of <b>stmv</b> in Projections for 4,096 processors. The vertical bars show the number of occurrences of CHARM++ entry methods, distinguished by their colors, that took a certain amount of time to execute. The first bar shows                                                                                      | 07       |

|            | the number of entry methods that executed for 0.1 ms to 0.2 ms, the second for 0.2 ms to 0.3 ms, etc                                                                                                                                                                                                                                 | 68       |

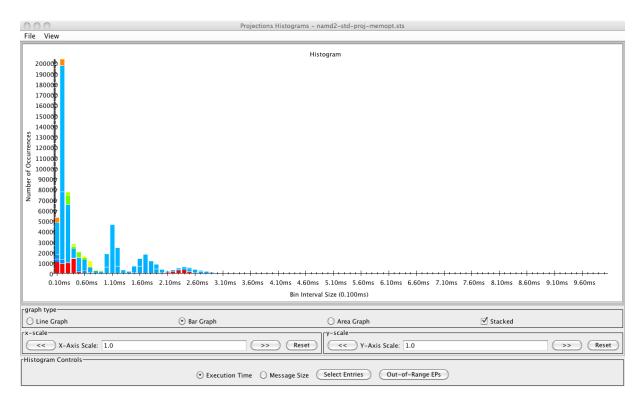

| 4.11       | 0.2 ms to 0.3 ms, etc                                                                                                                                                                                                                                                                                                                | 00       |

|            | where the bins represent longer execution times                                                                                                                                                                                                                                                                                      | 69       |

| 4.12       | Histogram plot of <b>stmv</b> with poor-grainsize in Projections using only the 409                                                                                                                                                                                                                                                  | 70       |

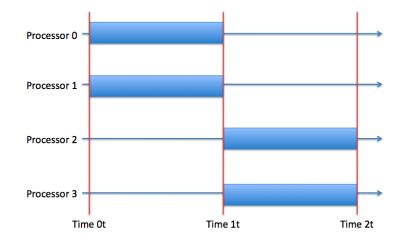

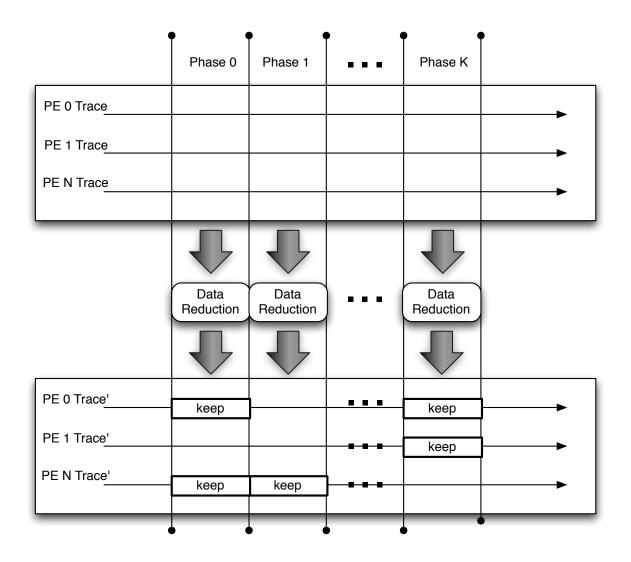

| 4.13       | logs from the reduced dataset                                                                                                                                                                                                                                                                                                        | 70       |

|            | time 0t to 2t                                                                                                                                                                                                                                                                                                                        | 75       |

| 4.14       | Application of data volume reduction techniques to individual execution phases.                                                                                                                                                                                                                                                      | 76       |

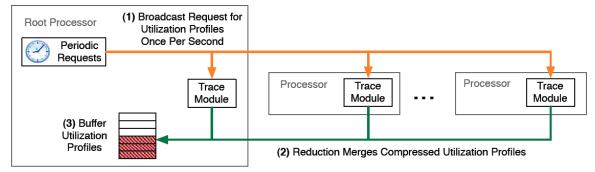

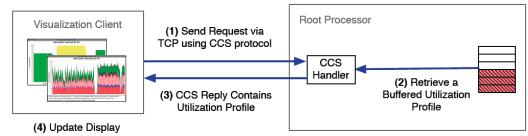

| 5.1        | An overview of the Utilization Profile Tool. The tool is comprised of two separate mechanisms. The first mechanism (A) periodicially gathers performance data in the parallel runtime system. The second mechanism (B) allows a visualization client to retrieve the previously buffered performance data from the parallel program. | 83       |

|            |                                                                                                                                                                                                                                                                                                                                      | 03       |

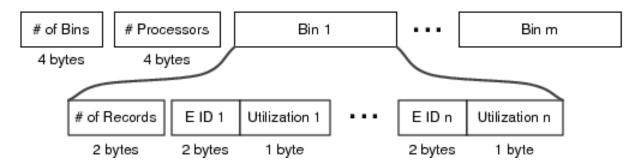

| 5.2     | Compressed utilization profile format.                                                | 85  |

|---------|---------------------------------------------------------------------------------------|-----|

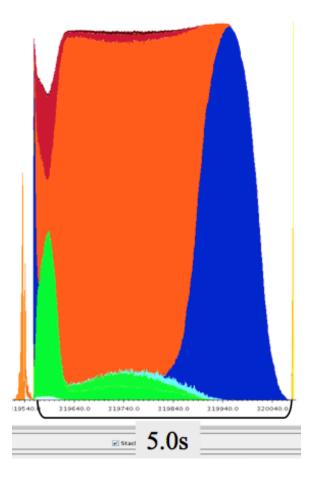

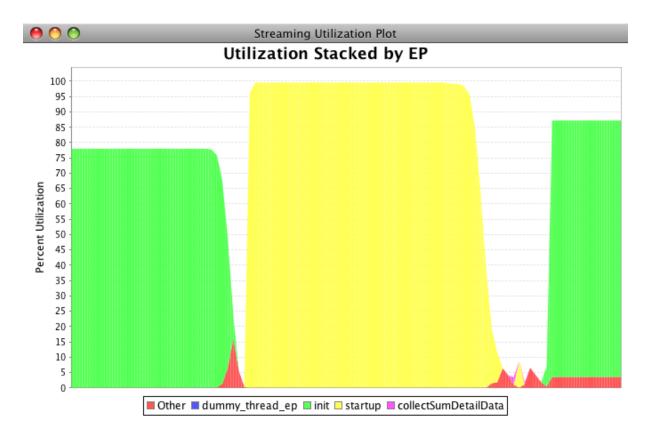

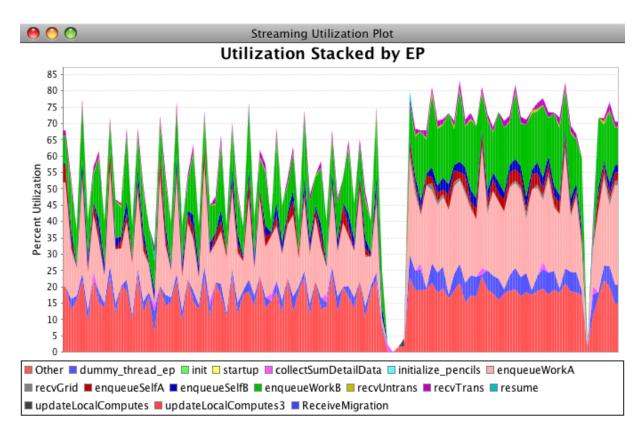

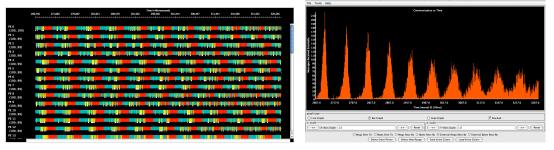

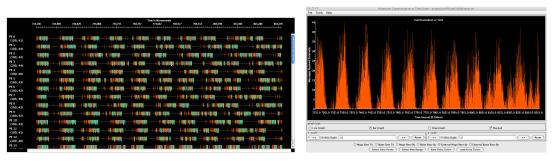

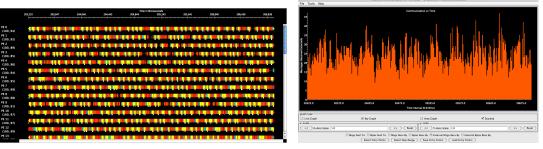

| 5.3     | A screenshot of the streaming view in our tool. This view represents 10 seconds       |     |

|         | of execution during startup for NAMD on 1,024 processors running the STMV             |     |

|         | molecular system.                                                                     | 89  |

| 5.4     | This streaming view represents 10 seconds of execution during the early steps         |     |

|         | when load balancing takes place. Two valleys, corresponding to the two load           |     |

|         | balancing steps, are clearly seen. This screenshot comes later in the execution       |     |

|         | of the same program run as in figure 5.3.                                             | 90  |

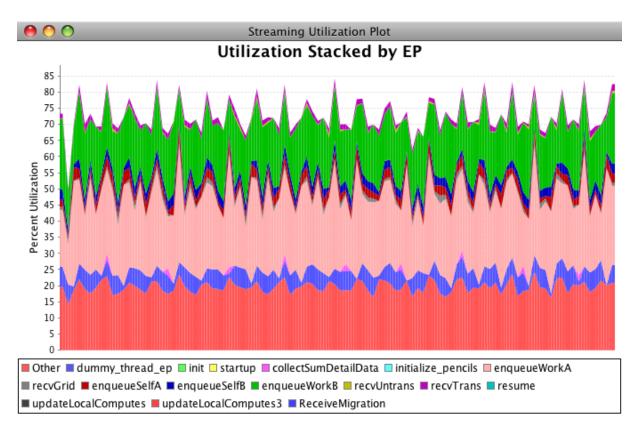

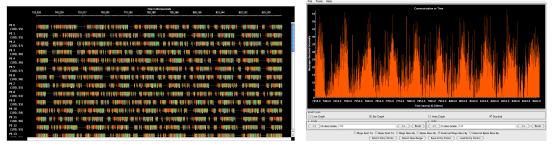

| 5.5     | This streaming view represents 10 seconds of execution during the later simula-       |     |

|         | tion steps once a more uniform load balance has been achieved. Each bar repre-        |     |

|         | sents the average utilization for 100ms of execution time. For this program, the      |     |

|         | timesteps are shorter than this duration and hence the utilization doesn't reach      |     |

|         | 100% in this plot. This screenshot comes later in the execution of the same           |     |

|         | program run as in figures 5.3 and 5.4.                                                | 91  |

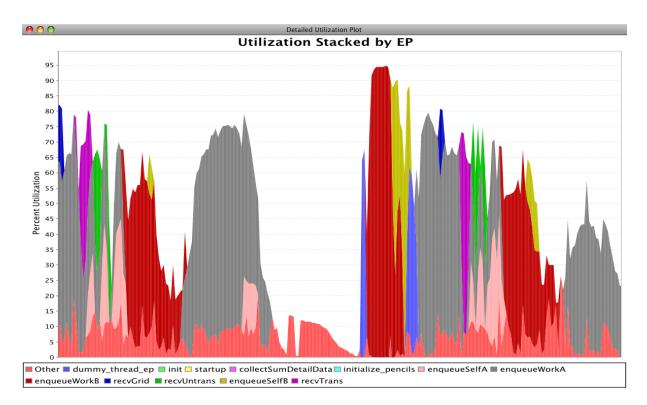

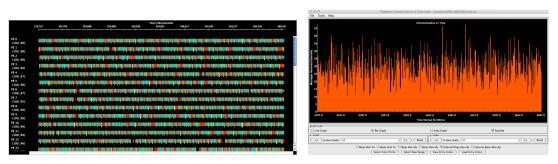

| 5.6     | This detailed view plots the full 1ms resolution utilization profile for 0.25 sec-    |     |

|         | onds of execution time for a NAMD STMV run on 1,024 processors. This                  |     |

|         | snapshot captures steps with poor load balance.                                       | 92  |

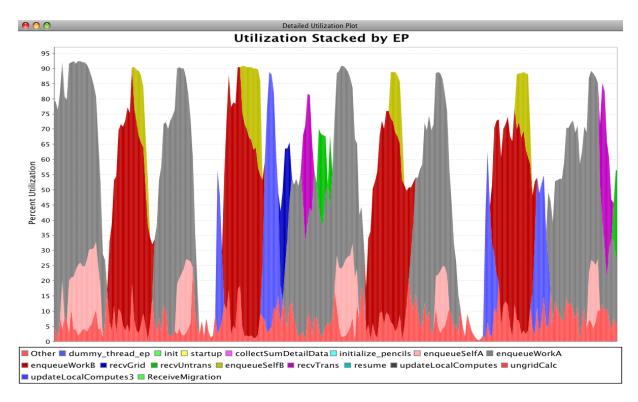

| 5.7     | This detailed view shows a later plot from the same run shown in figure 5.6,          |     |

|         | after load balancing improves the performance by shortening the time per step.        | 93  |

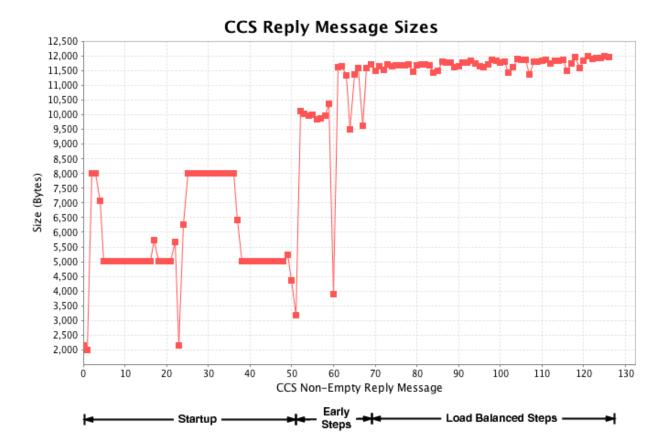

| 5.8     | Sizes of the compressed utilization profiles received by the visualization client.    |     |

|         | The total bandwidth required to stream the data is thus under 12KB/second for         | 0.4 |

|         | this program, namely NAMD simulating the STMV system on 1,024 processors.             | 94  |

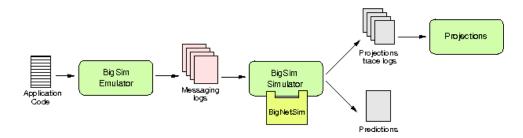

| 6.1     | BigSim Structure and Output                                                           | 100 |

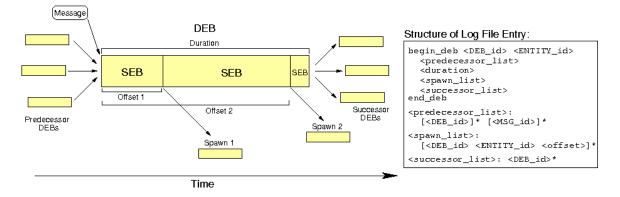

| 6.2     | Dependent Execution Block.                                                            | 101 |

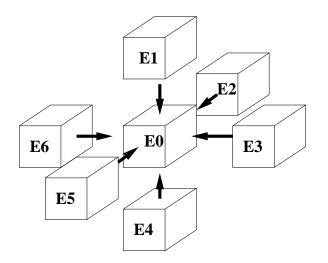

| 6.3     | Computation interaction between data elements at each seven-point stencil iter-       |     |

|         | ation. At iteration $i + 1$ , element E0 gets the value of $(E0 + E1 + E2 + E3 + E3)$ |     |

|         | $E4 + E5 + E6) \div 7.$                                                               | 108 |

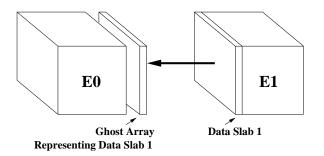

| 6.4     | Parallel object E1 sends its data slab to object E0 to be kept as a ghost array for   |     |

|         | the iteration's computation.                                                          | 108 |

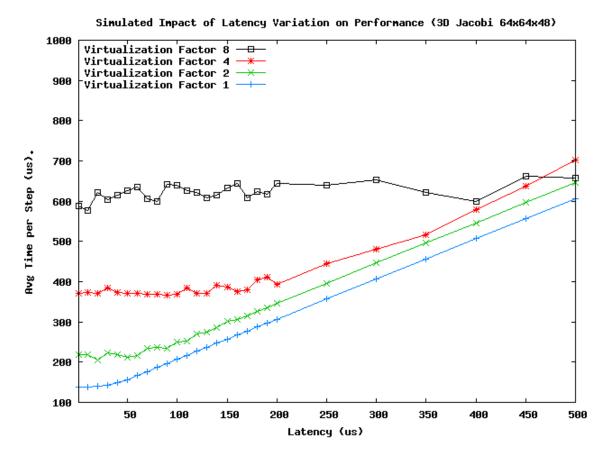

| 6.5     | BigSim-predicted latency tolerance trends for a 64x64x48 7-point stencil com-         |     |

|         | putation code                                                                         | 111 |

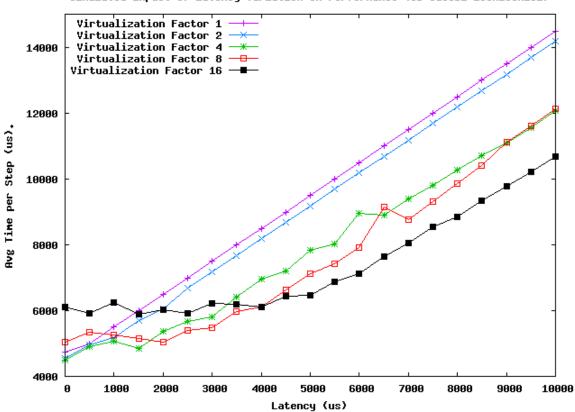

| 6.6     | BigSim-predicted latency tolerance trends for the 256x256x192 7-point stencil         |     |

|         | computation code                                                                      | 112 |

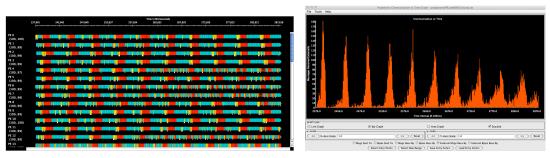

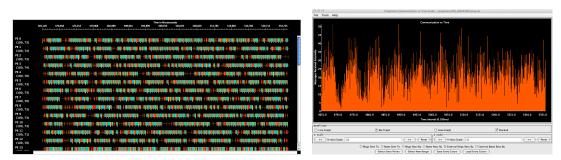

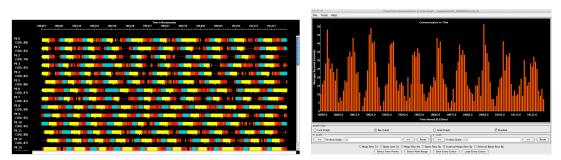

| 6.7     | Visualization of timeline and communication behavior for the 256x256x192 7-           |     |

|         | point stencil computation with a simulated latency of 1 us                            | 113 |

| 6.8     | Visualization of timeline and communication behavior for the 256x256x192 7-           |     |

|         | point stencil computation at virtualization factor 8 with a simulated latency of      |     |

|         | 2 ms                                                                                  | 114 |

| 6.9     | Visualization of timeline and communication behavior for the 256x256x192 7-           |     |

| <i></i> | point stencil computation with a simulated latency of 5 ms                            | 115 |

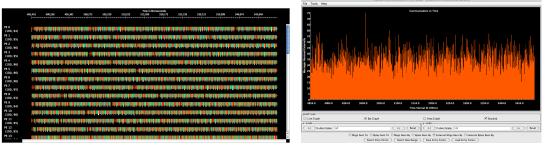

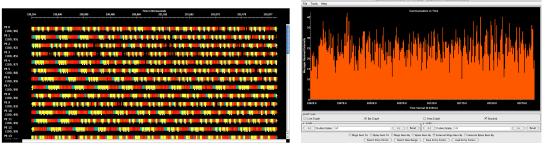

| 6.10    | Visualization of timeline and communication behavior for the 256x256x192 7-           | 111 |

|         | point stencil computation at with a simulated latency of 10 ms                        | 116 |

| Visualization of timeline and communication behavior for the 64x64x48 7-point     |                                           |

|-----------------------------------------------------------------------------------|-------------------------------------------|

| 1 *                                                                               | 117                                       |

| Visualization of timeline and communication behavior for the 64x64x48 7-point     |                                           |

| stencil computation at a latency of 100 us                                        | 118                                       |

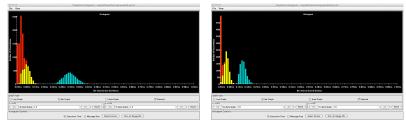

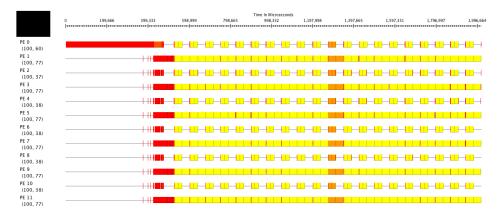

| Histogram visualization of activity grain sizes for the 64x64x48 and the 256x256x | 192                                       |

| 7-point stencil computation experiments                                           | 119                                       |

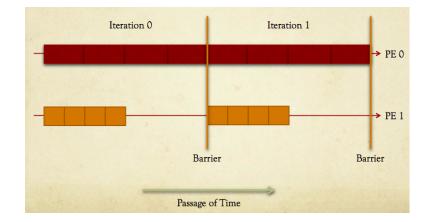

| Illustration of object placement and execution of the basic SimpleImbalance       |                                           |

| application.                                                                      | 123                                       |

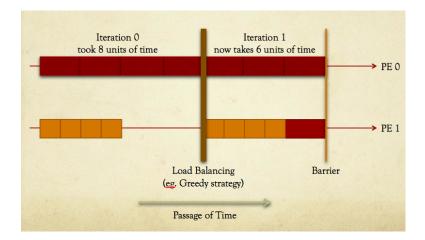

| Illustration of object placement and execution of the SimpleImbalance applica-    |                                           |

| tion with the <i>GreedyLB</i> load balancing strategy applied.                    | 124                                       |

| Projections timeline showing the baseline performance profile of the benchmark    |                                           |

| with deliberate load imbalance.                                                   | 125                                       |

| Projections timeline showing what happens if the Greedy load balancing strat-     |                                           |

| egy is applied.                                                                   | 126                                       |

| Projections timeline showing what happens if the Rotate load balancing strategy   |                                           |

| is applied.                                                                       | 127                                       |

|                                                                                   |                                           |

| Simplified fragment of framework base class.                                      | 132                                       |

| CHARM++ runtime event transition                                                  | 134                                       |

| TAU integration with CHARM++ framework.                                           | 135                                       |

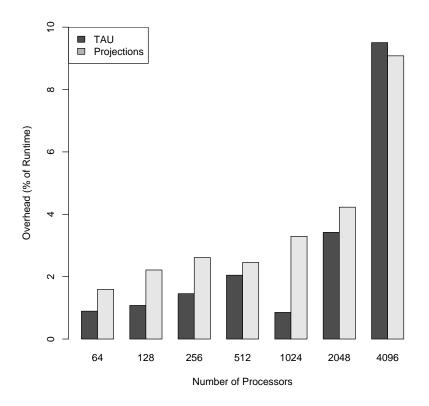

| Instrumentation overhead for TAU and Projections with NAMD running on             |                                           |

| Ranger.                                                                           | 138                                       |

|                                                                                   | stencil computation at a latency of 1 us. |

# Chapter 1 Introduction And Motivation

Modern parallel machines are getting larger. In the June 2009 list of the top 500 most powerful supercomputers <sup>1</sup>, the fastest possessed 129,600 processor cores running at a peak performance of 1,456.70 GigaFLOPS. Meanwhile, the largest machine weighed in at 294,912 cores. The processor growth trends are crystal-clear when one compares the bottom 100 machines in the June 2009 list with the one for June 2008. In June 2008, most machines in the bottom 100 had fewer than 2,000 processor cores. By June 2009, only a couple had fewer than 2,000 processor cores.

Bigger and faster parallel machines bring both opportunity and challenges to the user community. Opportunity, because of the greater computational resources made available to scientific applications. Challenges, because attaining good application performance on larger machines can be non-trivial. Achieving good performance for complex scientific applications require good tool support for performance analysis and tuning. However, as applications are scaled to execute on larger and larger processor counts, many traditional idioms guiding performance tool usage to study these applications break down in the face of the large performance datasets gathered for the purpose.

This thesis is motivated by the challenges to the scalable conduct of performance analysis for applications executed on large numbers of processors. The reasons behind the limitations on performance tool effectiveness are explored. Techniques are introduced to overcome some of these limitations and new scalable analysis idioms are investigated.

In this chapter, we begin by presenting a detailed context for the field of performance anal-

<sup>&</sup>lt;sup>1</sup>http://www.top500.org

ysis and tuning for parallel applications in general. We discuss the motivations for scaling applications to larger numbers of processors and the resulting impact it has on the effectiveness of tools use to study the performance of those applications. Existing literature on the wide range of performance tools and the effort to address tool scalability are then discussed. Finally, we detail the main objectives of the thesis.

### **1.1 Parallel Performance Tuning Tools**

Performance tools are employed to study the parallel performance of large complex applications. A large class of such applications are scientific simulation codes that include molecular dynamics simulations, rocket propellent simulations and cosmological simulations amongst many others. Performance tools enable *performance studies* to be conducted on *performance data* captured during an application's execution. Performance studies generally aim to find and correct performance bottlenecks in the parallel code. Studies for this purpose are also refered to as "performance debugging". In any complex scientific application, non-trivial interplay between computation, communication across processors and even computational dependencies within a processor can make the application suffer unexpectedly poor performance.

Performance debugging can be conducted for an application which is executed on a fixed number of processors. The purpose is to tune the application to run faster on the same number of processors. Performance tools are also used to understand the effects on the performance of a parallel application when it is *scaled* to larger numbers of processors. The purpose in this case is to identify root causes inhibiting performance so as to eliminate or mitigate the negative effects in order for the application to scale efficiently to higher numbers of processors. Allowing applications to scale efficiently is important as there are a number of reasons that drive scientists to scale their codes:

1. to run a particular simulation input faster so they may produce results faster; or

- to run a particular simulation input faster so they may produce results for longer simulation observations (e.g. a protein folding over a simulated time of 1 us instead of 100 ns) within the same execution time constraint; or

- 3. to run larger or more detailed simulations that may not otherwise be possible on smaller numbers of processors because of memory or execution time constraints.

For the purposes of our discussion on performance tool effectiveness, we define *performance space* to be a 4-dimensional domain, inherent in every parallel application. The 4 dimensions of performance space are:

- 1. the continous domain of *elapsed execution time* of the application.

- 2. the discrete domain of *processors* or threads used in the execution.

- 3. the discrete domain of the *types of activities* (e.g. functions calls, messaging activity) that can occur.

- 4. the discrete domain of the *types of metrics* that can be recorded for the activities that occur (e.g. time spent, number of bytes sent, number of level 1 cache misses).

We define an *instrumented application* to be one which captures and generates performance data. Performance data can be captured in many different ways in the context of performance space (see Section 1.3 for various well-known systems of each). For typical *statistical profiles*, a counter is maintained on each processor for each activity that can occur in an application. As the application executes, it is sampled at some regular time interval. At each sample, the current activity's counter is incremented. Thus, at the end of the application, one can compute an approximate breakdown of the proportion of time spent by each activity on each processor over the application's total execution time. *Direct measurement profiles* perform some accumulation operations on various performance metrics when encountering activity triggers or *events*. Pairs of events can represent the start and end of *activities* in the application. Different profiling tools

can perform many different forms of metric accumulation. Finally, *event trace logging* typically records all the details of pertinent performance metrics when encountering activity triggers. The design decisions behind the different methods of capturing performance data are usually based on the trade-off between detail and data volume.

## 1.2 Challenges To Performance Tool Effectiveness Due to Application Scaling

We can loosely quantify the measurement of effectiveness for performance tools based on the time-to-solution for specific performance debugging session. The time-to-solution covers multiple components:

- 1. the time taken for an instrumented application to be executed at the necessary processor counts;

- 2. the time taken to produce performance data for consumption by a performance tool. This component includes the writing of data to disk and transfer of the written logs, if necessary, to a remote machine where the performance tool is executed;

- 3. the time taken for a performance tool to acquire the necessary performance data and process it for analysis in response to a request by a human analyst. This component includes the reading of log data from the disk;

- 4. the time taken for an analyst to locate specific performance problems given some performance information (visual or otherwise) provided by the tool. This involves an iterative process where the analyst explores alternative hypotheses, and develop an intuitive understanding of the performance issues by studying multiple views and analysis supported by the tool;

- the time taken to attempt to fix the performance problem. This can be as simple as changing application configuration parameters or as complicated as application code modification;

- 6. the time taken to re-execute the application to validate that an attempted solution has worked.

We now discuss how application scaling impacts the performance space defined above. We will then discuss how this impact on performance space translates to impact on performance tool effectiveness based on the list of time-to-solution components.

There are two forms of application scaling. The first is known as *strong scaling* where an application runs the same simulation input on larger numbers of processors. The total computation work for the simulation across all processors, excluding parallel overheads, typically remains the same. The second is known as *weak scaling* where an application runs larger or more detailed simulation inputs on larger numbers of processors. The total computation work for the simulation inputs on larger numbers of processors. The total computation work for the simulation inputs on larger numbers of processors.

For both strong and weak scaling, the number of processors in the processor-dimension of performance space is increased. This directly translates to a larger exploration space for an analyst when attempting to make sense of the performance information. Hence human analysis time and performance tool response time may be affected. It also means the application potentially spends a longer time waiting in the queue of a supercomputing facility as larger processor resources are required.

The number of activity instances over time also increases for both forms of application scaling. In the case of strong scaling, this can be attributed mostly to more communication events overall. In the case of weak scaling, we have additional communication events as well as activities due to additional work for the larger simulation input. Depending on the way performance data is captured, this can impact overall performance data volume which in turn affects the effectiveness of a performance tool. We can now identify broad categories for techniques to enhance the effectiveness of a performance tool. These include:

- addressing performance *tool scalability* with respect to performance data volume. Scalability here refers to a performance tool's ability to present usable and useful performance data in the face of increasing data volume.

- 2. addressing time it takes for performance data to become *available* to a performance tool.

- 3. addressing the *turn-around time* for performance hypothesis experiments. This includes the time it takes to schedule and execute an application on a supercomputer to generate performance information for performance debugging or validation purposes.

### 1.3 Background

There are many different performance analysis and visualization tools that work on different programming models, use various forms and formats of performance data, and adopt different ways of presenting or analyzing recorded performance information.

In this section, we perform a quick sweep of the various tools to get a flavor of what is involved in performance analysis research. Detailed discussions of related research are deferred to the relevant related work sections in subsequent chapters.

Profile logs capture some summary of performance metrics, usually over an application's lifetime. Profiles can be generated by statistical sampling methods like that used by gprof [31]. Statistical profiles are perhaps the most compact, showing the contribution to total sample counts by each activity, typically the function calls invoked in the application. Statistical profiles are most useful for capturing timing information about activities, they are not as useful for events nor for dealing with metrics not associated with execution time. Other profiles can be generated by methods based on direct measurement of performance metrics of pre-defined events and activities, as is done in Projections [44] summaries or TAU profiles [69] using the Paraprof tool. Wylie et. al. [84] describes a similar approach for the KOJAK/Scalasca project

by what they call runtime measurement summarisation. Profile-based tools generally do not capture dynamic performance changes to the application over time. It is, however, possible to take snapshots [55] of profiles in TAU, allowing the capture of performance changes over known user-defined phases, but at the cost of storing an additional profile for each snapshot in the buffers. Profile summaries in Projections do the same, but uses fixed time intervals instead. Profiles tend to be compact, depending on their specific format, but not as effective for the purposes of studying the nature of complex inter-processor dependencies and interactions.

For the latter, detailed event trace logs are most effective. Detailed event logs store the faithful, usually chronological, time-stamped recording of performance metrics per pre-defined event or activity (e.g. function call, message sends) encountered in the application. These logs tend to be extremely large and care has to be taken to control the generated data volume for effective post-mortem analysis. Vampir [56], Jumpshot [85], Paragraph [33], Paradyn [52], KOJAK [80], Pablo [64], Cray Apprentice<sup>2</sup> [19, 20] and Projections [44] are examples of tools and systems that can use various forms of detailed event trace logs.

Regarding scalability for performance analysis tools, Wolf et. al. [79] offered an excellent overview of the technical issues, challenges and broad approaches to handling large event traces. Specifically, they surveyed nine approaches implemented by various research groups: using frame-based data formats [82]; periodicity detection [24]; call-graph compression [47]; distributed analysis [11]; automatic pattern search [81]; topological analysis [6]; holistic analysis [83]; granularity reduction [54]; and statistical analysis [2]. Meanwhile, the Scalasca project [27, 26] adopts scalable approaches to analysis based on automatic analysis methods. They search for patterns indicative of performance problems specific to MPI using a distributed analysis tool on full event traces. Roth and Miller [66] focus on an online approach to automated performance analysis.

The approach in this work sometimes complements and is sometimes similar to the scalabilityoriented research mentioned above, and is contemperoneous with them. The unique aspects to our work include a pragmatic semi-automatic flavor that keeps the analyst in control of all stages of analysis, exploiting the capabilities of an adaptive runtime system, and using the extra abstractions available to performance analysis in the context of a data-driven object-oriented model of programming.

### **1.4 Thesis Objectives And Scope**

The objective of the thesis is to develop techniques to address scalability challenges that impact the effectiveness of performance analysis idioms. We have implemented our techniques and approaches in this thesis using our performance tool named Projections for the Charm++ parallel programming model based on message-driven execution and migratable objects. Projections is heavily-used for the performance study and tuning of many complex production codes including the classical molecular dynamics simulation application NAMD [62], OpenAtom [8, 75] which simulates molecular dynamics using the Car-Parrinello ab initio method and the cosmological simulator ChaNGa [29]. Each of these production codes have been scaled to many thousands of processors. To remain relevant, any analysis tool would have to maintain its effectiveness as applications are further scaled to tens and hundreds of thousands of processors.

There are four main thrusts to the thesis research, each addressing different aspects of the challenges described in section 1.2. The first covers new tool support for scalable performance analysis idioms. To effectively find performance problems in the enlarged performance space when applications run on more processors, scalable analysis idioms are required. We will investigate how some performance analysis idioms are not scalable and how the tools and methods we developed will help.

The second is the exploration of techniques for the reduction of performance data volume without significant loss of detail from performance event traces. This reduction is possible because most of the data in an event trace tend to capture normal application behavior. The challenge in event trace compression is to retain data that highlight performance anomalies while preserving sufficient normal behavior to maintain the necessary context for an analyst to visually explore performance space. While the techniques can be applied to performance event logs that have already been written to disk, they can more importantly be applied to performance logs still in memory at the end of an application's execution.

The third thrust explores the benefits of live analysis and interaction with running applications. We look at how live interaction can help enhance some capabilities described in the research thrust for data reduction. At the same time, live interaction is an enabling mechanism for the online streaming of performance data as the application executes. It enables new and powerful idioms for studying application performance at large scales, allowing long-running behavior patterns to be revealed. It also improves the timeliness of performance data delivery to a performance tool.

Finally, we target methods for the reduction of job turn-around time. This idea is based on the observation that performance analysis is usually an iterative process where hypotheses are tested through re-execution and re-analysis. This can take a prohibitively long time on the job queues on typical large-scale machines, especially for the study of an application's fullmachine scaling. We explore simulation-based methods that enable analysts to test performance hypotheses using far fewer processors than would otherwise be necessary if an application had to be re-executed. These methods also have the added benefit of significantly reducing the usage of precious computational resource allocation units.

# Chapter 2 Software Infrastructure

In this chapter, we describe the basic software infrastructure employed to demonstrate the performance tool scalability and effectivenes techniques discussed in this thesis. The CHARM++ runtime system implements the message-driven object-oriented parallel programming paradigm used for our studies. Adaptive MPI is an implemention of the message-passing paradigm that makes use of many of the adaptive features provided by the CHARM++ runtime system. The Projections performance analysis framework is part of the CHARM++ runtime system. It provides the necessary capabilities for the instrumentation, generation and visualization of performance data.

### 2.1 Charm++

CHARM++ [40] is a portable C++ based parallel programming language based on the *migrat-able object programming model* and resultant *virtualization* of processors. In this model [42], a programmer decomposes a problem into N *migratable objects* that will execute on P processors, where ideally N >> P. The application programmer's view of the program is of the migratable objects and their interactions; the underlying runtime system keeps track of the mapping of the migratable objects to processors and performs any remapping that might be necessary at run-time. The programmer, not being constrained by physical processors, is able to focus on the interaction between the work partitions and concentrate on better expression of the parallel algorithm. At the same time, the runtime system can perform efficient resource management with the large number of migratable objects. The difference between the user view

and the system's implementation are illustrated in figure 2.1. In CHARM++, migratable objects are known as *chares*. Chares are C++ objects which encapsulates special *entry methods* that are invoked asynchronously from other chares through messages. In the basic CHARM++ model, entry methods are encapsulated functions that cannot be pre-empted after they have been invoked. CHARM++ uses message-driven execution to determine which entry method, and hence chare, gets control of a processor. The partial code example in figure 2.2 highlights how this model works.

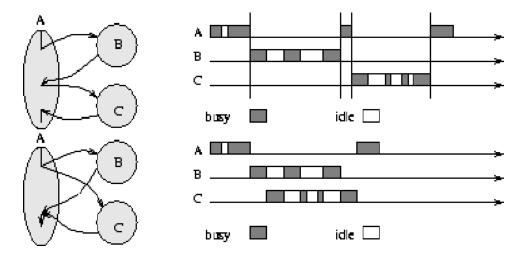

Figure 2.1: User view of the CHARM++ adaptive run time system with migratable objects on the left versus a possible system mapping of the same migratable objects on the right.

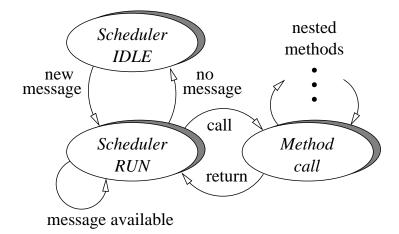

An advantage of this approach is that no chare can hold a processor while it is idle but waiting for a message. Since N >> P, there may be other chares on the same processor that can overlap their computation with the communicating chare. This *adaptive overlap* is enabled by a runtime scheduler on each processor. The scheduler picks up incoming messages and queues them in a local buffer. When an entry method completes on the processor, the local scheduler will invoke the appropriate handler routine for the next entry method associated with the message at the head of the queue. If the queue is empty, the scheduler enters into an *idle state*, waiting for new messages from other processors. The operation of the runtime scheduler on each processor is illustrated in figure 2.3.

```

mainmodule pingpong {

. . .

chare Ping {

// constructor

entry Ping(void);

// generates a PongMsg and calls recv() on a

// remote object of chare class Pong

entry void recv(PingMsg *);

};

chare Pong {

entry Pong(void);

// generates a PingMsg and calls recv() on a

// remote object of chare class Ping

entry void recv(PongMsg *);

};

. . .

}

```

Figure 2.3: A basic illustration of the runtime scheduler implementation on each processor.

CHARM++ is actively used in a number of major real-world scientific applications [60, 75, 29] that demand high scalability for some of the phenomena the scientific community wishes to study.

### 2.1.1 Adaptive MPI

The Message Passing Interface (MPI) [1] is a library specification for message-passing as the paradigm for communication and synchronization between processors in a parallel program. It is a standard that defines an application programmer's interface for messaging but leaves flexible the details for specific machine implementation. The interface was also designed with language independent semantics with convenient C and Fortran bindings. Since its introduction, it has become a widely accepted standard for parallel programming over a wide range of hardware.

Adaptive MPI (AMPI) [35] tries to add important adaptivity capabilities available to CHARM++ to MPI's rich feature set. These capabilities will be highlighted in sections 2.1.2 and 2.1.3. As of this writing, AMPI is compliant with the MPI 1.1 standard. AMPI implements its MPI processes as user-level threads bound to chares as illustrated in figure 2.4. This binding of user-level threads to migratable chare objects is key to automatic load balancing support for AMPI programs. Message passing between AMPI processes is implemented as communication between chares. Send calls in AMPI map directly to equivalent CHARM++ send semantics. Receive calls, however, have to be implemented as CHARM++ entry methods to bridge the semantic gap between the CHARM++ and AMPI models for the support of basic MPI 2-sided communication. MPI 1-sided communication, introduced in the MPI 2.0 standard, are currently not supported.

Standard MPI programs divide the computation onto P processes and the typical MPI implementation assigns and executes each of these processes on its own physical processor. An AMPI programmer would divide the computation into a V virtual processors (user-level thread) which then gets mapped onto P physical processors. Unlike the scenario of writing an MPI for

Figure 2.4: 7 AMPI "processes" implemented as user-level threads bound to CHARM++ chare objects which are then bound to 2 actual processors for execution.

a typical MPI implementation, an AMPI programmer would not worry about the number of physical processors, similar in nature to how a CHARM++ programmer would concentrate on the decomposition rather than the number of processors the application would run on. When V = P, the AMPI program would execute in the same way it would for typical MPI implementations. To exploit the adaptivity capabilities of the underlying CHARM++ runtime system, V needs to be significantly larger than P.

### 2.1.2 Adaptive Overlap

One important feature of the CHARM++ runtime system is its natural ability to dynamically schedule work based on incoming messages to a processing thread. This means that the computation work from two independent parallel software components could be overlapped dynamically. When one software component becomes idle on a processor, work from another could be scheduled. The adaptive overlap can also be refined by the ability to set different message priorities for different software components. This will have significance in the context of the work on continuous performance data streaming in Chapter 5.

To highlight this feature, consider the scenario illustrated in Figure 2.5 (This example is taken from [41]). There are three parallel components A, B and C spread across all processors. A must call B and C, but there is no dependence between B and C. In traditional MPI style

programming model, the programmer has to choose one component between B and C to call from A first on all processors. Only when the first chosen component returns can A call the remaining one on all processors. This model can be inefficient because when one component idles the CPU, for example, when waiting for communication to complete, other components are not allowed to take over and do useful computations, even though there is absolutely no dependence between the components.

Figure 2.5: Adaptive Overlapping

With the CHARM++ runtime support, A can invoke B on all the processors, initiating computation and sending out messages, and since there is no dependence between B and C, A can also start off C in a similar fashion, and thereby components B and C can interleave their execution. When one component blocks due to communication or load imbalance, the other component can automatically overlap the idle time with computation, based on the availability of data, as illustrated in Figure 2.5. With non-blocking calls and careful programming, the programmer could achieve the same effects with MPI, but the price is additional programming complexity and a loss of modularity.

#### 2.1.3 Automatic Load Balancing

One of the most prominent benefits of an adaptive runtime system like CHARM++ with migratable objects is the capability of dynamic load balancing by migrating objects across processors. This capability benefits parallel applications because of the *principle of persistence*. The principle of persistence is an empirical heuristic about parallel program behavior over time. For most parallel applications expressed in terms of virtualized processors, the computation loads and communication patterns tend to persist over time. This heuristic applies to many programs with dynamic behavior, including those using adaptive mesh refinement with abrupt but infrequent changes, to those simulating molecular dynamics with slow and gradual changes over time.

Based on the principle of persistence, the CHARM++ runtime system employs a measurementbased load balancing scheme. The load balancer automatically collects statistics on each object's computation loads and communication patterns, and using the collected load database, the runtime system decides on when and where to migrate the objects by adopting a load balancing strategy. A variety of such strategies have been developed for applications with different dynamic behaviors. Some strategies are centralized, others fully distributed. Some use only computation load when making a decision, and others take into account communication patterns and even topology of the platform. Our previous work on NAMD[43] demonstrates the significant benefits of automatic load balancing in real-life applications.

Application performance can be significantly affected by the choice of load balancing strategy and its frequency of application. In this thesis, we make use of the CHARM++ load balancing framework for two things. First, it can serve as a clear means of validating the data reduction work described in chapter 4. If in an application's run, we start with deliberate load imbalance and then fix it using an appropriate load balancing framework, any reduced dataset generated must necessarily capture the earlier load imbalance. Second, the load balancing framework in CHARM++ will serve as the instrument for re-mapping event log entries in recorded BigSim (see Section 6.2) simulation logs to test the effects of various load balancing strategies without the need to re-execute a large-scale application run. Object migration decisions by different load balancing strategies can be made using the load and communication information of the original large-scale run. These decisions can then be applied to transform BigSim event logs such that, when simulated, the performance information generated would reflect behavior as if a different load balancer had been used in the original application run.

### 2.2 The Projections Performance Analysis And Visualization Framework

The *Projections Analysis Framework* [44] consists of an instrumentation and data generation component within the CHARM++ runtime as well as a java-based visualization/analysis tool. Projections was designed to be a tool framework that supports the post-mortem and expert user-directed performance analysis of parallel applications. It's features have been used extensively to tune many CHARM++ applications in order to enhance their scalability and performance, especially NAMD [62, 44, 49].

Projections instrumentation is fully automated by default. Specifically, the runtime system knows when it is about to schedule the execution of a particular method of a particular object (in response to a message being picked up from the scheduler's queue), and when an object sends a message to another object. Default instrumentation code are written into the runtime system at these important abstraction points. When conducting performance analysis studies of applications, the instrumentation modules are invoked at these abstraction points, recording the necessary performance data into memory buffers at the cost of some time overhead. Timing data is typically recorded at microsecond resolutions. To ensure minimal performance impact in application runs, the instrumentation code overhead at these abstraction points can be reduced significantly when performance analysis is not required for that run-instance. The performance framework design can further allow overhead to be completely eliminated in fully optimized

production CHARM++ application binaries.

The recorded performance data (which can take multiple forms, see section 2.2.2) is typically written out at the end of the run. If it exhausts all the memory space allocated to it in the middle of a run, or if the user desires (e.g. at known global synchronization points), the data can be flushed to disk. In our experience, however, asynchronous flushing of log data causes such severe perturbation of application performance that the performance information after the first instance of such a flush becomes effectively useless.

### 2.2.1 Charm++ Performance Events

Gaining insight into a Charm++ application's parallel performance depends on what events are observable during execution. There are several points in the Charm++ runtime system's code base that can capture important events and information about their execution context. These include:

- 1. Start of an entry method.

- 2. End of an entry method.

- 3. Sending a message to an object.

- 4. Change in scheduler state: *active to idle* (entry method completes and no new message is available, *idle to active* (new message is available)

The first two relate directly to Charm++'s logical execution model. Observing message sends provides a runtime level perspective of object interaction. Scheduler state transitions expose resource-oriented aspects of the execution. The point is that the observation of multiple events at different abstraction levels is needed to get a full characterization of performance in a parallel language system such as Charm++.

### 2.2.2 **Projections Event Log Formats**

Projections' summary format is the most compact data format. It records processor utilization for each processor over k time intervals where k is fixed. The duration, d, of these time intervals is adjusted dynamically, doubling each time the application's execution goes past  $k \times d$ . The size of each file is dependent only on the desired number of time-intervals k. Therefore, the total size summed across all files grows in O(P) where P is the number of processors. We use runlength encoding as an additional measure to reduce the size of each file. Projections also supports an intermediate summary detail format. It employs the same dynamically adjusted time interval scheme for recording data as described above for the *summary* format. However, we record attribute information for each time interval such as the time spent or number of messages received separatedly for each CHARM++ entry method. Such a format is reasonably rich and useful for analysis, allowing a quick way to zoom in on a potential problem area. The size of each file is of the order of  $k \times E$ , where E is the number of CHARM++ entry methods in the application. However, E is relatively small, around 220 for NAMD, and depends on the static design of the application. As a result, E can be considered in practice to be a constant factor for all applications. So, the total data size grows in O(P) similar to summary files. Like the *summary* format, runlength encoding is used to reduce the size of the file.

Projections event trace logs are written in a text format with one event per line. Some events contain more details than others. For example, we record events like the start and end of each CHARM++ entry method, every time a message was sent and each time the runtime scheduler goes idle or returns from being idle. For each event, different types of attributes may be recorded. This includes the timestamp, size of a message, the CHARM++ object id, and any performance counter information (e.g. PAPI [10]) associated with the event. Recording performance counter information is optional and the default instrumentation policy has small overhead, involving a low-cost timestamp request and accessing the in-memory instrumentation log buffers.

### 2.2.3 The Projections Performance Visualization Tool

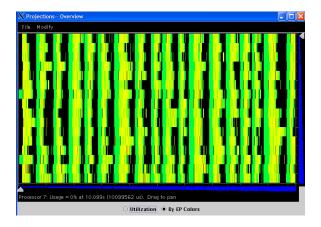

Figure 2.6: Overview: A summary of overall parallel structure.

The visualization component of the Projections framework is implemented in Java and has the advantage of being generally portable across many platforms. The trace logs generated by the instrumentation modules in the CHARM++ run-time are platform neutral with respect to visualization and analysis. Kalé et. al. [44] describes the important visualization tools provided by Projections and how they were used to support analysis processes employed by analysts to tune and optimize NAMD[62], a molecular dynamics simulation application. The rest of this section describes some of the commonly-used visualization support in order to give a flavor of what is available to our user-directed approach to post-mortem performance analysis.

Figure 2.7: Usage Profile: Processor utilization of various activities.

The overview plot of Figure 2.6 can show the dominant activity within fixed time inter-

vals along the horizontal-axis over each processor along the vertical-axis. It presents a good summary of the overall parallel structure of the application.

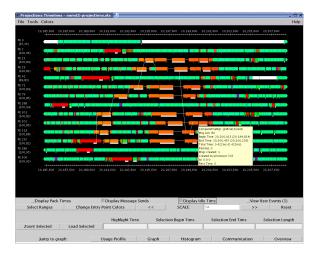

Figure 2.8: Timeline visualization of processor activity.

The *usage profile* view of Figure 2.7 displays, for each processor, the utilization percentage of all activities over a user-selected range of the application's execution time. This includes the percentage of idle time, when no useful work occurs. The left-most bar presents data averaged across all processors. This view is particularly useful for identifying the presence of load imbalance in the application, as well as its overall efficiency.

Finally, the *timeline* view in Figure 2.8 presents to the user a detailed look at the interactions between application activity and communication between processors. The horizontal time-axis marks the passage of time in the application while the vertical axis represents processors. Moving the mouse pointer over an activity pops up a small window with specific information about various performance properties of that activity (eg. number of messages sent).

### 2.2.4 The Performance Analysis Process Using Projections

The typical performance analysis process for a large-scale CHARM++ parallel application using Projections follows these general steps:

1. Instrument application if necessary.

- 2. Compile and build binaries.

- 3. Submit application to job submission queueing system.

- 4. Application generates performance data.

- 5. Use analysis idioms to find performance problems captured by the data.

- (a) Study application's overall performance profile.

- (b) Locate area in performance space with possible problems.

- (c) Restrict visualization to smaller and smaller areas of the performance space with higher levels of performance detail.

- (d) Identify specific problems, interpret and find solution in code, or back up if the problem was mis-identified at lower levels of performance detail.

- 6. Update application code given a hypothesis about the performance problem.

- 7. Validate the effectiveness of the solution. Repeat steps 2 through 5. If the solution was not effective, a new hypothesis is tested via steps 6 through 7.

In general, an iterative "drill-down" approach is adopted for performance analysis using the trace-based data generated by CHARM++ or AMPI applications. This is very similar to the way trace-based performance data from traditional MPI tools are analyzed, the key differences being the activity/event semantics and the interpretation of bottlenecks. Analysts typically have to understand the underlying code structure of the application they are trying to analyze.

# Chapter 3 Scalable Analysis