© 2007 by Gregory Allen Koenig. All rights reserved.

## EFFICIENT EXECUTION OF TIGHTLY-COUPLED PARALLEL APPLICATIONS IN GRID COMPUTING ENVIRONMENTS

#### BY

#### GREGORY ALLEN KOENIG

B.S., Indiana University-Purdue University Fort Wayne, 1993

B.S., Indiana University-Purdue University Fort Wayne, 1995

B.S., Indiana University-Purdue University Fort Wayne, 1996

M.S., University of Illinois at Urbana-Champaign, 2003

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2007

Urbana, Illinois

### Abstract

Grid computing offers a model for solving large-scale scientific problems by uniting computational resources within multiple organizations to form a single cohesive resource for the duration of individual jobs. Such an infrastructure creates a pervasive and dependable pool of computing power that enables computational scientists to develop dramatically new classes of applications. Despite the appeal of Grid computing, developing applications that run efficiently in these environments often involves overcoming significant challenges.

One challenge to deploying Grid applications across geographically distributed resources is overcoming the effects of latency between sites. Certain classes of applications, such as pipeline style or master-slave style applications, lend themselves well to running in Grid environments because the communication requirements of these types of applications can be varied readily and because most communication takes place outside the critical path. In contrast, tightly-coupled applications in which every processor performs the same task and communicates with some subset of all processors in the computation during every iteration present a significant challenge to deployment in Grid environments.

Another challenge to deploying applications in Grid environments is managing the heterogeneity that is frequently present across resources. Because supercomputing clusters in a Grid environment are often installed and upgraded independently, components such as processors and interconnects can present widely varying capabilities within a single Grid job. Tightly-coupled applications, however, especially require access to as many computational resources as possible. For example, wasting processing resources due to inefficiently mapping work to processors of heterogeneous speeds within a single Grid job is unacceptable. Likewise, intra-cluster communication should take place as much as possible using high-performance cluster interconnects, resorting to lower performance wide-area protocols only when necessary.

This thesis examines the feasibility of deploying tightly-coupled parallel applications in Grid computing environments. A desired outcome of this work is the capability of delivering application performance in a Grid environment that is on par with the performance within a single cluster while simultaneously requiring few or no modifications to application software. To that end, the thesis explores techniques that can be deployed effectively at the runtime system level and applied to a variety of application decomposition styles. Where would any of us be without teachers without people who have passion for their art or their science or their craft and love it right in front of us? What would any of us do without teachers passing on to us what they know is essential about life?

> "Mister" Fred Rogers (1928-2003)

## Acknowledgments

My introduction to parallel computing came in 1996 when I participated in the United States Department of Energy Science and Engineering Research Semester (SERS) near the end of my undergraduate education. This program allowed me to spend eight months at Argonne National Laboratory under the direction of Ian Foster. I remember being amazed at the power and complexity of large-scale parallel computers and the types of problems that they are used to solve. However, when Ian described a new software project that he and his colleagues were undertaking to unite parallel computers at a national level into computational "Grids" for solving problems of an entirely new scale, I was completely hooked. At that moment I knew that I wanted to go to graduate school to study computer science, and that I wanted to focus my studies on Grid computing. The project that Ian described to me was, of course, the Globus Toolkit which has received widespread adoption over the past decade. In the years that I have spent pursuing my graduate education, I have had several opportunities to see and interact with Ian. Each time, I have been impressed with Ian's excitement for working on challenging problems as well as his genuine enthusiasm for helping people at all levels of education learn about computer science. I know that his excitement and enthusiasm have had a huge influence on my life, and I believe that they have a huge influence on the lives of many others as well.

During my time at the University of Illinois at Urbana-Champaign, I have been richly blessed by being surrounded by a wide variety of researchers, teachers, and colleagues who have not only stimulated and challenged me intellectually, but who have also many times become very good friends. Without a doubt, my experiences at UIUC have changed my life at a very fundamental level and I will carry my memories of this place with me forever.

I was very privileged to work at the National Center for Supercomputing Applications during most of my graduate school studies. I am indebted to Rob Pennington who originally encouraged me to seek employment with NCSA and who has continued to offer kind words and helpful tips for navigating the terrain of the scientific community. My early work at NCSA took place largely within the Advanced Cluster Group. My colleagues there, including Jeremy Enos, Avneesh Pant, and Michael Showerman, were of the highest technical caliber. Avneesh Pant, especially, taught me an immense amount about cluster interconnects and writing efficient code. I also appreciate the many good times and hours of laughter I have had with the members of this group in both work and non-work environments. My later years at NCSA were spent within the Security Research Group, led by William Yurcik in conjunction with EJ Grabert. This position gave me many opportunities for technical leadership as well as several occasions to take part in workshops and conferences on an international scale. I especially thank Bill for these opportunities. Finally, Galen Arnold, a systems engineer in the NCSA consulting group, helped me many times with reservation requests for TeraGrid resources and with miscellaneous "weird" systems problems that I encountered. Galen is a consummate professional, and I was always greatly relieved when I came to the consulting office and found him working because I knew that regardless of how strange a problem I was facing, Galen would make sure that a solution was found so that I could move forward with my work.

The research-oriented portions of my graduate school studies took place within the Parallel Programming Laboratory in the Department of Computer Science at UIUC. I could not have asked for a nicer group of people with which to work. It is easy to take for granted a group like this due to the many excited students who always seem to have interesting research insights and suggestions and due to the fantastic research staff who very much streamline the day-to-day issues of conducting research. My earliest experiences in PPL were helped largely by Orion Lawlor. In more recent years, my thesis work has been greatly enhanced by technical assistance and comments from Eric Bohm, Sayantan Chakravorty, and Gengbin Zheng. Additionally, many of the figures in this thesis are due to the artistic talent of David Kunzman who transformed my crude stick-figure drawings into figures that I believe greatly enhance the quality of the manuscript.

The members of my thesis committee, Geneva Belford, Philippe Geubelle, and Steven Lumetta, represent an amazing amount of knowledge in a wide variety of computer and computational science fields such as distributed systems, finite element analysis, and cluster computing. This thesis has benefited greatly from their expertise. More than that, however, I appreciate the encouragement and enthusiasm that I have received from every member of the committee. Knowing that your committee thinks your research is "really cool" is a fantastic motivator during all-night hacking sessions!

I give special thanks to my advisor, Professor Laxmikant Kalé, who gave me a huge degree of independence in working on this project. In many ways I was not a very traditional graduate student, and his patience and ability to adapt to my style of doing research are a testament to his excellence as a teacher and researcher. Many times I would come to him with a problem, only to leave with several suggestions that I did not think could possibly help. Days or weeks later, however, I would be amazed to discover that Sanjay's insights were exactly right.

Finally, the accomplishments represented by this thesis would be nothing without the love and support of my parents, sister, and brand new niece Akya who have always encouraged me to pursue my goals in life.

## **Table of Contents**

| List of                | Tables                                        | xi        |  |

|------------------------|-----------------------------------------------|-----------|--|

| List of                | Figures                                       | xii       |  |

| Chapter 1 Introduction |                                               |           |  |

| 1.1                    | Example Grid Computing Environments           | 3         |  |

| 1.2                    | Grid Computing Challenges                     | 5         |  |

| 1.3                    | Thesis Objectives                             | 7         |  |

| Chapte                 | er 2 Enabling Technologies                    | 9         |  |

| 2.1                    | Charm++ and Adaptive MPI                      | 9         |  |

| 2.2                    | Virtual Machine Interface                     | 11        |  |

| 2.3                    | Efficient Implementation of Charm++ on VMI    | 14        |  |

| 2.4                    | Artificial Latency Environment                | 16        |  |

| Chapte                 | er 3 Related Work                             | 18        |  |

| Chapte                 | er 4 Adaptive Latency Masking                 | <b>23</b> |  |

| 4.1                    | Adaptive Latency Masking in Grid Environments | 24        |  |

| 4.2                    | Example Application: Five-Point Stencil       | 26        |  |

| 4.3                    | Summary                                       | 32        |  |

| Chapte                 | er 5 Object Mapping Strategies                | 35        |  |

| 5.1                    | Naive Mapping                                 | 35        |  |

| 5.2                    | Block Mapping                                 | 37        |  |

| 5.3                    | Summary                                       | 53        |  |

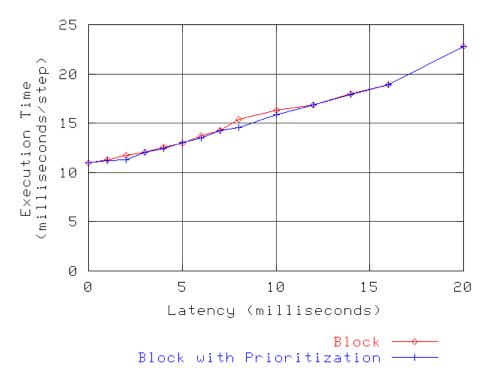

| Chapte                 | er 6 Object Prioritization                    | <b>54</b> |  |

| 6.1                    | Object Prioritization Technique               | 54        |  |

| 6.2                    | Implementation Details                        | 55        |  |

| 6.3                    | Performance Evaluation                        | 60        |  |

| 6.4                    | Limitations                                   | 71        |  |

| 6.5                    | Summary                                       | 72        |  |

| Chapte          | er 7 Grid Topology-Aware Load Balancing                                                                                               | <b>74</b> |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| 7.1             | Basic Grid Communication Load Balancing                                                                                               | 76        |  |  |  |

|                 | 7.1.1 Load Balancer Technique                                                                                                         | 76        |  |  |  |

|                 | 7.1.2 Implementation Details                                                                                                          | 77        |  |  |  |

|                 | 7.1.3 Performance Evaluation                                                                                                          | 81        |  |  |  |

|                 | 7.1.4 Overhead                                                                                                                        | 90        |  |  |  |

|                 | 7.1.5 Limitations $\ldots$                           | 90        |  |  |  |

| 7.2             | Graph Partitioning Load Balancing                                                                                                     | 92        |  |  |  |

|                 | 7.2.1 Load Balancing Technique                                                                                                        | 92        |  |  |  |

|                 | 7.2.2 Implementation Details                                                                                                          | 93        |  |  |  |

|                 | 7.2.3 Performance Evaluation                                                                                                          | 97        |  |  |  |

|                 | 7.2.4 Overhead                                                                                                                        | 07        |  |  |  |

|                 | 7.2.5 Limitations $\ldots \ldots 1$ | .07       |  |  |  |

| 7.3             | Hybrid Load Balancing                                                                                                                 | 10        |  |  |  |

|                 | 7.3.1 Load Balancer Technique                                                                                                         | 10        |  |  |  |

|                 | 7.3.2 Implementation Details                                                                                                          | 12        |  |  |  |

|                 | 7.3.3 Performance Evaluation                                                                                                          | 14        |  |  |  |

|                 | 7.3.4 Overhead                                                                                                                        | 24        |  |  |  |

|                 | 7.3.5 Limitations $\ldots \ldots 1$ | 24        |  |  |  |

| 7.4             | Summary                                                                                                                               | 25        |  |  |  |

|                 |                                                                                                                                       | • •       |  |  |  |

| Chapte          |                                                                                                                                       | 28        |  |  |  |

| 8.1             | 1                                                                                                                                     | .29       |  |  |  |

|                 | J                                                                                                                                     | .29       |  |  |  |

|                 |                                                                                                                                       | .30       |  |  |  |

| 8.2             |                                                                                                                                       | .31       |  |  |  |

|                 |                                                                                                                                       | .31       |  |  |  |

|                 | $\mathcal{J}$                                                                                                                         | .33       |  |  |  |

|                 |                                                                                                                                       | .36       |  |  |  |

| 8.3             | v                                                                                                                                     | .39       |  |  |  |

|                 |                                                                                                                                       | .39       |  |  |  |

|                 | v                                                                                                                                     | 40        |  |  |  |

| <b>a</b> 4      |                                                                                                                                       | .44       |  |  |  |

| 8.4             | Summary                                                                                                                               | .46       |  |  |  |

| Chapte          | er 9 Conclusion                                                                                                                       | 48        |  |  |  |

| Refero          | References                                                                                                                            |           |  |  |  |

| IUICICICI       |                                                                                                                                       |           |  |  |  |

| Curriculum Vitæ |                                                                                                                                       |           |  |  |  |

## List of Tables

| 6.1 | Performance of Jacobi2D 2048x2048 object prioritization with 8 processors  |     |

|-----|----------------------------------------------------------------------------|-----|

|     | and 64 objects                                                             | 63  |

| 6.2 | Performance of Jacobi2D 2048x2048 object prioritization with 16 processors |     |

|     | and 64 objects                                                             | 66  |

| 6.3 | Performance of Jacobi2D 2048x2048 object prioritization with 32 processors |     |

|     | and 256 objects                                                            | 68  |

| 6.4 | Performance of Jacobi2D 8192x8192 object prioritization with 16 processors |     |

|     | and 64 objects                                                             | 70  |

| 6.5 | Performance of Jacobi2D 8192x8192 object prioritization with 64 processors |     |

|     | and 256 objects                                                            | 71  |

| 7.1 | Overhead of the basic load balancing technique in GridCommLB               | 91  |

| 7.2 | Overhead of the graph partitioning load balancing technique in GridMetisLB | 108 |

| 7.3 | Overhead of the hybrid load balancing technique in GridHybridLB            | 125 |

|     |                                                                            |     |

| 8.1 | Performance comparison of LeanMD in artificial latency environment and     |     |

|     | TeraGrid environment (NCSA-ANL)                                            | 137 |

| 8.2 | Performance comparison of LeanMD in artificial latency environment and     |     |

|     | TeraGrid environment (NCSA-SDSC)                                           | 138 |

| 8.3 | Performance comparison of Fractography3D in artificial latency environment |     |

|     | and TeraGrid environment (NCSA-ANL)                                        | 145 |

| 8.4 | Performance comparison of Fractography3D in artificial latency environment |     |

|     | and TeraGrid environment (NCSA-SDSC)                                       | 146 |

## List of Figures

| $1.1 \\ 1.2$ | Example of an application co-allocated across two clusters                         | $\frac{2}{5}$ |

|--------------|------------------------------------------------------------------------------------|---------------|

| 2.1          | Depiction of the user's view of a Charm++ application and the system's view        |               |

|              | after mapping objects to processors                                                | 10            |

| 2.2          | Structure of the efficient implementation of Charm++ on VMI $\ldots \ldots \ldots$ | 15            |

| 4.1          | Hypothetical timeline illustrating the use of message-driven objects to tolerate   |               |

|              | wide-area latency                                                                  | 25            |

| 4.2          | Execution time of a parallel application as a function of grainsize $[23]$         | 27            |

| 4.3          | Graphical depiction of a five-point stencil decomposition in which a fixed         |               |

|              | number of cells are divided across a variable number of objects                    | 28            |

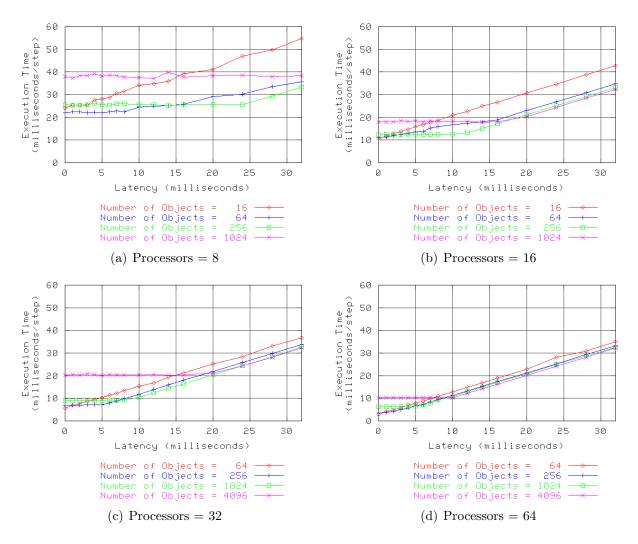

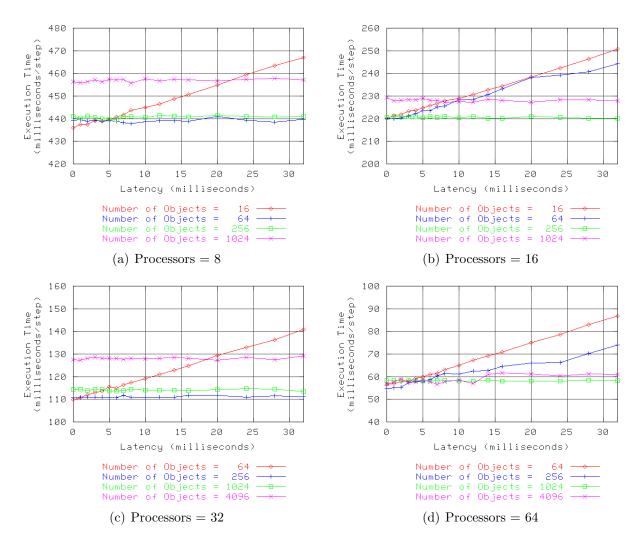

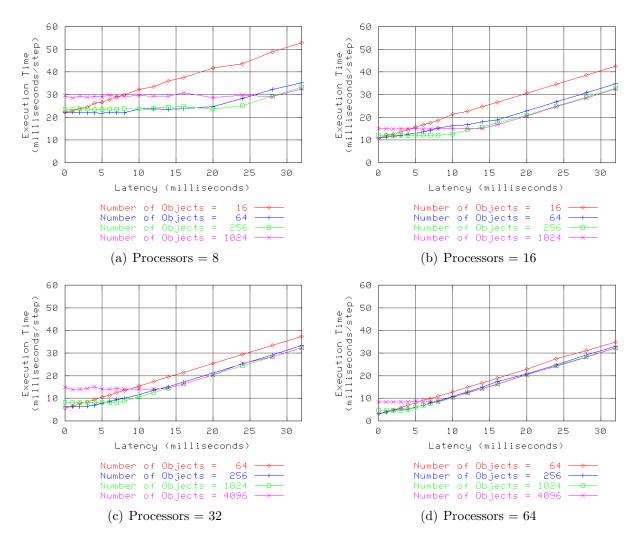

| 4.4          | Performance of Jacobi2D 2048x2048 with Naive object mapping                        | 30            |

| 4.5          | Performance of Jacobi2D 8192x8192 with Naive object mapping                        | 33            |

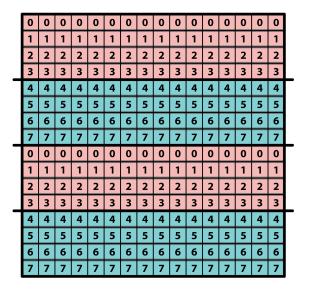

| 5.1          | Naive object mapping for 256 objects mapped onto 8 processors                      | 36            |

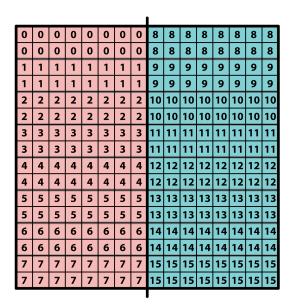

| 5.2          | Naive object mapping for 256 objects mapped onto 16 processors                     | 37            |

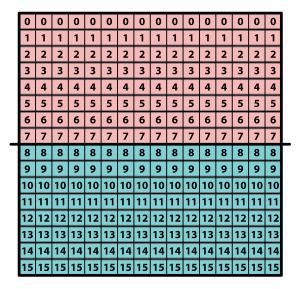

| 5.3          | Block object mapping for 256 objects mapped onto 8 processors                      | 38            |

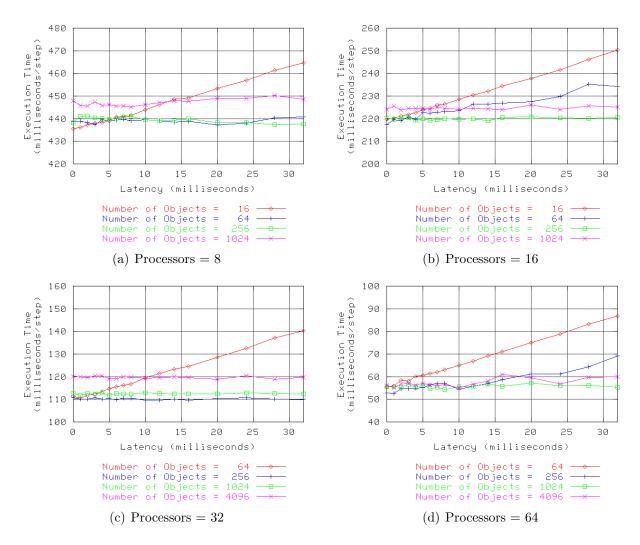

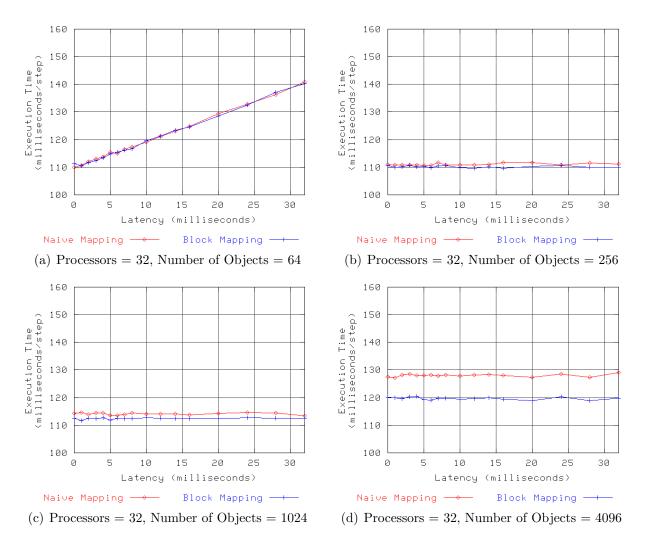

| 5.4          | Performance of Jacobi2D 2048x2048 with Block object mapping                        | 40            |

| 5.5          | Performance of Jacobi2D 8192x8192 with Block object mapping                        | 41            |

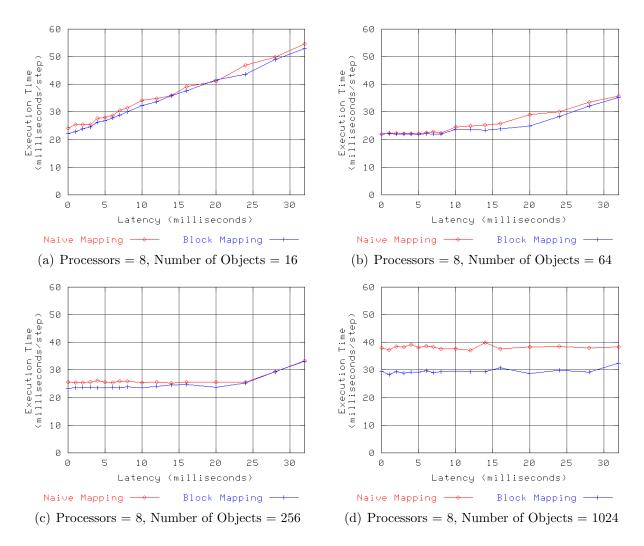

| 5.6          | Performance comparison of Jacobi2D 2048x2048 Naive object mapping vs.              |               |

|              | Block object mapping (8 processors)                                                | 44            |

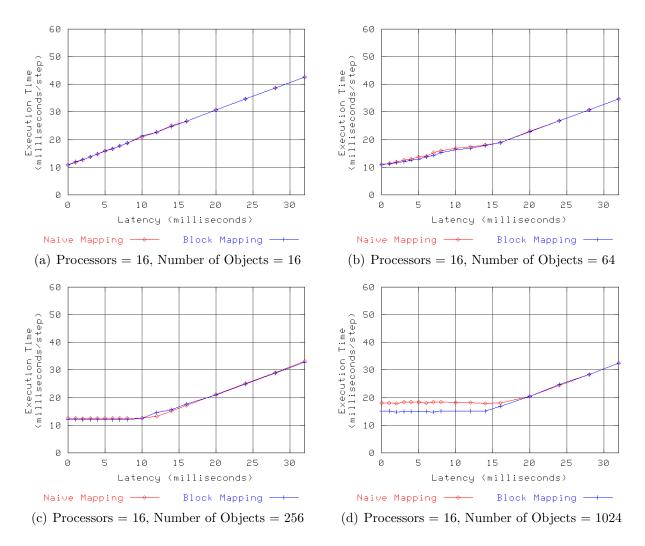

| 5.7          | Performance comparison of Jacobi2D 2048x2048 Naive object mapping vs.              |               |

|              | Block object mapping (16 processors)                                               | 45            |

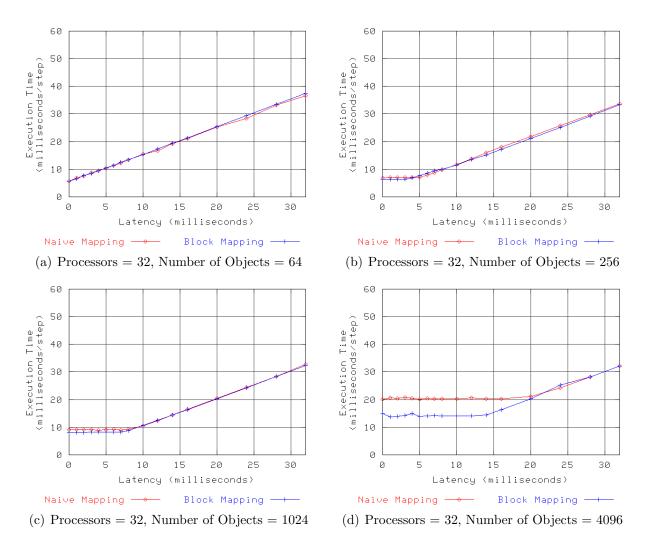

| 5.8          | Performance comparison of Jacobi2D 2048x2048 Naive object mapping vs.              |               |

|              | Block object mapping (32 processors)                                               | 46            |

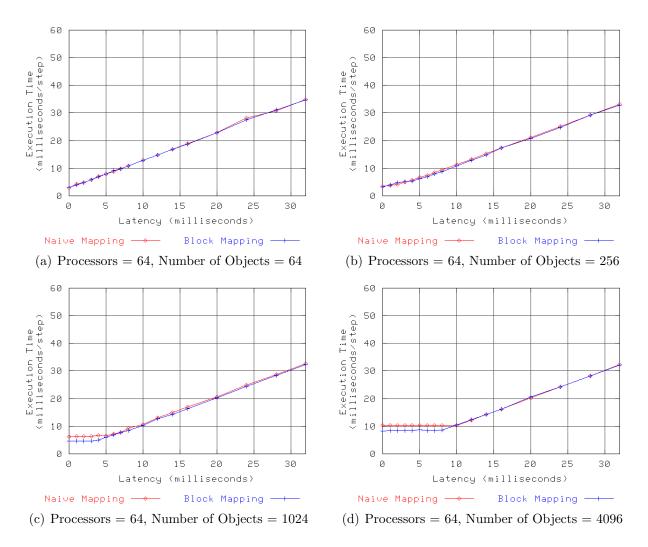

| 5.9          | Performance comparison of Jacobi2D 2048x2048 Naive object mapping vs.              |               |

|              | Block object mapping (64 processors)                                               | 47            |

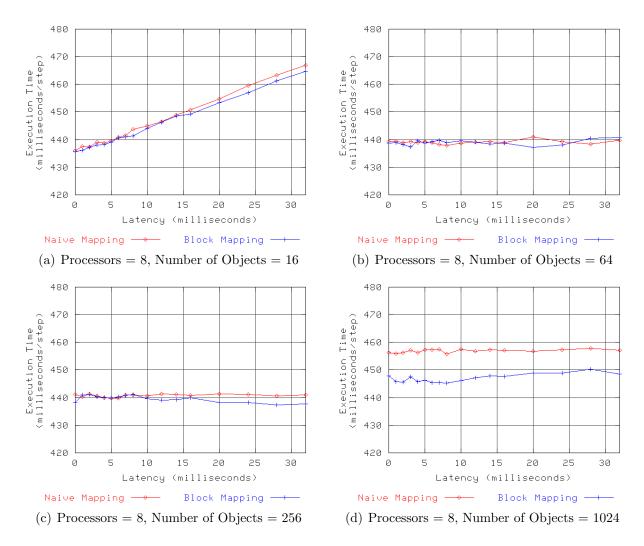

| 5.10         |                                                                                    |               |

|              | Block object mapping (8 processors)                                                | 49            |

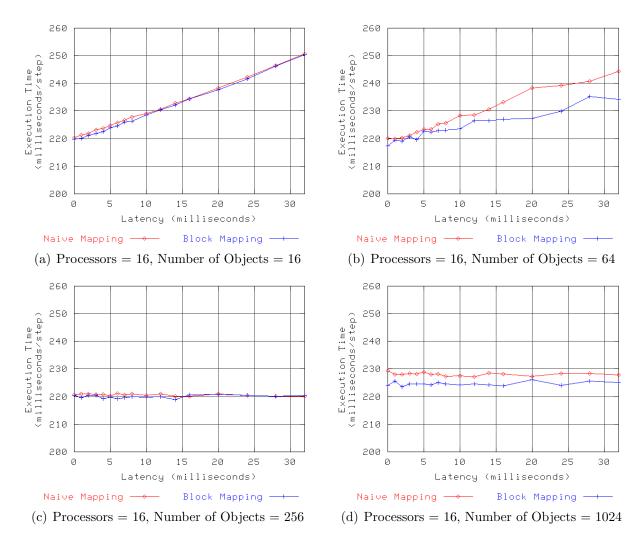

| 5.11         | Performance comparison of Jacobi2D 8192x8192 Naive object mapping vs.              |               |

|              | Block object mapping (16 processors)                                               | 50            |

| 5.12         | Performance comparison of Jacobi2D 8192x8192 Naive object mapping vs.              |               |

|              | Block object mapping (32 processors)                                               | 51            |

| 5.13 Performance comparison of Jacobi2D 8192x8192 Naive object mapping vs.<br>Block object mapping (64 processors) | 52  |

|--------------------------------------------------------------------------------------------------------------------|-----|

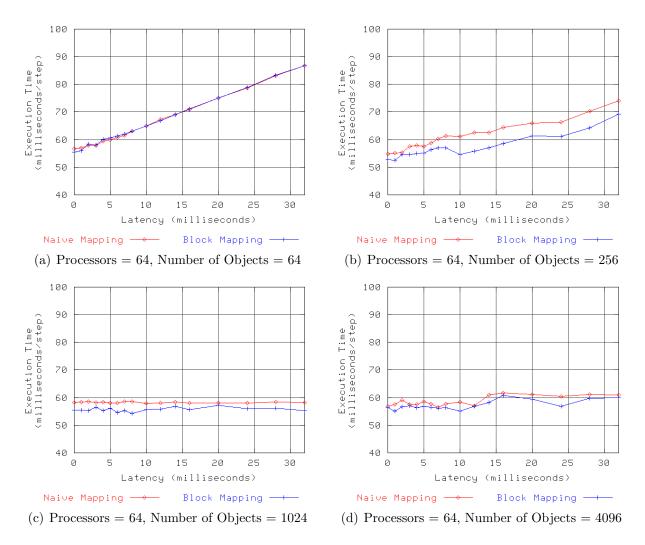

| <ul><li>6.1 Example of border object prioritization</li></ul>                                                      | 58  |

| processors and 64 objects                                                                                          | 66  |

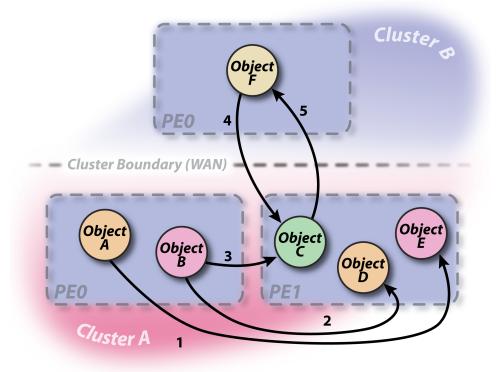

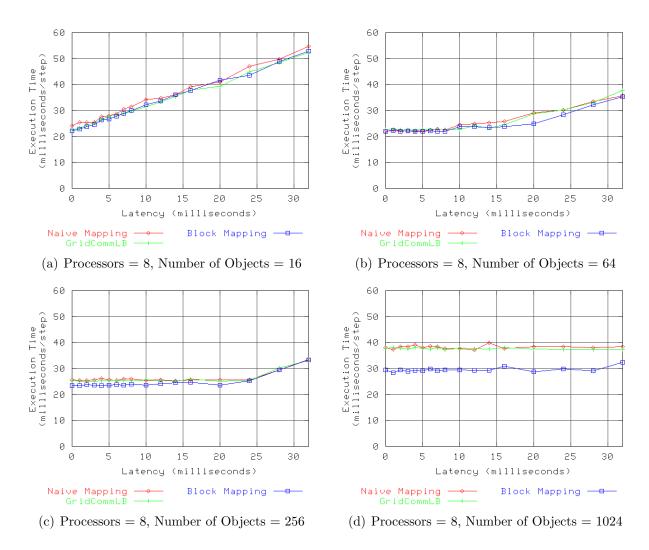

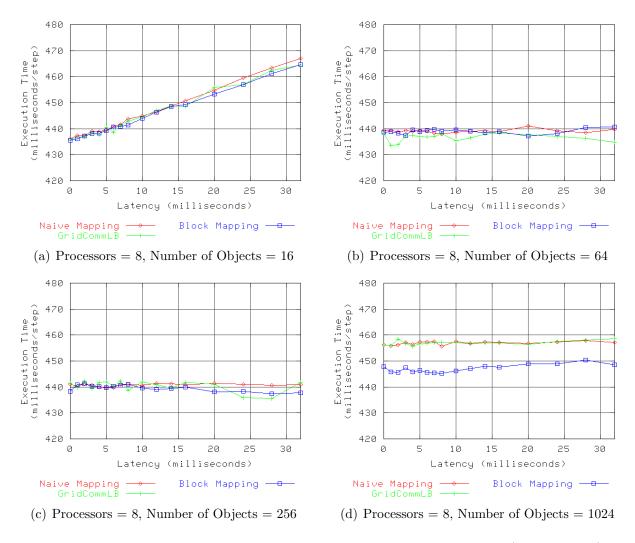

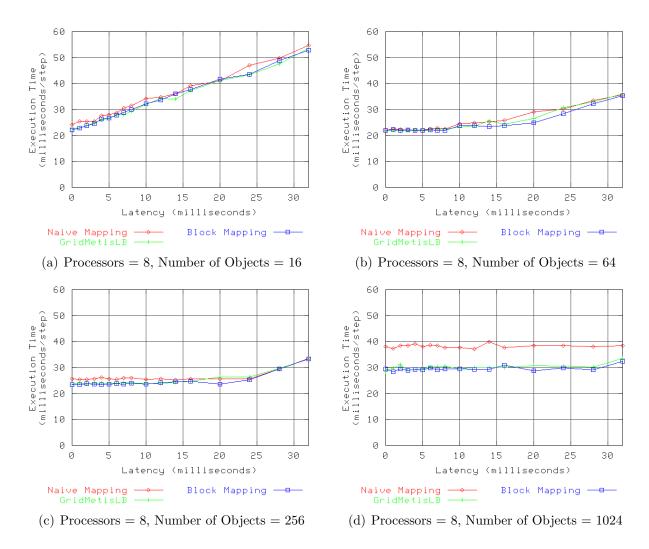

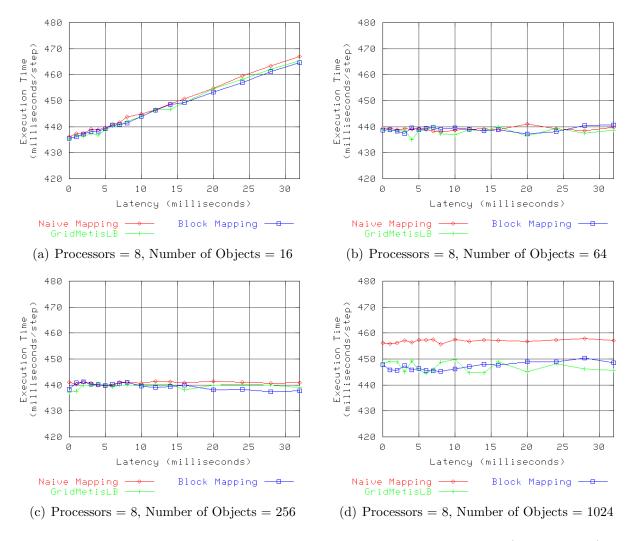

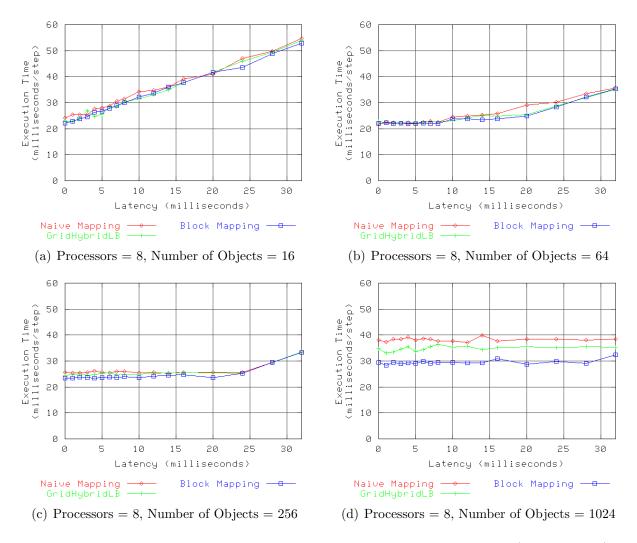

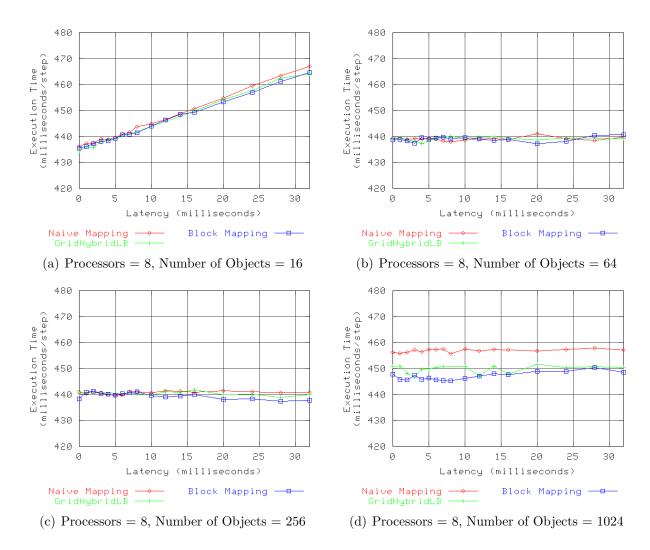

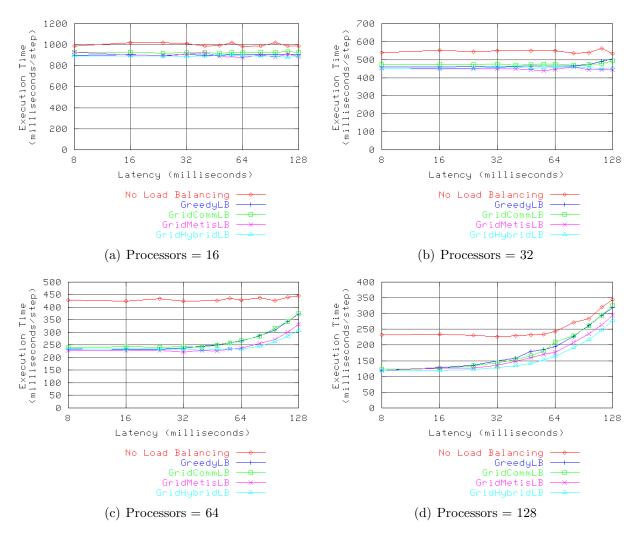

| 7.1 Performance of Jacobi2D 2048x2048 with GridCommLB (8 processors)                                               | 82  |

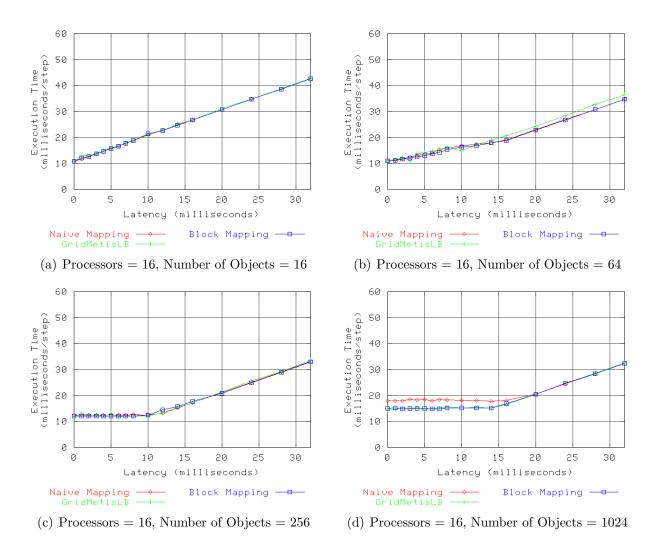

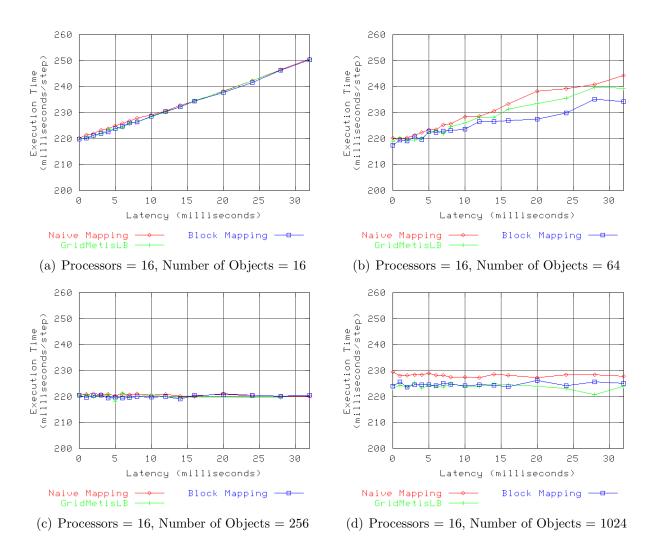

| 7.2 Performance of Jacobi2D 2048x2048 with GridCommLB (16 processors)                                              | 83  |

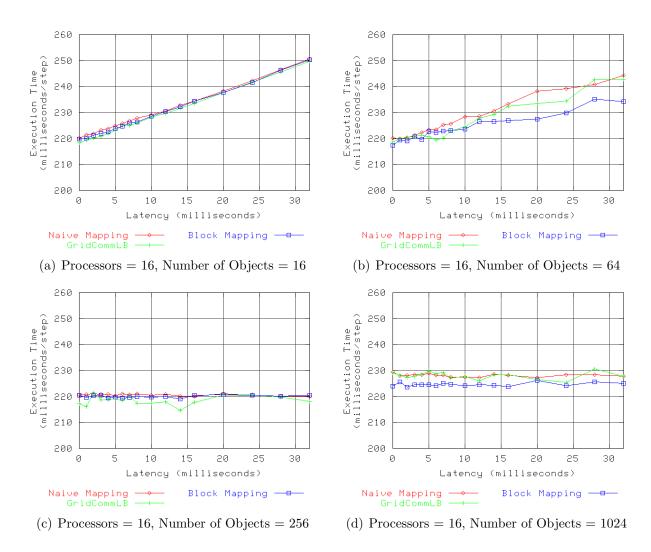

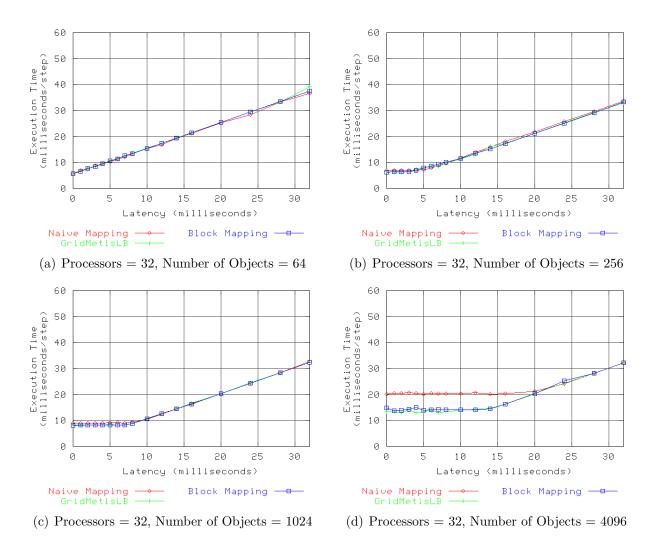

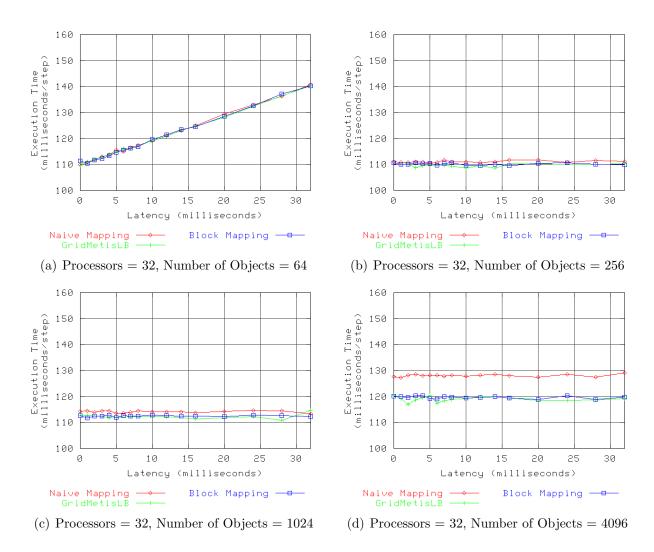

| 7.3 Performance of Jacobi2D 2048x2048 with GridCommLB (32 processors)                                              | 84  |

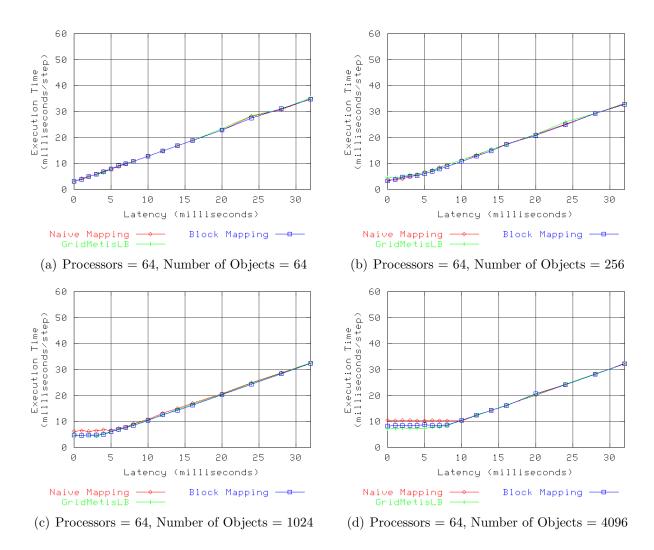

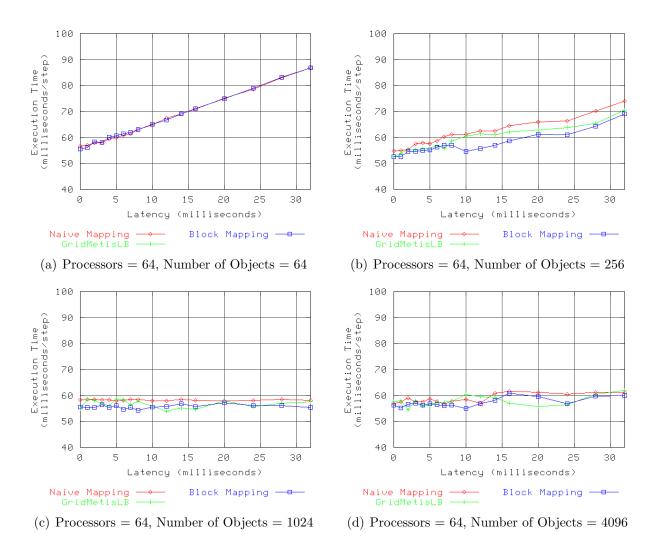

| 7.4 Performance of Jacobi2D 2048x2048 with GridCommLB (64 processors)                                              | 85  |

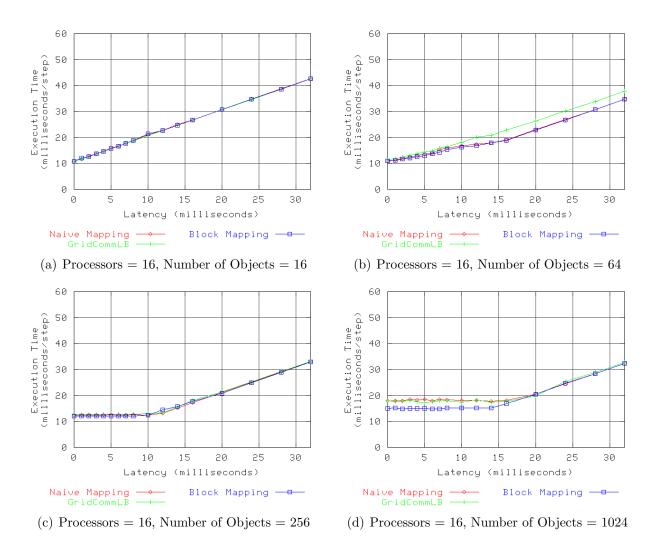

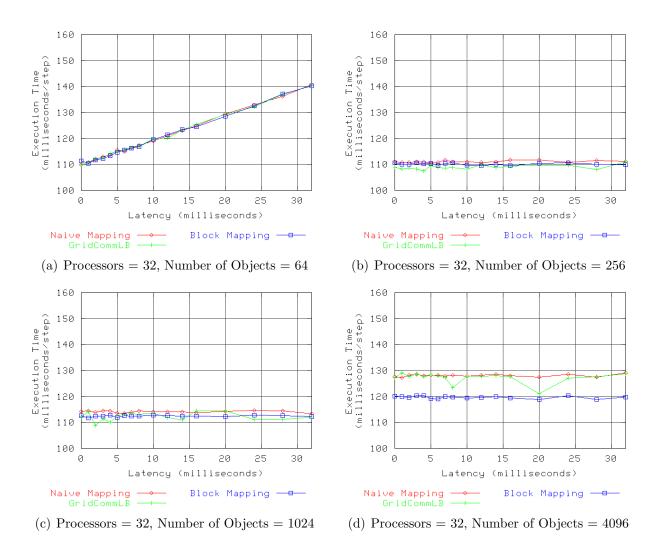

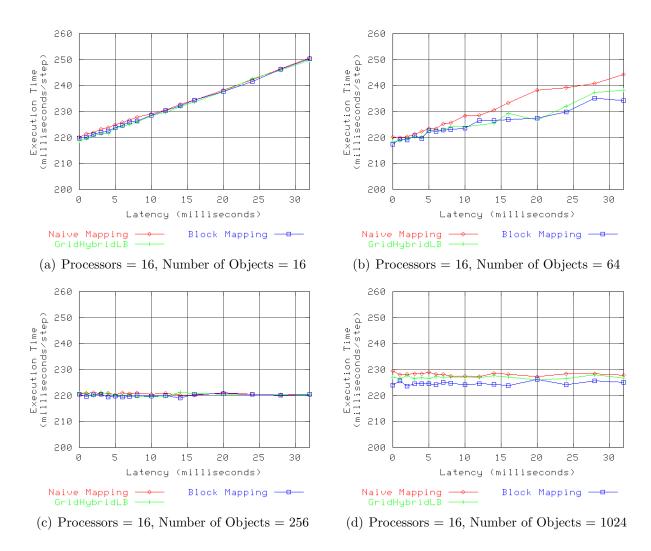

| 7.5 Performance of Jacobi2D 8192x8192 with GridCommLB (8 processors)                                               | 86  |

| 7.6 Performance of Jacobi2D 8192x8192 with GridCommLB (16 processors)                                              | 87  |

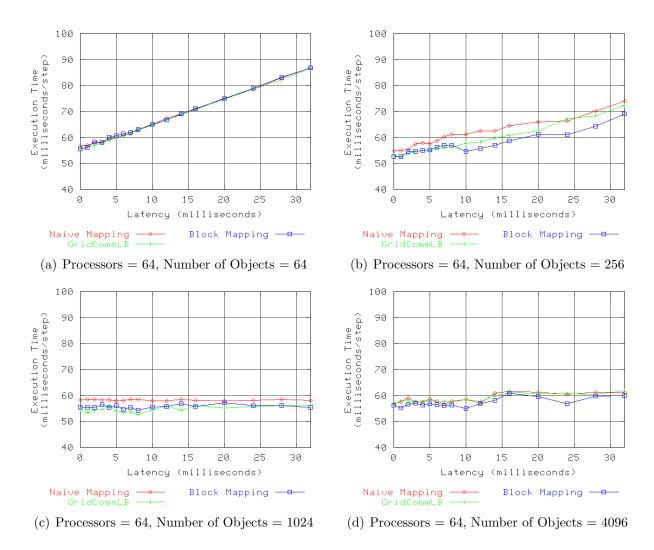

| 7.7 Performance of Jacobi2D 8192x8192 with GridCommLB (32 processors)                                              | 88  |

| 7.8 Performance of Jacobi2D 8192x8192 with GridCommLB (64 processors)                                              | 89  |

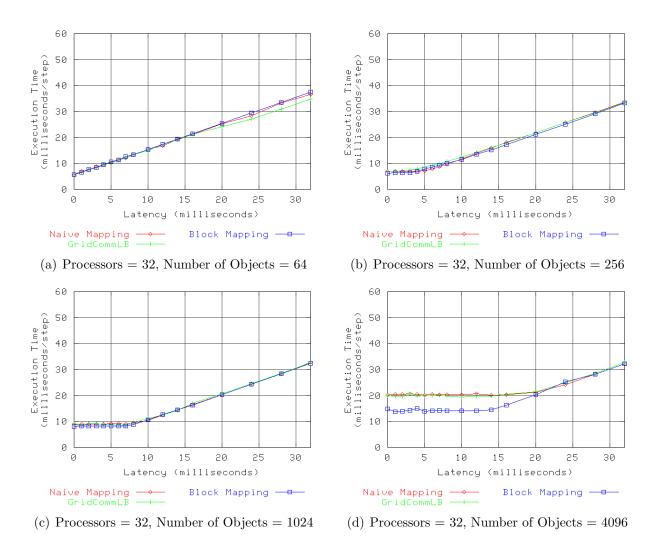

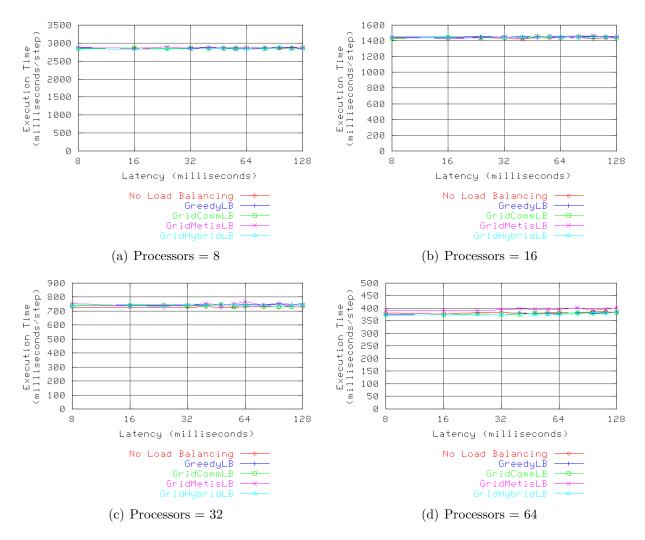

| 7.9 Performance of Jacobi2D 2048x2048 with GridMetisLB (8 processors)                                              | 99  |

| 7.10 Performance of Jacobi2D 2048x2048 with GridMetisLB (16 processors) $\ldots$                                   | 100 |

| 7.11 Performance of Jacobi2D 2048x2048 with GridMetisLB (32 processors) $\ldots$                                   | 101 |

| 7.12 Performance of Jacobi2D 2048x2048 with GridMetisLB (64 processors) $\ldots$                                   | 102 |

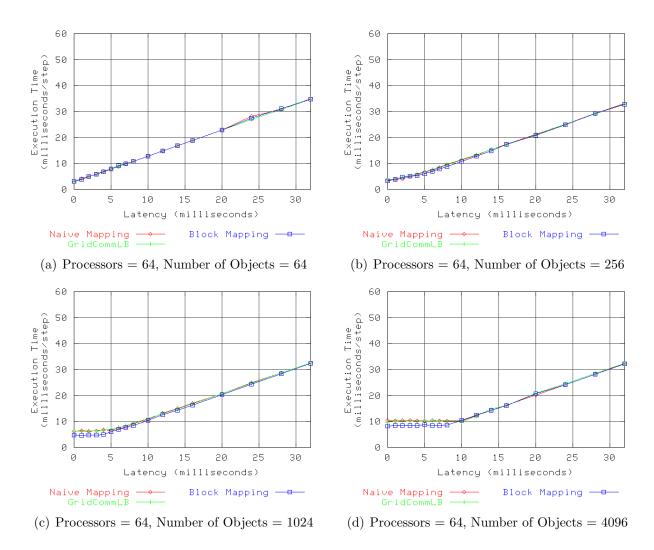

| 7.13 Performance of Jacobi2D 8192x8192 with GridMetisLB (8 processors)                                             | 103 |

| 7.14 Performance of Jacobi2D 8192x8192 with GridMetisLB (16 processors) $\ldots$                                   | 104 |

| 7.15 Performance of Jacobi2D 8192x8192 with GridMetisLB (32 processors) $\ldots$                                   | 105 |

|                                                                                                                    | 106 |

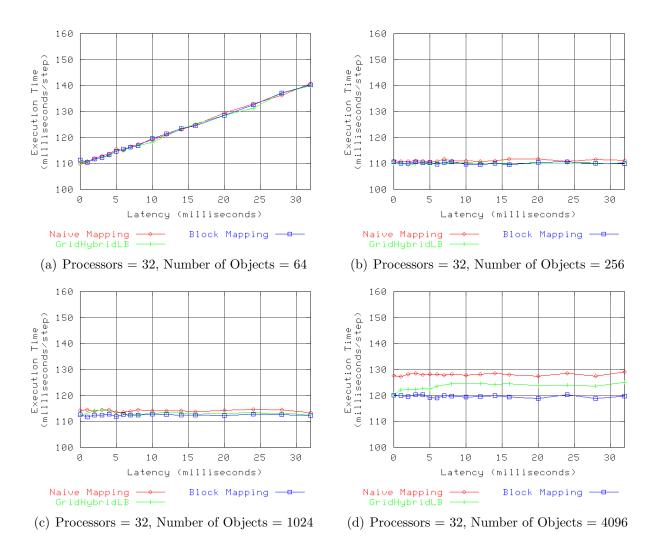

|                                                                                                                    | 116 |

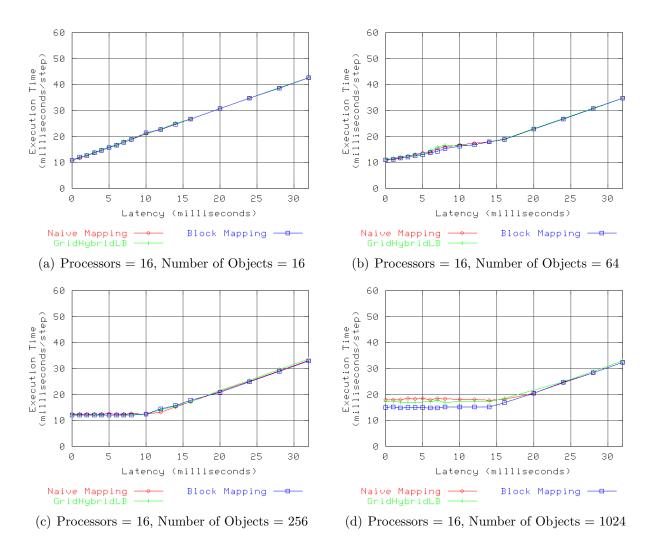

| 7.18 Performance of Jacobi2D 2048x2048 with GridHybridLB (16 processors) $\therefore$                              | 117 |

|                                                                                                                    | 118 |

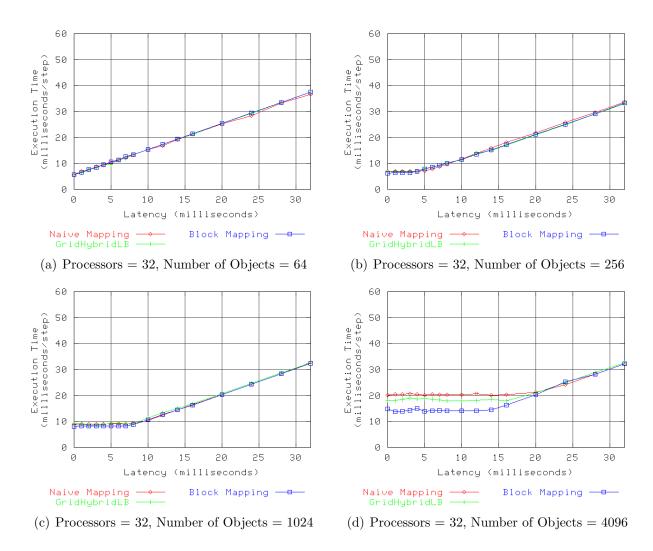

|                                                                                                                    | 119 |

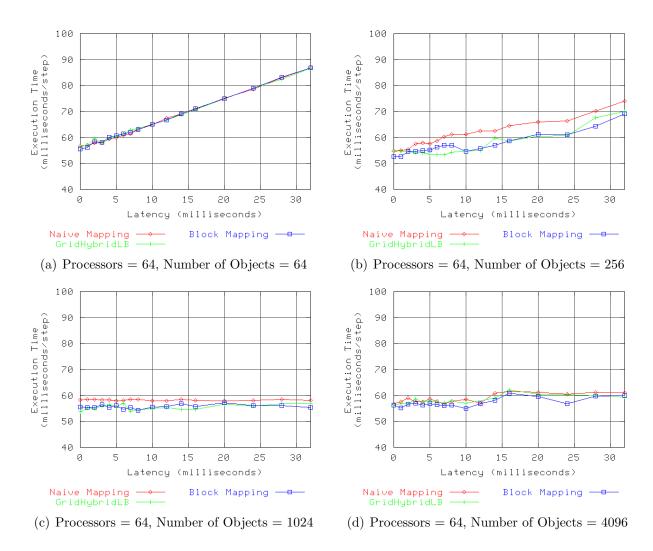

|                                                                                                                    | 120 |

|                                                                                                                    | 121 |

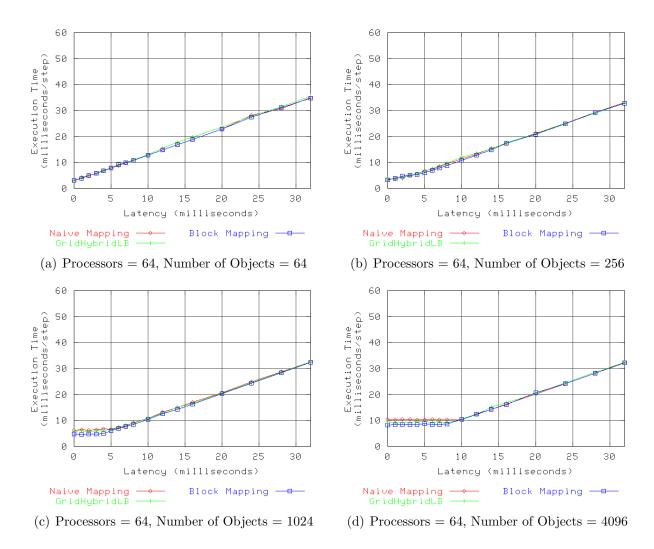

|                                                                                                                    | 122 |

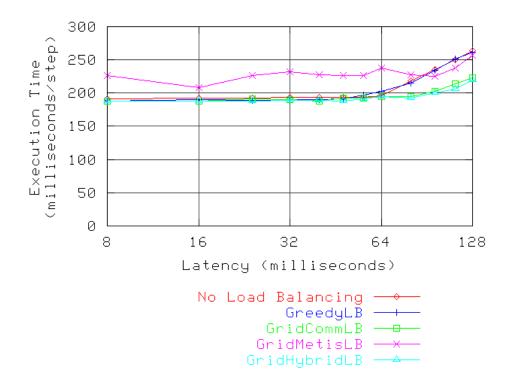

| 7.24 Performance of Jacobi2D 8192x8192 with GridHybridLB (64 processors) $$ .                                      | 123 |

| 8.1 Performance of LeanMD                                                                                          | 133 |

| 8.2 Performance of Fractography3D                                                                                  | 142 |

| 8.3 Performance of Fractography3D on 128 processors                                                                | 144 |

# Chapter 1 Introduction

Due to the growth of distributed Grid computing technologies and environments over the past several years [11, 12], consumers of high performance computing cycles are increasingly considering the feasibility of deploying applications that span multiple geographically distributed sites. Software such as the Globus Toolkit [10] allows the creation of so-called "virtual organizations" in which computational resources owned by multiple physical organizations are united to form a single cohesive resource for the duration of a single computational job. For example, an application could collect data from scientific devices at two different sites, perform a computation with the combined data on a supercomputing cluster at a third site, and display the results of the computation with visualization tools and equipment at a fourth site.

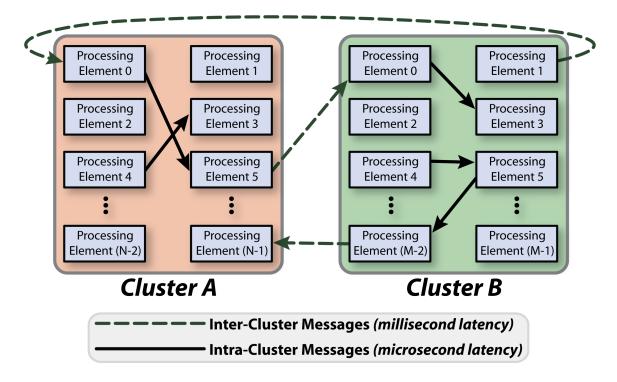

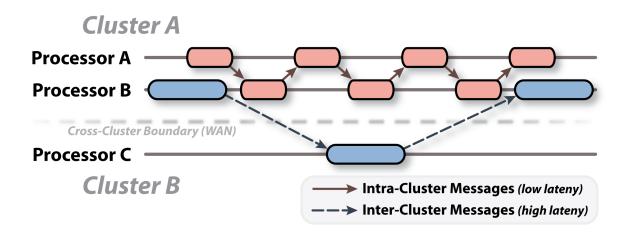

Despite the appeal of Grid computing, however, developing applications that can run efficiently in Grid environments often involves significant challenges. One fundamental challenge to deploying Grid applications across geographically distributed computational resources is overcoming the effects of the wide-area latency between sites. While the interconnects used in contemporary supercomputers and high-performance clusters can deliver data to applications with latencies on the order of a few microseconds, latencies across the wide-area are usually measured in milliseconds. Figure 1.1 illustrates this idea. Certain classes of applications lend themselves well to running in such an environment. Pipeline style applications, such as those that do simulation on one cluster and visualization on another, for example, involve one-way dependencies that help them tolerate cross-site latency. Master-slave style applications are also good candidates for Grid environments because they typically have

Figure 1.1: Example of an application co-allocated across two clusters

small communication requirements and because communication delays are often not on the critical path.

Another challenge to deploying applications in Grid computing environments is managing the heterogeneity that is frequently present across resources. Because clusters in a Grid environment are often installed and upgraded independently of one another, components such as processors and cluster interconnects can present widely varying capabilities within the context of a single Grid job. For example, the processors allocated to a Grid job from one cluster may be twice as fast as the processors from a second cluster. Or, one cluster may use Myrinet for high performance intra-cluster message passing while another cluster uses InfiniBand; inter-cluster messages would be transmitted via lower performance communication mechanisms such as TCP/IP. As above, pipeline style applications work well in these types of heterogeneous environments due to fact that the discrete pieces of software that compose the pipeline application each typically reside within, and do not extend beyond, the boundary of a single cluster, thus greatly limiting the effects of heterogeneity. Similarly, master-slave style applications also work well in heterogeneous environments because each slave works independently, returning results as fast as it is capable and communicating minimally with other slaves.

In contrast, some classes of applications present serious challenges to deployment in Grid computing environments. Tightly-coupled applications in which every processor in a computation performs the same task and communicates with some subset of all processes in the computation during every iteration present a significant challenge. Examples of such applications include most simulations of physical systems in science and engineering, for example structured and unstructured mesh applications and applications from domains such as molecular dynamics or cosmology in which elements in a three-dimensional space interact with all other elements within a specified cutoff distance. Optimizing these types of applications through techniques such as masking the effects of wide-area latency and managing the heterogeneity of resources is critical for achieving good performance in Grid environments. To date, however, much of the work involving the deployment of tightly-coupled applications on computational Grids has focused on algorithm-level optimizations, such as the expansion of ghost zone regions in mesh computations [8].

#### **1.1 Example Grid Computing Environments**

The rapid growth in the use of Grid computing for solving large-scale scientific problems is driven by a number of developments in several related and overlapping areas. For example, the recent trend in building computational clusters from commodity off-the-shelf components has resulted in a proliferation of dispersed pockets of significant computational power owned by individual organizations. Connecting these dispersed pockets of computational power is a natural next step. Developments of this nature set important directions and guidelines for research like that presented in this thesis. To that end, the following two examples highlight environments in which the work presented in this thesis might be applied directly.

The first example environment in which the work described in this thesis might be applicable is that of a circumscribed campus-area network. Due to the increasing use of cluster computing, individual departments are now able to afford to own not-insignificant amounts of computational power which are leveraged towards unique departmental goals. However, the sizes of these departmentally-owned computational resources are often limited either by the availability of funding or by the infeasibility of purchasing clusters that far exceed the expected steady-state cycle needs of the department. One can envision a situation in which two collaborating departments on the same campus might want to join their individuallyowned cluster resources together for the purpose of solving occasional very large problems. Certain challenges to Grid computing are not as severe in this type of environment. Because communication is generally limited to a campus-area network, cross-cluster latencies in a Grid computing environment of this nature are typically on the order of one to three milliseconds. While this is still bad compared to the microsecond-scale latencies within a single cluster, latencies of this scale are much more easily masked than the latencies in national scale Grid environments where latencies are measured in tens of milliseconds. On the other hand, other challenges to Grid computing might be very obvious in this type of environment. For example, because individual departments often purchase clusters independently, issues of heterogeneity, in terms of processor speeds or communication interconnects, might be difficult to manage.

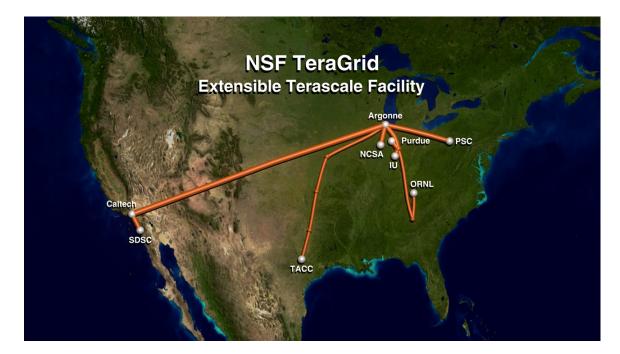

The second example environment in which the work described in this thesis might be applicable is that of established Grid computing environments such as the TeraGrid [1]. The TeraGrid is a multi-year effort, led by the National Science Foundation and involving nine core sites distributed across the United States, to build and deploy the world's largest and fastest Grid computing environment available for open scientific research. The core TeraGrid includes over one hundred teraflops of computational power and over fifteen petabyte of disk storage, interconnected with a forty-gigabit-per-second national network. Figure 1.2 shows a map of the core TeraGrid infrastructure. Such an environment presents different challenges

Figure 1.2: Map of the NSF TeraGrid Extensible Terascale Facility core sites [1]

from ones described in the example of a campus-area network. Because the TeraGrid is a joint effort among several collaborating sites with the express purpose of fostering Grid computing, issues such as heterogeneity have been kept to a minimum, particularly in the context of the original core TeraGrid resources. On the other hand, because the TeraGrid environment spans the United States, overcoming challenges such as cross-site latencies measured in tens of milliseconds becomes critical when optimizing tightly-coupled application performance.

### 1.2 Grid Computing Challenges

Viewing Grid computing in the contexts described above is useful because it allows the challenges to efficiently executing tightly-coupled parallel applications in such environments to be identified. This section specifically states several of these challenges.

• Wide-area communication costs – In environments consisting of resources separated by large geographic distances, such as in the case of the TeraGrid, the efficiency of communication taking place over the wide-area is a critical factor to consider when optimizing application performance. Two issues related to communication costs are important: bandwidth and latency. Of these two issues, latency seems to be the more challenging. Challenges involving bandwidth may often be resolved simply by building a more capable infrastructure that can deliver more bandwidth to applications. For example, the backbone connections in the TeraGrid bond four ten-gigabit-per-second channels together to deliver forty gigabits-per-second. It seems likely that if, in the future, applications demand additional bandwidth to feasibly run on the TeraGrid, that additional bandwidth could be requisitioned. Latency, on the other hand, has a lower bound between any two points on the TeraGrid due to the simple physics of nature; light only travels so fast.

• Efficient mapping of work to resources – Some success has been made in using algorithm-specific optimizations for achieving good performance of various types of tightly-coupled problems in Grid computing environments. Work representative of these efforts is described in Chapter 3. A downside of this type of approach is that these types of optimizations may be quite complex for a programmer to implement correctly. Further, optimizations of this nature may lead to optimizing an application specifically for a particular Grid environment, requiring frustrating modifications to the optimized implementation in order to move it to a different Grid environment at a later time. For example, consider an unstructured mesh decomposition specifically coded to map work evenly among two clusters in a Grid. In contrast to applications such as master-slave decompositions in which work can readily be parceled out to available processors, manually partitioning an unstructured mesh for efficient execution over a Grid is non-trivial due to the complexities involved in locating good division points in the mesh that result in approximately-equal work on both clusters while simultaneously minimizing communication costs between the clusters. Further, the manual mapping of work must be changed if, in the future, changes are made to the environment in which the application runs, such as by upgrading the nodes in one cluster to be of a faster speed, requiring more work to be mapped to these processors relative to the slower processors in the other cluster, or by introducing a third cluster across which the application is mapped.

- Dynamic environment By their very nature, Grid computing environments are extremely dynamic. For example, latencies between parts of a computation may increase or decrease depending on other competing network traffic. Effectively dealing with the issues surrounding this dynamic nature of Grids is crucial for achieving good application performance. Optimizing applications to run efficiently in response to these challenges is difficult because it requires software to be able to adaptively tune application performance at runtime.

- Pervasive heterogeneity Many Grid computing environments, such as those composed of organizations that combine resources "after the fact" of purchasing equipment independently, contain pervasive heterogeneity. This is in contrast to proscribed Grid environments like the core TeraGrid which are developed specifically to minimize issues of heterogeneity. In the environments, heterogeneity in the form of processors of different speeds and capabilities as well as multiple types of cluster interconnects (e.g., Myrinet and InfiniBand) will be common. To achieve maximum performance of tightly-coupled codes running in such an environment, this heterogeneity needs to be managed.

### **1.3** Thesis Objectives

The objective of this thesis is to examine the feasibility of deploying tightly-coupled parallel applications in Grid computing environments. A desired outcome of this work is the capability of delivering application performance in a Grid environment that is on par with the performance within a single cluster while at the same time requiring few or no modifications to the application software. To that end, the thesis explores techniques that can be deployed effectively at the runtime system (middleware) level and used in a Grid computing environment consisting of multiple clusters. Such techniques include capabilities for efficiently mapping work to the resources allocated to a Grid application and dynamically updating this mapping in light of short-term changes in these resources (e.g., a sudden and unexpected increase in latency between two clusters across which a Grid job is co-allocated). Additional techniques address issues related to the heterogeneity found in a Grid environment, such as by providing abstractions to the various interconnects used throughout all resources in a Grid job or by partitioning a Grid job to reflect processors of different speeds or capabilities. An advantage of developing these techniques within the runtime system is that they are automatically available to applications representing a wide variety of problem decomposition strategies with little or no effort required by application developers. This enables application developers to focus on the underlying problem, writing a software solution in the most straightforward way possible, without being concerned with details of the Grid environment in which the application will be deployed.

This thesis promotes a message-driven programming model for developing Grid applications. A message-driven model, as realized in systems such as Charm++ [21] and Adaptive MPI [20], is attractive for use in Grid computing because it encourages a development style in which an application is broken into a large number of parallel migratable objects which are subsequently mapped onto a much smaller number of physical processors by an adaptive runtime system. The runtime system can provide features such as message prioritization and dynamic load balancing, allowing the runtime system to optimize a computation during execution. A message-driven runtime system architecture coupled with optimization capabilities allows an application to be feasibly deployed in Grid environments consisting of several clusters that are made up of processors of various speeds and utilizing multiple network interconnects.

# Chapter 2 Enabling Technologies

This chapter describes the enabling technologies upon which the work in this thesis is based. These technologies include the Charm++ and Adaptive MPI runtime systems and the software surrounding them as well as the Virtual Machine Interface message passing layer.

#### 2.1 Charm++ and Adaptive MPI

Charm++ [21] is a message-driven parallel programming language based on C++ and designed with the goal of enhancing programmer productivity by providing a high-level abstraction of a parallel computation while at the same time providing good performance on platforms ranging from traditional supercomputers to more recent commodity cluster environments. Charm++ is backed by an adaptive runtime system that provides features such as processor virtualization, prioritized message delivery, load balancing, and optimized communication libraries, especially for collective operations such as broadcasts and reductions.

Programs written in Charm++ consist of parallel objects called *chares* that communicate with each other through asynchronous message passing. When an object receives a message, the message triggers a corresponding *entry method* within the object to handle the message asynchronously. Further, objects may be organized into one or more indexed collections called *chare arrays*. Messages may be sent to individual objects within a chare array or to the entire chare array simultaneously.

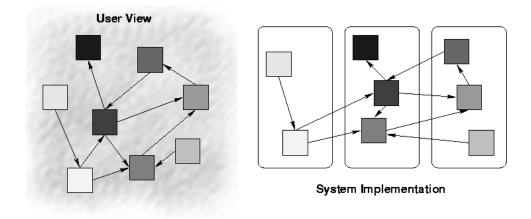

The chares in a Charm++ program are assigned to processors by the runtime system, and this mapping is transparent to the user. Figure 2.1 illustrates the concept that the

Figure 2.1: Depiction of the user's view of a Charm++ application and the system's view after mapping objects to processors

user's view of a Charm++ computation usually varies greatly from the way that the computation is mapped onto physical resources. The user views the computation in terms of the object-based abstraction, simply invoking methods on objects within the computation. The runtime system's view of the system is quite different, however, because it includes details about object placement and about the messages sent between objects that correspond to method invocations made by the user. Because the object-to-processor mapping is transparent to the user, the runtime system may change this assignment dynamically by migrating objects among processors. A suite of measurement-based load balancers is provided to take advantage of this capability. In addition, the migration capability is leveraged to support other capabilities such as automatic checkpointing, fault tolerance, and the ability to shrink and expand the set of processors used by a parallel job.

Adaptive MPI (AMPI) [20] provides the same capabilities as Charm++ in a more familiar MPI programming model. AMPI implements the MPI standard by encapsulating each MPI process within a user-level migratable thread. By embedding each thread within a Charm++ object, AMPI programs can automatically take advantage of the features of the Charm++ runtime system with little or no changes to the underlying MPI program. This is very attractive for the work presented in this thesis due to the large number of MPI applications available representing a wide-variety of styles of problem decomposition that may be readily deployed into Grid environments without requiring modification of application code.

The message-driven model used in the Charm++ runtime system is similar to the model used in systems such as Active Messages [48, 49], Fast Messages [40], and Nexus [13, 14]. A key idea with Charm++, however, is that a programmer completely decomposes a program into a large number, tens or hundreds, of Charm++ chares or AMPI threads per physical processor, allowing the runtime system to adaptively overlap computation in ready objects with communication taking place in objects waiting for remote data. These objects can in some ways be thought of as virtualizing the notion of a processor [22]. This use of processor virtualization is similar to virtualization used in systems such as the CM-2 [2].

#### 2.2 Virtual Machine Interface

The proliferation of high-performance clusters built from commodity off-the-shelf components has resulted in the widespread use of several high-bandwidth low-latency cluster interconnects such as Myrinet [6] and InfiniBand [44]. Because these types of interconnects deliver very good hardware performance, increased emphasis has been placed on the efficiency of the underlying messaging software. Delivering point-to-point communication performance near what is achievable from the raw network hardware is now the primary goal to message layer designers. Furthermore, messaging layers are now expected to address several secondary goals including portability, monitoring and management, and support for applications running in distributed Grid computing environments.

The Virtual Machine Interface (VMI) message layer [42, 41] is designed to be a lowoverhead abstraction layer providing several compelling features:

• Multiple interconnects – VMI is designed to provide a single programming interface to the various network interconnects commonly used in high-performance commodity clusters. Software implemented on VMI immediately gains access to all of the interconnects supported by VMI while paying a small overhead of only a few microseconds per message. Furthermore, the underlying network interconnect may be switched simply by changing the contents of a file that describes the devices used for the computation; no recompilation or relinking of the application software is necessary.

- Data striping and automatic fail-over Because VMI operates as a software layer directly above the native network interconnect layer, it can stripe data across multiple network interconnects, even if these network interconnects are heterogeneous. By striping data across multiple network interconnects, VMI can deliver the aggregate bandwidth available from all interconnects to the application. Furthermore, if one interconnect fails, VMI can simply continue operating with any remaining interconnects.

- Portability VMI is designed to be portable in two ways. First, VMI is designed to be portable to a wide variety of network interconnects. The challenge to this goal is the difficulty in designing a single Application Program Interface that can encompass all of the lower-level network APIs currently available while simultaneously providing excellent performance by giving the programmer access to some of the unique features of individual interfaces. Second, VMI is designed to be portable to a wide variety of platforms. Currently, VMI is available on IA-32, IA-64, and PowerPC architectures.

- Scalability As high-performance commodity clusters increase in popularity, there is also a trend toward an increase in the number of nodes in a single cluster. Clusters with hundreds or thousands of nodes are now common. To this end, VMI is designed to scale to upward of several thousand nodes.

- Support for distributed Grid-based computing The increasing number of cluster installations within collaborating organizations has led to a growing desire to connect multiple clusters together in order to harness the aggregate power of all machines. The challenges to creating a messaging layer to address this goal are twofold. First, the messaging layer must scale to hundreds or thousands of nodes, just like in the

case of building independent clusters that each contain a large number of nodes. Second, the messaging layer must not only provide good performance for the variety of interconnects used within each cluster but must also provide good performance for the wide-area networks used to connect the clusters themselves together. Design decisions regarding bandwidth and latency, for example, may be applicable to local area networks but not to the wide area. Because VMI is designed to be scalable to upward of several thousand nodes and because it readily supports various types of interconnects, it is a favorable platform for Grid computing. Furthermore, algorithms within VMI are designed to be latency tolerant in order to allow VMI to function correctly over wide-area networks.

• Dynamic monitoring and management – In order to deal with the ever-increasing complexity of cluster and Grid computing environments, modern messaging layers add support for monitoring and management. VMI includes capabilities for monitoring the state of the messaging layer in real time and dynamically managing the state of the entire network stack.

VMI achieves many of these goals by using an architecture in which software modules are dynamically loaded at runtime. These modules are organized into a *send chain* and a *receive chain* of modules, with all data that passes out of or into the messaging layer traveling through the modules on the respective chain. Each module on a chain may simply pass the data to the next module, modify the data in some way (for example, by compressing or encrypting it), or "sink" the data by delivering it into the underlying network (in the case of a device on the send chain) or into the application (in the case of a device on the receive chain). This architecture leads to many novel possibilities. For example, as described above, by loading multiple modules simultaneously, data may be striped across multiple interconnects. This concept may be extended to allow a parallel application to run in a Grid computing environment using a high-performance interconnect to communicate with local neighbors within the computation and a wide-area network to communicate with neighbors located on remote nodes.

One of the most important contributions of VMI is its ability to provide an abstract view of the underlying network used by all parts of a distributed Grid computation. Underneath this abstract view, however, may be a network consisting of several heterogeneous interconnects. Using VMI, message data travels over the most efficient point-to-point connection between any pair of processes in a Grid computation. Further, the overhead of this capability is measured in a few microseconds per message. It is for this reason that VMI is a critical part of the work surrounding this thesis.

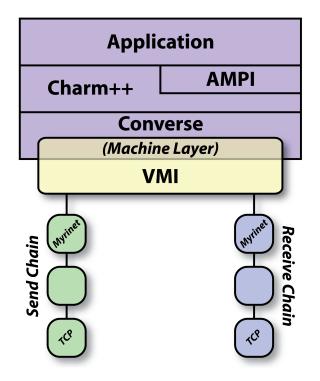

#### 2.3 Efficient Implementation of Charm++ on VMI

VMI is not typically intended to be a software layer exposed directly to application developers, but rather as a layer upon which higher level message layers or runtime systems can be built. To this end, earlier work [34] describes an efficient implementation of Charm++ that uses VMI as its underlying message passing layer. This implementation is significant to the work described in this thesis because it delivers the features of VMI described in Section 2.2 to Charm++ and AMPI applications without requiring any additional effort on the part of the application developer. In light of the challenges to Grid computing described in Section 1.2, probably the most important contribution that the efficient implementation of Charm++ on VMI provides is abstracting the details of the various underlying interconnects used in all parts of a Grid computation. That is, an application can run across two clusters using, for example, Myrinet for communication in one cluster, InfiniBand for communication in the other cluster, and TCP/IP for inter-cluster communication. All communication between any pair of processes in the computation travels over the most favorable interconnect possible.

Figure 2.2 shows the structure of the Charm++ implementation on VMI. Charm++

Figure 2.2: Structure of the efficient implementation of Charm++ on VMI

is implemented in terms of Converse, a portable foundation for higher-level language and library writers. Converse includes a set of functions, the Converse Machine Interface, that define the base functionality that must be implemented to port Charm++ to a new architecture. The implementation of Charm++ is written in terms of this Converse Machine Interface, requiring few modifications to the core Charm++ software itself.

Using the implementation of Charm++ on VMI as a basis for the work in this thesis provides several useful possibilities. For example, the following section describes a VMI "delay device" that can induce arbitrary artificial latencies between pairs of processes in a computation. This delay device allows simulating a Grid environment with any desired latencies using a single cluster.

### 2.4 Artificial Latency Environment

Because running an application in a real Grid environment does not permit varying the wide-area latency as necessary to carry out experiments, the features of VMI can be used to create a "simulated Grid environment" physically consisting of nodes from a single real cluster. In this simulated Grid environment, arbitrary latencies can be inserted between any pair of nodes, allowing cross-cluster latencies to be swept across a range to study the impact of varying wide-area latencies on the underlying application. Creating such an environment leverages the implementation of Charm++ running on the Virtual Machine Interface messaging layer. Recall that a novel feature of VMI is the ability to organize the device driver software modules used for communication operations into send and receive chains of drivers. As message data travels along a chain, each module on the chain may simply pass the data to the next module, manipulate the data in arbitrary ways, or deliver the data into the underlying network. This capability of intercepting message data is used to write a VMI device driver that injects pre-defined latencies between arbitrary pairs of nodes. This "delay device driver" is then inserted into the VMI device chains used for experiments by constructing send and receive chains that consist of two network drivers with the delay driver in between. By affiliating a subset of the cluster's nodes (i.e., those that exist on the "local cluster") with the first driver in the chain, message data are immediately sent between the nodes within that subset without passing through the delay device. For nodes not in this affiliation (i.e., those that exist on the "remote cluster"), messages are intercepted by the delay device which delays the message by a pre-defined amount of time before passing it to the network device driver used to communicate over the "wide area."

The VMI delay device carries out its work on the receive side of a communication channel. When message data arrives at the delay device, the driver inserts the data along with the arrival time into a linked list of delayed messages. As the runtime system periodically "pumps" the message layer for new messages, the timestamp for the element at the head of the list is examined. If the current time is greater than the head element's arrival time plus the pre-defined artificial latency, the message is released to the runtime system for delivery. Because messages are timestamped in the order that they are received, only the head of the list needs to be examined for each "pump" operation; all elements following the head are necessarily received after the head element.

Creating the artificial latency environment used for the experiments in this thesis involves few changes to the software stack used in real Grid environments. That is, the application, runtime system, messaging layer, and underlying communication layers are all the same both in experiments using the artificial latency environment and in experiments running in real Grid environments; only the introduction of the delay device driver is necessary to construct the artificial latency environment. For this reason, experiment results collected in the artificial latency environment closely match results collected in real Grid environments. In particular, the results for the case studies presented in Chapter 8 show very similar performance for parallel applications running in both environments.

# Chapter 3 Related Work

The work described in this thesis shares characteristics with several other projects while at the same time offering its own unique contributions. This chapter describes related work and draws comparisons and contrasts to the work described in this thesis.

Viewing a distributed computation as a set of interacting objects and, accordingly, using object oriented programming techniques to manage complexity is an attractive approach to Grid computing. Several other projects such as Legion [16] and Globe [47] share this characteristic with the work presented in this thesis. In contrast, however, both of these projects tend to be focused more on the entire range of problems surrounding Grid computing, including resource management, file and data access, information brokering, and security. Indeed, the designers of Legion call such an all-encompassing system a *metasystem*. Examples of applications running in these kinds of environments appear to be focused on those types that can implicitly tolerate latency, such as parameter sweep applications [39], or applications such as molecular dynamics applications running entirely within the context of a single machine on the Grid [38]. The goal of this thesis differs from this type of work in that this thesis is specifically focused on the topic of developing techniques for efficiently executing tightly-coupled applications that are co-allocated across multiple resources in a Grid environment.

Several projects extend the MPI parallel computing standard to work in a Grid environment with the goal of allowing jobs that can span multiple clusters. Examples of such projects include MPICH-G2 [24] and MPICH/MADIII [4]. These projects, like the work described in this thesis, view the communication infrastructure of a distributed Grid job as a hierarchy of interconnects. Such a view consists of high-performance local-area interconnects such as Myrinet or InfiniBand at one level of the hierarchy and lower-performance wide-area interconnects such as TCP/IP at another level of the hierarchy. The goal is to allow any pair of processors to communicate via the most efficient channel possible within the hierarchy. MPICH-G2 achieves this goal by being layered on top of underlying native MPI implementations within each cluster to provide efficient intra-cluster communication and by using TCP/IP to provide inter-cluster communication. MPICH/MADIII takes an approach that is very similar to the implementation of Charm++ on VMI described in Section 2.2. MPICH/MADIII is implemented on top of a communication library, Madeleine III, that allows multiple underlying networks to be used in a way similar to VMI. Further, MPICH/MADIII uses an efficient user-level thread library, Marcel, that provides task decomposition capabilities similar to what is available with Charm++ objects or Adaptive MPI threads. In contrast to MPICH/MADIII, however, the work described in this thesis seeks to increase the number of opportunities for the adaptive runtime system to overlap useful computation with communication by using very large degrees of virtualization, with perhaps hundreds of objects per physical processor in the computation. MPICH/MADIII seems to typically use a much smaller number of threads per processor. Further, the Charm++ adaptive runtime system includes the ability to dynamically load balance objects within a distributed computation while MPICH/MADIII does not seem to offer this functionality. This capability is important for achieving good performance on fine-grained Grid computations that span multiple clusters.

Various algorithm-level approaches to tolerating latency in Grid computing environments exist. For example, the performance of Partial Differential Equation solvers running in a Grid environment may be improved by increasing the number of ghost cell layers used per processor [8]. Increasing the number of ghost zones allows each processor to buffer more data and reduces the number of messages sent between processors. Further improvements to the PDE algorithm allow the elimination of diagonal communications. Together, these algorithm-level optimizations allow the performance of the application described in the cited paper to be improved by as much as 170%. The primary contrast between approaches such as the one described in the paper and the work described in this thesis is that the techniques described in this thesis operate at the runtime system layer rather than at the application layer. While algorithm-level approaches have the advantage that they can generally achieve very good levels of optimization, runtime-level approaches have the advantage that they are broadly available to a wide variety of problem decomposition types (i.e., structured and unstructured mesh decomposition, spatial decomposition, etc.) without requiring modification of application software.

Cactus-G [3] is a Grid-enabled computational framework that is based on the Cactus problem solving environment and the MPICH-G2 message passing library. Originally designed for use in numerical relativity applications such as modeling black holes, neutron stars, and gravitational waves, Cactus has grown into a framework well-suited to solving general mesh decomposition problems. A novel feature of Cactus is that it consists of a central core called the *flesh* which connects to application modules called *thorns* through an extensible interface. The thorns in a computation encapsulate the actual scientific code governing the application as well as capabilities such as parallel I/O, data distribution, and checkpointing. The experiment described in the paper leverages this rich platform to perform an experiment in which a heterogeneous environment consisting of four machines distributed between the San Diego Supercomputing Center (SDSC) and the National Center for Supercomputing Applications (NCSA) is synthesized and applied to a tightly-coupled mesh decomposition problem. The authors are successful in this endeavor due to the ability to leverage thorns that optimize the computation in three ways. First, because the resources physically allocated to the computation consisted of one machine at SDSC and three machines at NCSA, the authors positioned the gridpoints in the mesh to reflect this uneven distribution. Second, the authors increased the size of the ghost zone layers on each processor similar to the method used in the ghost zone expansion technique described above [8]. Third, the authors used a thorn to compress message data that were sent over the wide-area connection between SDSC and NCSA. In many ways, Cactus-G can be thought of as an elaborate runtime system that offers features similar to those found in the Charm++ runtime. The work described in this thesis differs from the work in Cactus, however, in that the approach taken by this thesis focuses on dividing a computation into a large number of objects and then dynamically mapping and re-mapping these objects onto physical processors as the computation progresses. In many senses, this approach is at a lower level in the software stack than the approach taken by Cactus-G.

Load balancing of parallel applications is a well-known concept with a history dating back more than twenty years. For example, Fox describes load balancing through the use of randomized placement of sub-blocks within a problem [15]. Interest in load balancing has increased in recent years in the field of Grid computing because the performance of Grid applications can be significantly improved through the use of good load balancing. Two primary ways of doing Grid load balancing exist: static techniques and dynamic techniques. When using static techniques, decomposed pieces of an overall problem are assigned to the most suitable (least loaded) processor in the computation. However, once a unit of work is placed on a processor, it remains on that processor until the work is completed; it cannot migrate to a new processor as is possible with the Charm++ runtime system. Frequently, static load balancing techniques cannot fully address the unique needs of Grid environments due to the constantly-changing nature of Grids. To that end, the work presented in this thesis focuses on dynamic load balancing techniques provided by the Charm++ runtime system [55].

The dynamic load balancing capabilities of the work described in this thesis are similar to systems such as OptimalGrid [30] which monitor the runtime performance of each node in a computation with respect to the portion of a problem that it is handling and reapportion successive iterations of the computation to address load imbalances. A particularly in-depth analysis of this type of technique was carried out using a Successive Over-Relaxation (SOR) mesh problem running in the PlanetLab Grid environment [9]. The biggest difference between the dynamic load balancing research in OptimalGrid and in the PlanetLab experiments and the work in this thesis is that the work presented here balances a computation in terms of both measured CPU utilization and the object-to-object communication graph of the computation in relation to the structure of the Grid resources used by the computation.

The common thread that differentiates the work described in this thesis from others is the pervasive use of message-driven execution, in the form of Charm++ chares or AMPI threads, coupled with Grid topology-aware dynamic load balancing as a means of tolerating latency in Grid computing environments without requiring modification of application software.

# Chapter 4 Adaptive Latency Masking

Perhaps the most important factor for successfully running tightly-coupled applications in Grid environments is the ability to mask the effects of cross-site latency on the portions of the computation that communicate across the wide area. Many parallel applications are written in a way so as to minimize the effects of latency, at least to some degree. For example, a common way of structuring MPI applications is to arrange each timestep such that each processor asynchronously sends data in ghost cells at the borders of the processor's portion of application data to its neighbors in the computation, then performs its computation required to complete the timestep, and finally receives the data necessary to compute the next timestep from its neighbors in the computation. Thus, the time required to communicate a processor's data to its neighbors is partially masked by the time used by the processor to perform its computation in the timestep. This solution, while helpful in traditional parallel computing environments, is less useful in Grid environments because the degree to which latency can be masked within the application varies only with the number of processors used to decompose the problem. While this may be worthwhile within the context of a single parallel machine with microsecond latencies between processors, it may be much less worthwhile in a Grid environment in which inter-processor latencies may be tens of milliseconds between some processor pairs. Further, the solution requires the application programmer to carefully structure the application software itself to achieve latency masking, and this may make the software much more complicated than it otherwise would need to be.

This chapter describes how the architecture of the Charm++ runtime system itself can be used to mask the effects of latency on tightly-coupled parallel applications running in Grid environments. The technique described here is especially attractive because it takes place automatically within the runtime system, allowing the application programmer to structure the application in a more straightforward manner that does not need to take the deployment environment into consideration. More importantly, however, the number of objects used to decompose a Charm++ program does not depend on the number of processors on which the application is running. This means that the number of objects can be varied to give the application a higher degree of latency tolerance.

### 4.1 Adaptive Latency Masking in Grid Environments

The fundamental idea behind the Charm++ runtime system is that a programmer divides a program into a large number of message-driven entities, implemented in the form of either Charm++ objects or Adaptive MPI virtual processors. The number of objects or virtual processors is independent of, and in practice much larger than, the number of physical processors. The runtime system maps objects onto physical processors and may dynamically adjust this mapping as the application executes to balance load or optimize communication costs. Rather than thinking in terms of physical processors, the programmer thinks in terms of the object abstraction and writes code to coordinate interactions among these entities. These interactions are realized as asynchronous messages that are passed between physical processors in the computation. As messages arrive at a physical processor, they are enqueued in a message queue in either FIFO or priority order. When a physical processor becomes idle, its message scheduler dequeues the next waiting message and delivers it, triggering the execution of code that is encapsulated within an object to handle the message. This code runs to completion, producing other messages for objects on this or another physical processor.

Because messages are asynchronous, the runtime system may schedule the execution of a new object immediately after execution within an existing objects completes, resulting in one

Figure 4.1: Hypothetical timeline illustrating the use of message-driven objects to tolerate wide-area latency

or more messages sent by the object. Rather than waiting for these messages to be delivered, the newly-scheduled object begins work immediately, thus overlapping its computation with the communication of the previous object. This ability to overlap useful computation with communication is important within the context of a single parallel machine, but is especially critical for applications that are running in a Grid environment in which nodes are separated by a high-latency wide-area network. Figure 4.1 illustrates this concept by depicting a hypothetical timeline for three processors running on two clusters that are connected by a high-latency wide-area network. Processors A and B are located within one cluster and processor C is located within the second cluster. At the left side of the timeline, processor B sends a message to processor C; this message must cross the high-latency inter-cluster network. Rather than waiting idly for this message to be delivered, B is free to respond to incoming messages from processor A, and in fact performs several short computations and message exchanges with A. Finally, processor C responds to processor B with the result of the computation previously triggered by B. The important idea is that B is able to do useful work during the gap between dispatching a message to C and receiving a response.

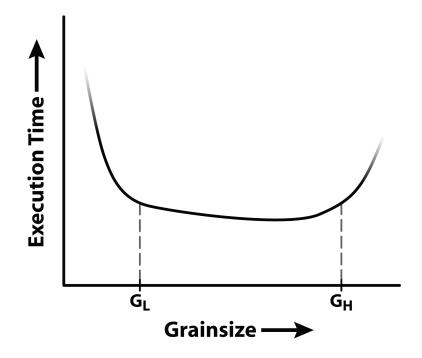

Issues related to adaptivity and granularity in Charm++ programs have been studied extensively [23, 17, 22, 18] and are important to the discussion in this chapter. The cited

papers report that the overhead associated with scheduling a Charm++ object invocation is small, less than a microsecond, and that the most critical factor in determining an appropriate grainsize for Charm++ applications is the communication overhead. Figure 4.2 illustrates this concept by showing the execution time of a hypothetical parallel application as a function of grainsize. For small grainsizes, where a large number of objects are used to decompose the problem, execution time is relatively large due to a large amount of overhead spent in communication. As grainsize increases and approaches  $G_L$ , execution time decreases rapidly. This is because the problem is divided among a smaller number of objects, with each object working on a larger portion of the problem space, thus requiring less communication. Throughout the flat region of the graph, between  $G_L$  and  $G_H$ , execution time remains essentially unchanged because the overhead of communication is only a small fraction of the overall execution time. Finally, when grainsize increases beyond  $G_H$ , execution time once again increases significantly due to insufficient parallelism resulting in wasted idle time. The important conclusion drawn in the cited papers is that the grainsize in Charm++ programs should be as small as possible while still masking overhead. This allows the number of objects used to decompose a problem to be independent from the number of processors upon which the problem runs, giving the Charm++ runtime system the maximum amount of freedom in mapping objects to processors.

#### 4.2 Example Application: Five-Point Stencil

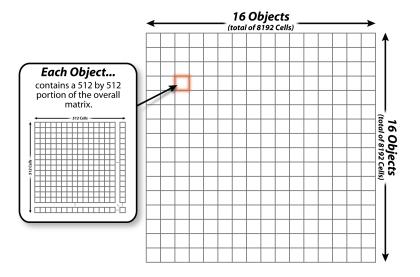

To examine the effectiveness of using the Charm++ runtime system's message-driven execution model to mask latency, a simple five-point stencil finite difference method, also known as a two-dimensional Jacobi decomposition (Jacobi2D), was examined in a simulated Grid environment consisting of two clusters separated by a high-latency wide-area connection. This simulated Grid environment is constructed using the VMI artificial latency environment described in Section 2.4. In this class of numerical method, a multidimensional mesh

Figure 4.2: Execution time of a parallel application as a function of grainsize [23]

is repeatedly updated by replacing the value at each point with some function of the values at a small, fixed number of neighboring points. In the case of the experiment described here, the neighboring points taken into consideration are the ones directly above and below as well as to the left and right of a given cell. This produces four discrete communication events per cell for each time-step.

For the experiment here, meshes of size 2048x2048 and 8192x8192 cells are considered. The problem is decomposed using Charm++ objects by dividing the cells within the mesh evenly among a specified number of objects. For example, for an 8192x8192 mesh divided among 256 objects, 16 objects are mapped along each axis of the mesh. Accordingly, each object has a 512x512 square section of the mesh to operate upon. During each time step, each object communicates values for a 512x1 vector of cells to its appropriate neighbor. Figure 4.3 graphically depicts this example problem layout.

The mesh is divided in half and split across two clusters separated by a wide-area connection, causing every time step to involve some objects communicating with neighbors situated

Figure 4.3: Graphical depiction of a five-point stencil decomposition in which a fixed number of cells are divided across a variable number of objects

across the wide area. More importantly, however, both clusters contain a large number of objects that communicate with neighbors solely within the local cluster. The expectation is that the message-driven execution model will allow the high-latency communication operations to be masked by other communication that is carried out with neighbors situated on the local cluster.