# ACHIEVING HIGH PERFORMANCE ON EXTREMELY LARGE PARALLEL MACHINES: PERFORMANCE PREDICTION AND LOAD BALANCING

#### BY

### GENGBIN ZHENG

B.S., Beijing University, China, 1995 M.S., Beijing University, China, 1998

### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2005

### **Abstract**

Parallel machines with an extremely large number of processors (at least tens of thousands processors) are now in operation. For example, the IBM BlueGene/L machine with 128K processors is currently being deployed. It is going to be a significant challenge for application developers to write parallel programs in order to exploit the enormous compute power available and manually scale their applications on such machines. Solving these problems involves finding suitable parallel programming models for such machines and addressing issues like load imbalance. In this thesis, we explore Charm++ programming model and its migratable objects for programming such machines and dynamic load balancing techniques to help parallel applications to easily scale on a large number of processors. We also present a parallel simulator that is capable of predicting parallel performance to help analysis and tuning of the parallel performance and facilitate the development of new load balancing techniques, even before such machines are built.

We evaluate the idea of virtualization and its usefulness in helping a programmer to write applications with high degree of parallelism. We demonstrate it by developing several mini-applications with million-way parallelism. We show that Charm++ and AMPI (an extension to MPI) with migratable objects and support for load balancing are suitable programming model for programming very large machines.

It is important to understand the performance of parallel applications on very large parallel machines. This thesis explores Parallel Discrete Event Simulation (PDES) techniques with an optimistic synchronization protocol to simulate parallel applications running on a very large number of processors. We optimize the synchronization protocol by exploiting the inherent determinacy that is normally found in parallel applications to reduce the synchronization overhead significantly.

Load balance problem presents significant challenges to applications to achieve scalability on very large machines. We study load balancing techniques and develop a spectrum of load balancing strategies based on studies of the characteristics of applications. These load balancing strategies are motivated by several real-world applications such as LeanMD, NAMD (both are classical molecular dynamics applications) and

Fractography3D (a dynamic 3D crack propagation simulation program). We optimize our load balancing strategies in multiple dimensions of criteria such as load balancing for improving communication locality, sub-step load balancing, and computation phase-aware load balancing.

We further study the performance of existing load balancing strategies in the context of very large parallel machines using the parallel simulator we developed. We demonstrate the weaknesses of the centralized and fully distributed load balancing schemes via large scale simulation, and design a new scalable hierarchial load balancing scheme suitable for such large machines. This hierarchial load balancing scheme builds load data from instrumenting an application at run-time on both computation and communication pattern in a fully automatic way. The hierarchial load balancing takes application communication pattern into account explicit in decision making. It also incorporates an explicit memory cost control function to make it easy to adapt to extremely large number of processors with small memory footprint.

To my wife Lixia Shi and our newborn son Chenyuan

## Acknowledgements

I would like to thank my thesis advisor, Prof. Kale, for his guidance, advice, motivation and continued support throughout my academic career at University of Illinois, without which this thesis would not have been possible.

I would like to thank the several past and current PPL members, Milind, Orion, Terry, Sameer, Eric, Chao ... It was a lot of fun working with you guys.

Many thanks to the various members of the TCBG group. Robert for helping me with load balancing framework in my thesis. It was a great pleasure and experience working with Jim.

I would also like to thank my wife Lixia, who has always been my source of inspiration. I'll never forget the day she gave birth to my son ChengYuan, who brought endless joyfulness to my family.

Finally, I would like to thank my parents for all their love, encouragement and inspiration that was needed to accomplish this task.

# **Table of Contents**

| List of ' | Tables                                                    | • • | X   |

|-----------|-----------------------------------------------------------|-----|-----|

| List of l | Figures                                                   |     | xii |

| Chapte    | er 1 Introduction                                         |     | 1   |

| 1.1       | Petaflops-class Machine Architectures                     |     | 1   |

| 1.2       | Software Challenges                                       |     | 3   |

| 1.3       | Approach                                                  |     | 4   |

| 1.4       | Contributions                                             |     | 5   |

| 1.5       | Dissertation Outline                                      |     | 7   |

| Chapte    | er 2 CHARM++/AMPI and Processor Virtualization            |     | 8   |

| 2.1       | Charm++ vs. Conventional Programming Models               |     | ç   |

| Chapte    | er 3 Dealing with Very Large Parallel Machines            |     | 12  |

| 3.1       | Need for Emulator of Very Large Parallel Machines         |     | 12  |

| 3.2       | Methodology                                               |     | 13  |

| 3.3       | Parallel Emulator                                         |     | 13  |

|           | 3.3.1 Emulator Function API                               |     | 15  |

|           | 3.3.2 Emulating Hardware Processors                       |     | 16  |

|           | 3.3.3 Emulator Performance                                |     | 20  |

| 3.4       | Porting High Level Parallel Languages to the Emulator     |     | 22  |

|           | 3.4.1 Design Issues                                       |     | 22  |

|           | 3.4.2 Experience with the Emulator                        |     | 26  |

| Chapte    | er 4 Performance Prediction for CHARM++/AMPI Applications |     | 27  |

| 4.1       | Methodology                                               |     | 28  |

| 4.2       | Related Work in PDES                                      |     | 29  |

|           | 4.2.1 Synchronization Protocols                           |     | 29  |

|           | 4.2.2 Performance Prediction for Parallel Applications    |     | 31  |

| 4.3       | Component Performance Models                              |     | 31  |

| 4.4       | Parallel Simulator                                        |     | 33  |

| 4.5       | Simulating Parallel Applications                          |     | 34  |

|           | 4.5.1 Simulating Linear Order Applications                |     | 34  |

|           | 4.5.2 Simulating a Broader Class of Applications          |     |     |

|           | 4.5.3 Implementation Details and Optimizations            |     | 39  |

| 4.6       | Network Simulation                                        |     | 42  |

|         | 4.6.1 Parallel Simulator Performance                |  |

|---------|-----------------------------------------------------|--|

| 4.7     | Validation and Performance Case Studies             |  |

|         | 4.7.1 Verification of Jacobi on BG/L                |  |

|         | 4.7.2 Validation — AMPI                             |  |

|         | 4.7.3 Validation — NAMD                             |  |

|         | 4.7.4 Performance of the Simulation                 |  |

|         |                                                     |  |

| -       | *5 Million-way Parallelization                      |  |

| 5.1     | Molecular Dynamics Simulation - LeanMD              |  |

| 5.2     | Finite Element Methods Simulation                   |  |

| Chapter | 6 Dynamic Load Balancing Framework                  |  |

| 6.1     | The Load Balancing Problem                          |  |

|         | 6.1.1 Basic Definitions                             |  |

| 6.2     | Application Load Imbalance                          |  |

| 6.3     | Related Work and Load Balancing Contexts            |  |

|         | 6.3.1 Non-iterative Applications                    |  |

|         | 6.3.2 Iterative Applications with Predictability    |  |

|         | 6.3.3 Iterative Applications without Predictability |  |

|         | 6.3.4 Partitioning Algorithms                       |  |

|         | 6.3.5 Task Migration                                |  |

|         | 6.3.6 Our Approach                                  |  |

| 6.4     | Practical Load Balancing Methodology                |  |

|         | 6.4.1 Load Evaluation                               |  |

|         | 6.4.2 Load Balance Initiation                       |  |

|         | 6.4.3 Load Balance Decision Making                  |  |

|         | 6.4.4 Object Migration                              |  |

| 6.5     | CHARM++ Load Balancing Framework                    |  |

| 6.6     | Framework Overview                                  |  |

|         | 6.6.1 Components                                    |  |

| Chapter | 7 Centralized Load Balancing Strategies             |  |

| 7.1     | Quantitative Performance Analysis Methodology       |  |

|         | 7.1.1 Sequential Load Balancing Simulation Tool     |  |

| 7.2     | Basic Centralized Load Balancing Strategies         |  |

|         | 7.2.1 Overview                                      |  |

|         | 7.2.2 Performance Evaluation                        |  |

|         | 7.2.3 Application Study — NAMD                      |  |

| 7.3     | Load Balancing with Communication                   |  |

|         | 7.3.1 Overview                                      |  |

|         | 7.3.2 Performance Evaluation                        |  |

|         | 7.3.3 Collective Communication                      |  |

|         | 7.3.4 Application Study — LeanMD                    |  |

| 7.4     | Temporal Characteristic - Multi-phase Computation   |  |

|         | 7.4.1 Experiments                                   |  |

| 7.5     | Asynchronous Load Balancing                         |  |

|         | 7.5.1 Towards Any-time Migration                    |  |

|         | 7.5.2 Asynchronous Load Balancing 110               |  |

|         | 7.5.3   | Application Study — Fractography3D                                      |

|---------|---------|-------------------------------------------------------------------------|

| Chapter | 8 Lo    | ad Balancing Strategies for Peta-scale Machines                         |

| 8.1     | Load I  | Balancing Challenges for Peta-scale Machines                            |

| 8.2     | Fully l | Distributed Load Balancing Strategies                                   |

|         | 8.2.1   | Measurement-based Neighborhood Averaging Strategy                       |

|         | 8.2.2   | Neighborhood Averaging with Work-Stealing when Idle                     |

|         | 8.2.3   | Limitations of Fully Distributed Strategies                             |

|         | 8.2.4   | NAMD Performance with a Fully Distributed Strategy                      |

| 8.3     | Centra  | lized Load Balancing Strategies for Peta-scale Machines                 |

|         | 8.3.1   | Simulation Study of Centralized Strategies                              |

|         | 8.3.2   | Summary                                                                 |

| 8.4     | Hybrid  | l Load Balancing Strategy                                               |

|         | 8.4.1   | HybridLB Strategy Details                                               |

| 8.5     | Relate  | d Work                                                                  |

| 8.6     | Perfor  | mance Evaluation of HybridLB                                            |

|         | 8.6.1   | LeanMD                                                                  |

|         | 8.6.2   | Performance Study of HybridLB on Very Large Machines via Simulation 144 |

| Chapter | 9 Co    | onclusion and Future Work                                               |

| Referen | ces     |                                                                         |

| Vita    |         |                                                                         |

# **List of Tables**

| 3.1               | of control                                                                                                                                                                                                                                                       | 18       |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2               | Total memory needed for a number of emulated processors with various stack sizes of a control flow                                                                                                                                                               | 18       |

| 3.3               | Emulation time (in seconds) using CthThreads and Pthreads with BigSim emulator                                                                                                                                                                                   | 21       |

| 4.1               | Actual vs. predicted time                                                                                                                                                                                                                                        | 47       |

| 4.2<br>4.3        | Actual vs. predicted time (in <i>ms</i> ) per timestep for NAMD                                                                                                                                                                                                  | 48<br>52 |

| 5.1               | Simulated speedup vs. estimated speedup (based on load imbalance alone), normalized based on 1000-processor case                                                                                                                                                 | 57       |

| 6.1               | Software systems that support dynamic load balancing                                                                                                                                                                                                             | 72       |

| 7.1<br>7.2        | Performance of Centralized Load Balancers (mesh2d communication)                                                                                                                                                                                                 | 86       |

| 7.3               | Performance of Centralized Load Balancers (randgraph communication)                                                                                                                                                                                              | 87<br>87 |

| 7.4<br>7.5        | Performance of Centralized Load Balancers (Fractography FEM)                                                                                                                                                                                                     | 87<br>97 |

| 7.5<br>7.6<br>7.7 | Performance of Communication-aware Centralized Load Balancers (mesh2d communication)  Performance of Communication-aware Centralized Load Balancers (mesh2d communication)  Performance of Communication-aware Centralized Load Balancers (randgraph communi-    | 98       |

|                   | cation)                                                                                                                                                                                                                                                          | 98       |

| 7.8<br>7.9        | Performance of Communication-aware Centralized Load Balancers (Fractography FEM) Execution times for 1-away LeanMD simulation before load balancing. These simulations do not use the section multicast library. Time per step is taken as the average over five | 98       |

|                   | simulation steps                                                                                                                                                                                                                                                 | 01       |

| 7.10              | Execution times for 1-away LeanMD simulation before load balancing. These simulations use section multicast library. Time per step reported in this table is average over five simu-                                                                             |          |

|                   | lation steps                                                                                                                                                                                                                                                     | 02       |

| 7.11              | Execution times for 1-away LeanMD simulation with load balancing. These simulations do not use the section multicast library                                                                                                                                     | 02       |

| 7.12              | Execution times for 1-away LeanMD simulation after load balancing (Greedy) using section                                                                                                                                                                         |          |

| 7.13              | multicast library. Time per step reported in this table is average over fifteen simulation steps. 1 Execution times for 1-away LeanMD simulation after load balancing (GreedyCommLB)                                                                             | .04      |

|                   | using section multicast library. Time per step reported in this table is average over fifteen simulation steps                                                                                                                                                   | 04       |

|                   | <b>▲</b>                                                                                                                                                                                                                                                         |          |

| 8.1  | Memory usage of centralized load balancers on the central node                       |

|------|--------------------------------------------------------------------------------------|

| 8.2  | Load balancing strategy time in second for 32K processors (on finesse)               |

| 8.3  | Load balancing strategy time in second for 64K processors (on finesse)               |

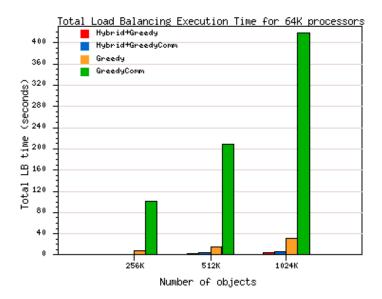

| 8.4  | Total Load balancing execution time for 64K processors (in seconds)                  |

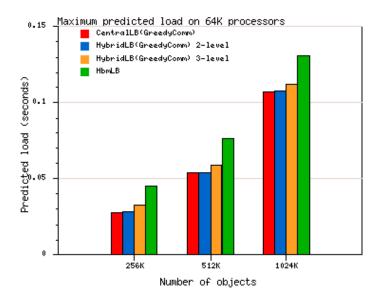

| 8.5  | Maximum predicted load over average load after load balancing for 64K processors 129 |

| 8.6  | Comparison of Load Balancing Time                                                    |

| 8.7  | Maximum memory usage of HybridLB (in bytes)                                          |

| 8.8  | Total load balancing time on 64K processors (in seconds)                             |

| 8.9  | Maximum predicted load after load balancing for 64K processors                       |

| 8.10 | Non-local communication volume on 64K processors                                     |

| 8.11 | Comparison of 2- and 3-level trees for 512k object case                              |

| 8.12 | Comparison of 2- and 3-level trees for 1M object case                                |

# **List of Figures**

| 1.1        | Blue Gene/L architecture (taken from IBM Blue Gene website)                        | 3  |

|------------|------------------------------------------------------------------------------------|----|

| 2.1        | Virtualization in CHARM++                                                          | 8  |

| 3.1<br>3.2 | Functional view of an emulated node                                                |    |

| 3.3        | Context switching time vs. number of flows on Sun Solaris machine                  |    |

| 3.4        | Context switching time vs. number of flows on Mac machine                          |    |

| 3.5        | Simulation Time per Step                                                           |    |

| 3.6        | CHARM++ hierarchy                                                                  |    |

| 3.7        | Layered Implementation of Blue Gene CHARM++                                        | 25 |

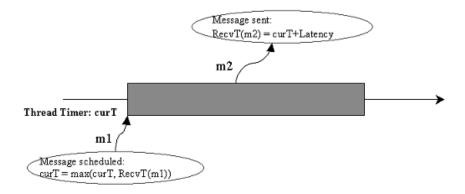

| 4.1        | Timestamping events                                                                |    |

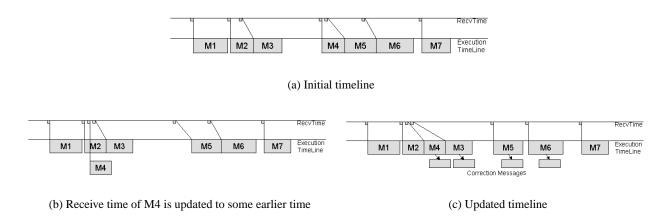

| 4.2        | Timelines after updating event receive time and after complete correction          | 36 |

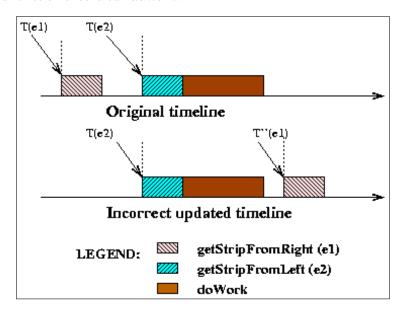

| 4.3        | Incorrect timestamp correction scheme                                              |    |

| 4.4        | Sample code in Structured Dagger                                                   |    |

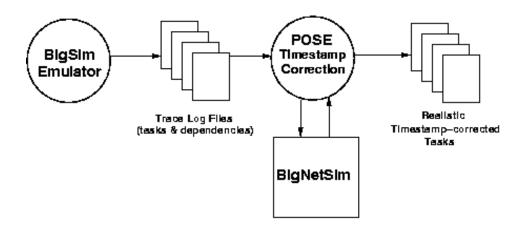

| 4.5        | Interaction between BigSim, Pose timestamp correction and BigNetSim                |    |

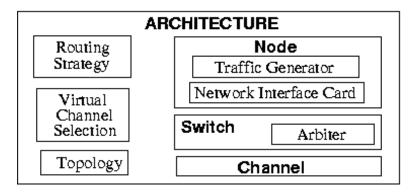

| 4.6        | BigNetSim conceptual model                                                         | 43 |

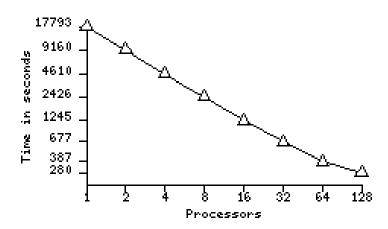

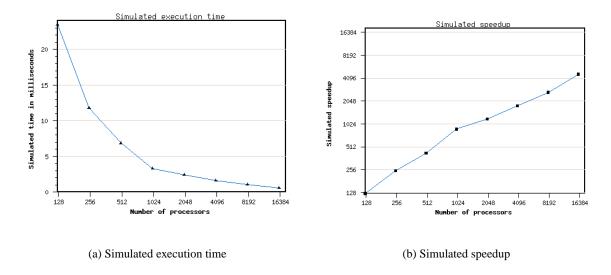

| 4.7        | BigNetSim execution time with NAMD                                                 | 45 |

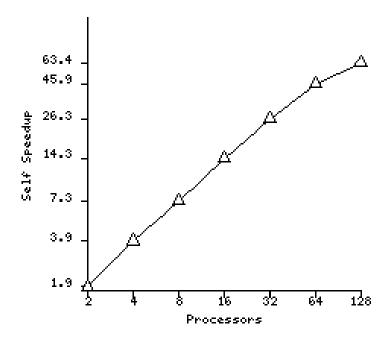

| 4.8        | BigNetSim speedup with NAMD                                                        | 46 |

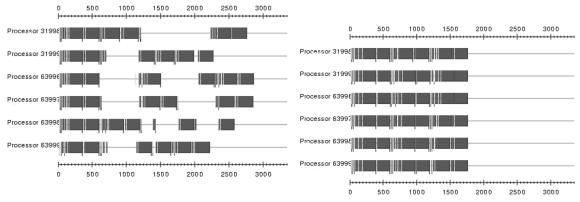

| 4.9        | Timelines before timestamp correction                                              | 47 |

|            | Timelines after timestamp correction                                               |    |

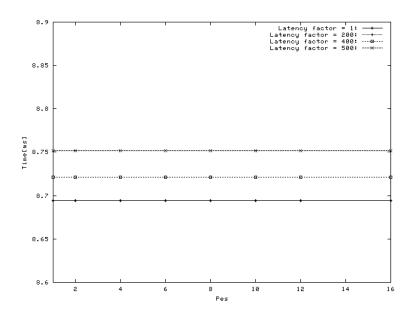

|            | Jacobi simulation predictions on different numbers of physical processors used     |    |

|            | Predicted time vs latency multiplier                                               |    |

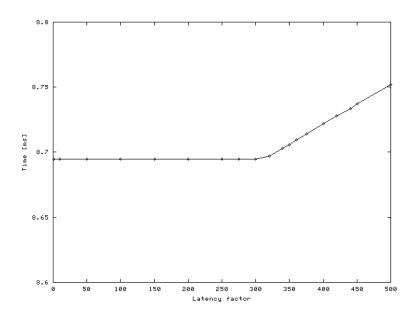

|            | Speedup for Jacobi1D                                                               |    |

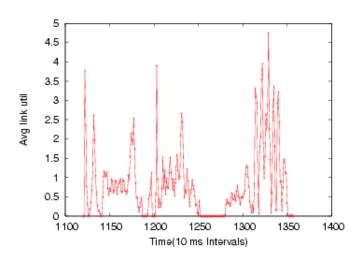

|            | Average Link Utilization in NAMD                                                   |    |

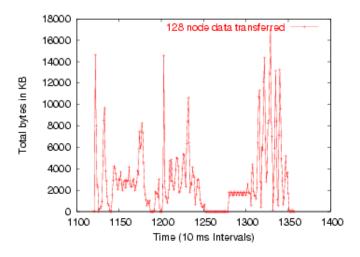

|            | Data Transferred (KB) during Full Simulation                                       |    |

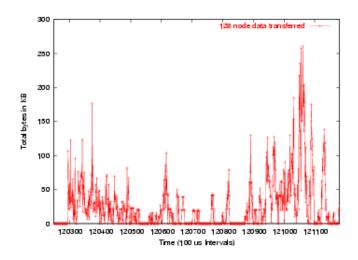

|            | Data Transferred (KB) in a Single Time Step                                        |    |

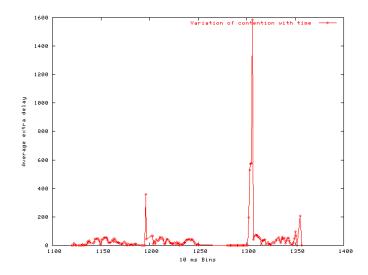

|            | Contention encountered by messages                                                 |    |

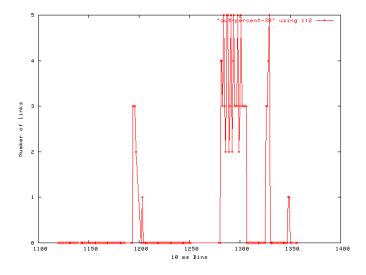

|            | Number of links with utilization greater than 30 percent                           |    |

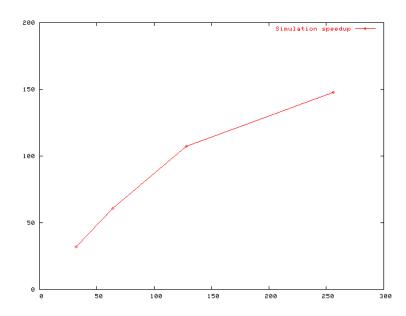

| 4.19       | Simulation Speedup                                                                 | 33 |

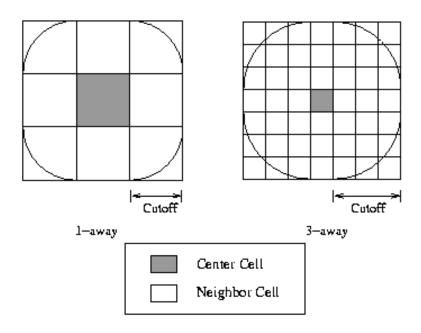

| 5.1        | 1-away and 3-away cut-off distance                                                 |    |

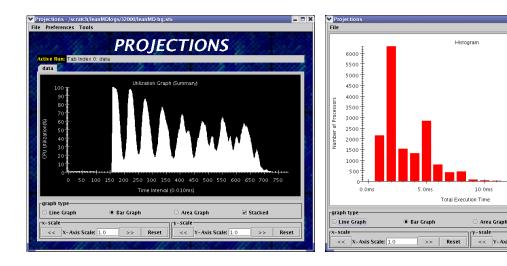

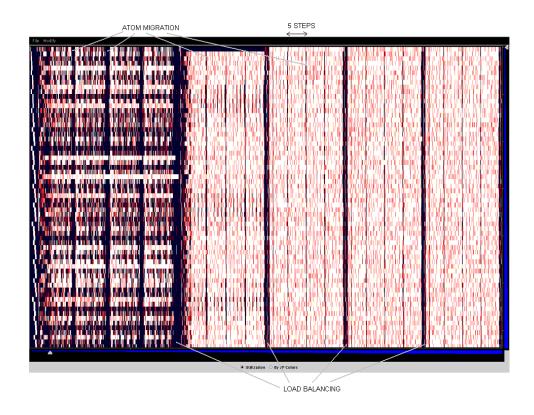

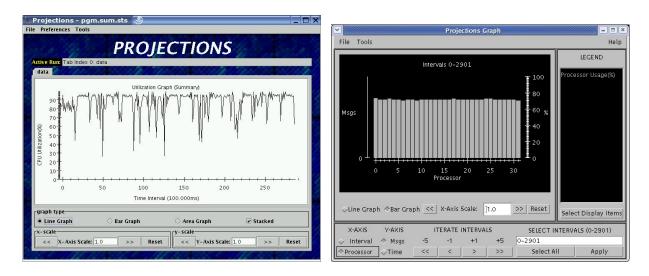

| 5.2        | LeanMD Projections Views                                                           |    |

| 5.3        | FEM Framework Performance on a 5 Million Element Mesh                              |    |

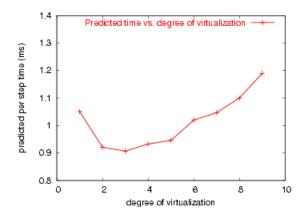

| 5.4        | Predicted execution time for a 5 million element mesh vs. degree of virtualization | 60 |

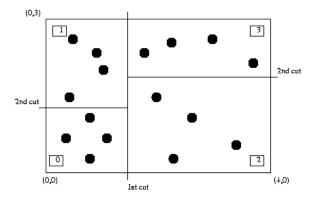

| 6.1        | Recursive hisection                                                                | 68 |

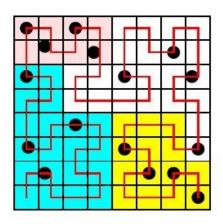

| 6.2  | Space-filling curve                                                                    |     |

|------|----------------------------------------------------------------------------------------|-----|

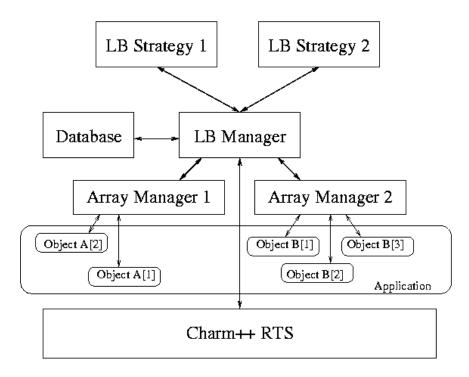

| 6.3  | Components and interactions in the load balancing framework                            | 77  |

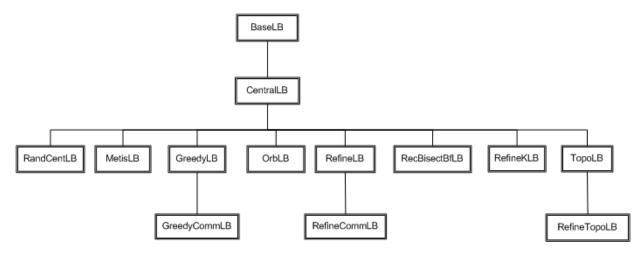

| 7.1  | Centralized load balancers and their hierarchies                                       | 80  |

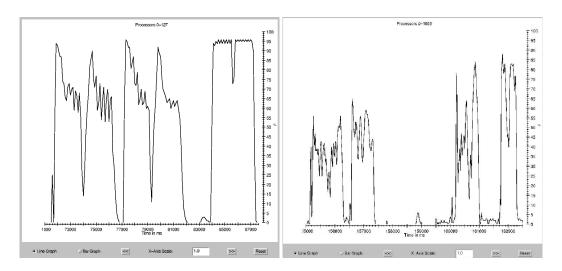

| 7.2  | Average processor utilization against time on (a) 128 (b) 1024 processors              | 88  |

| 7.3  | Average Processor Utilization after (a) greedy load balancing and (b) refining         | 88  |

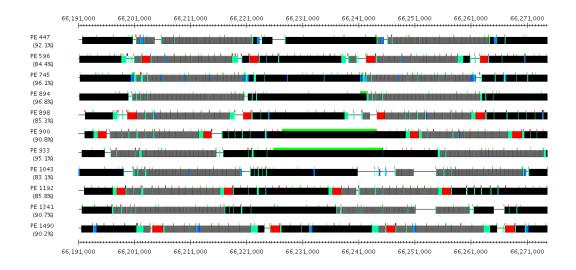

| 7.4  | NAMD Timineline view on 1536 processors                                                |     |

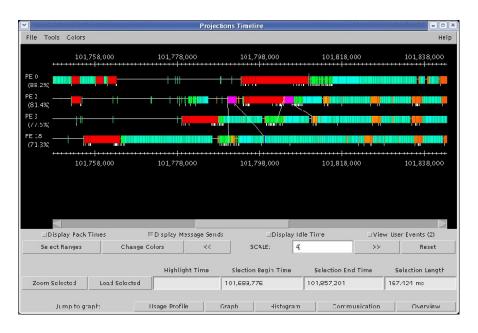

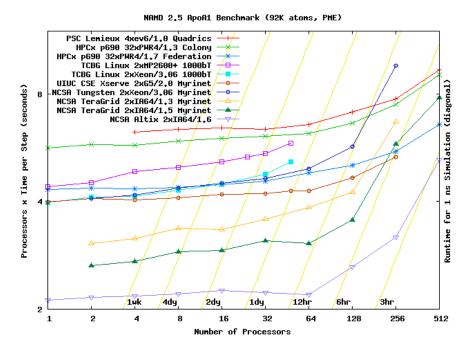

| 7.5  | NAMD sub-step load balancing with ApoA1 benchmark on Turing                            | 91  |

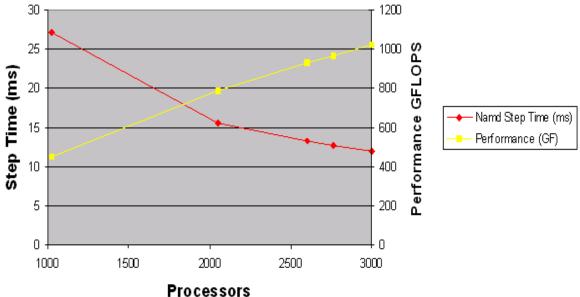

| 7.6  | NAMD Performance on 327K atom ATPase PME benchmark, on PSC LeMieux                     | 92  |

| 7.7  | NAMD Performance on various platforms with ApoA1 benchmark                             |     |

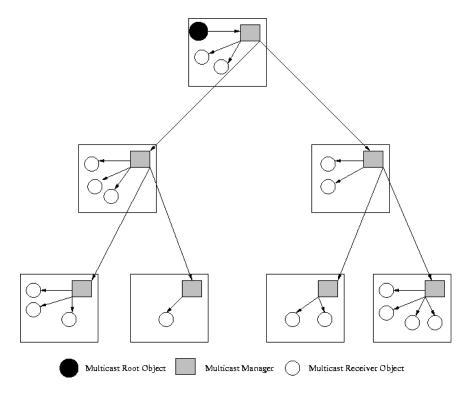

| 7.8  | Section multicast via a binary tree                                                    | 100 |

| 7.9  | Overview of a LeanMD 1-away simulation on 64 processors with GreedyLB                  | 103 |

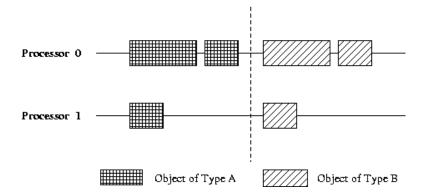

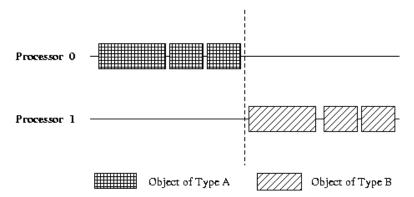

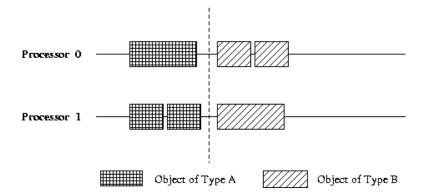

| 7.10 | Original timeline with mapping of objects on 2 processors                              | 105 |

| 7.11 | Timeline with bad mapping of objects on 2 processors after load balancing              | 105 |

| 7.12 | Timeline with better mapping of objects on 2 processors after load balancing           | 106 |

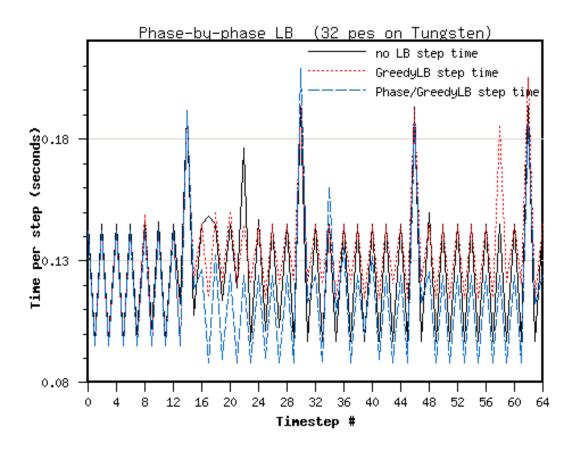

| 7.13 | A benchmark comparison of PhaseLB and GreedyLB                                         | 107 |

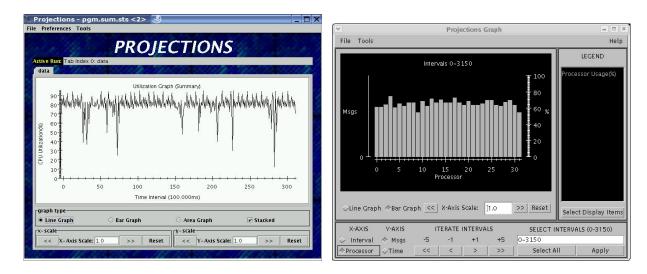

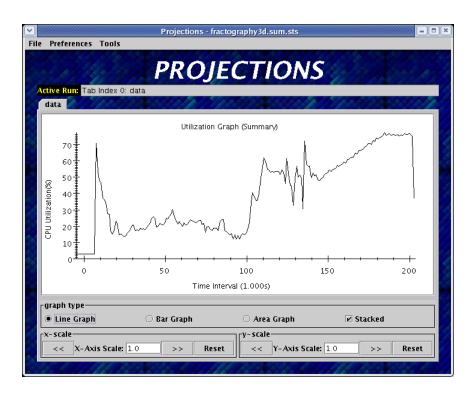

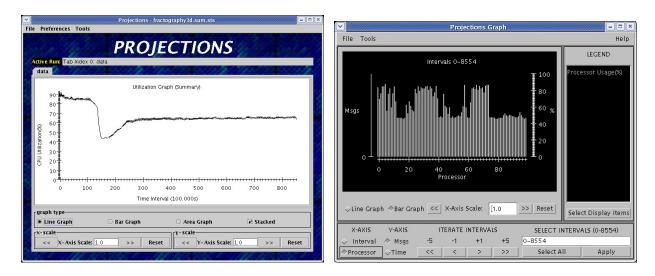

| 7.14 | Projections summary view of run without load balancing                                 | 108 |

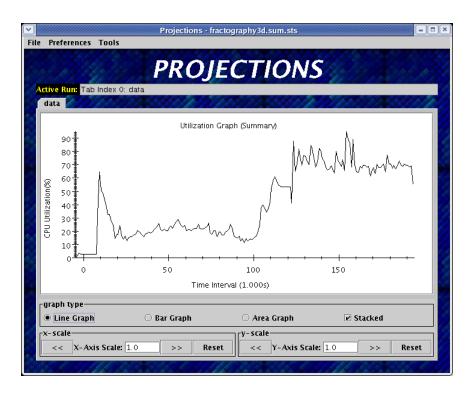

| 7.15 | Projections summary view of run with Greedy load balancing                             | 108 |

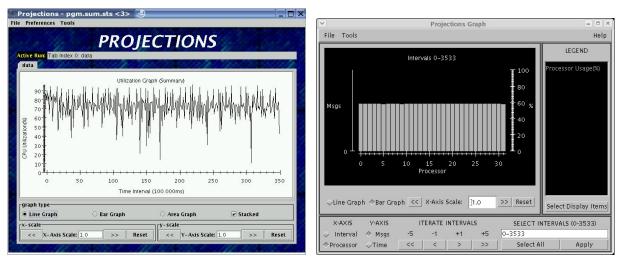

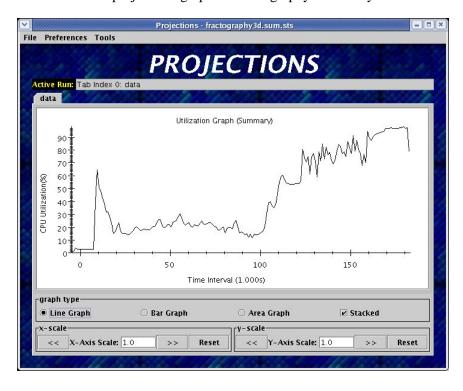

| 7.16 | Projections summary view of run with Phase load balancing                              | 109 |

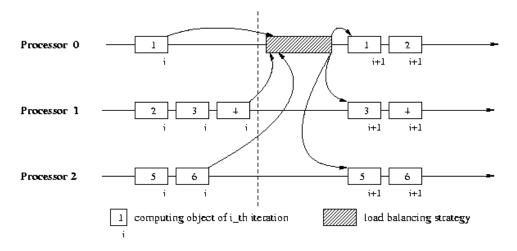

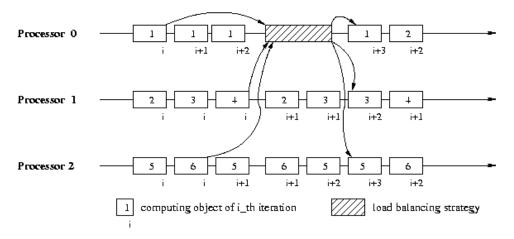

| 7.17 | Traditional synchronous load balancing                                                 | 111 |

| 7.18 | Asynchronous load balancing                                                            | 111 |

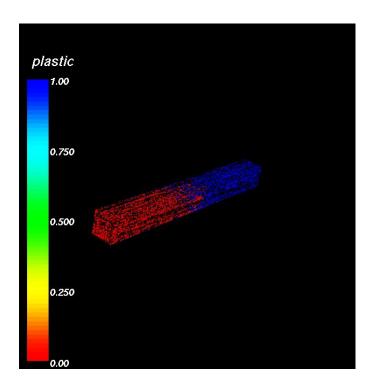

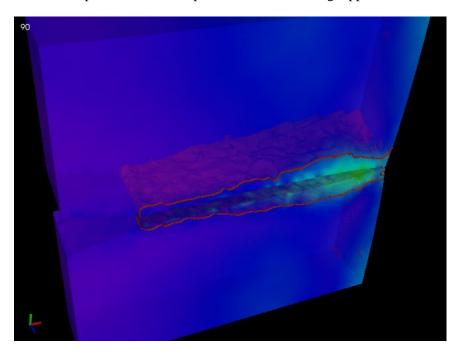

| 7.19 | Elastic bar turning into plastic with 1D force                                         | 113 |

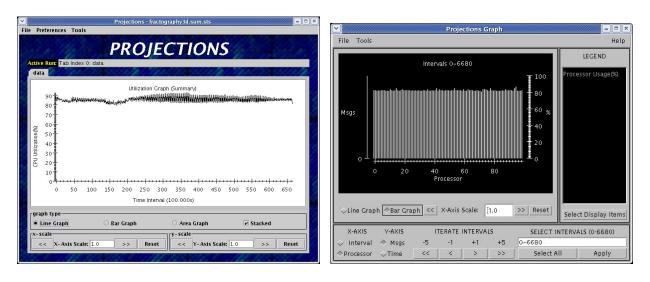

| 7.20 | CPU utilization projections graph of Fractography3D without load balancing             | 114 |

| 7.21 | CPU utilization projections graph of Fractography3D with synchronous load balancing 1  | 115 |

|      | CPU utilization projections graph of Fractography3D with asynchronous load balancing 1 |     |

| 7.23 | 3-D elastic-plastic fracture                                                           | 116 |

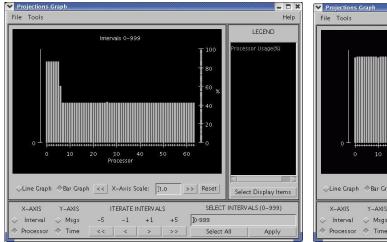

|      | CPU utilization projections graph of Fractography3D without load balancing             |     |

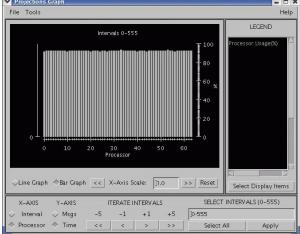

| 7.25 | CPU utilization projections graph of Fractography3D with load balancing                | 118 |

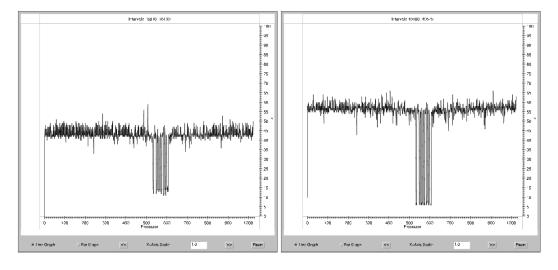

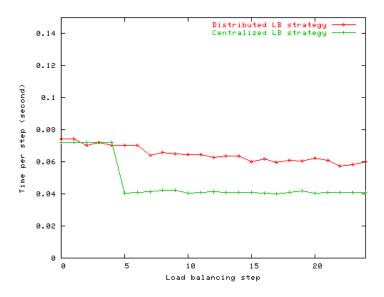

| 8.1  | Seed load balancing benchmark test                                                     | 124 |

| 8.2  | NAMD performance comparison between a distributed LB strategy and a centralized LB     |     |

|      | strategy                                                                               |     |

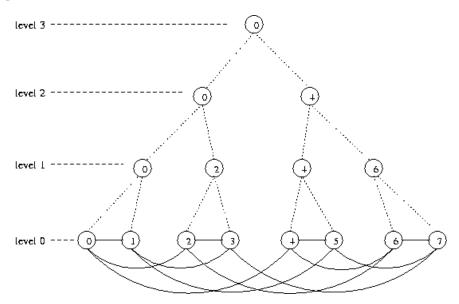

| 8.3  | Hierarchical organization of a 8-processor system with hypercube network               | 131 |

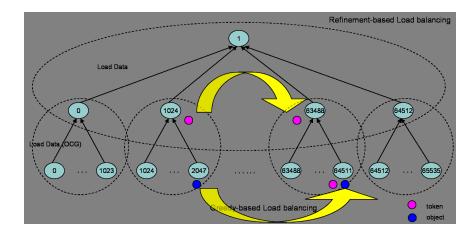

| 8.4  | HybridLB load balancing scheme                                                         | 137 |

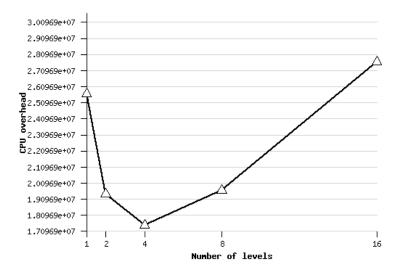

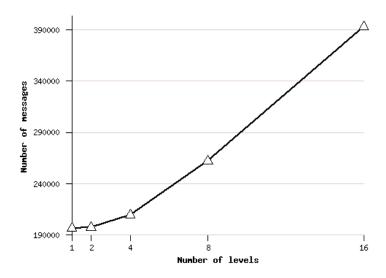

| 8.5  | Plot of CPU complexity over different levels                                           | 138 |

| 8.6  | Plot of number of messages over different levels                                       | 139 |

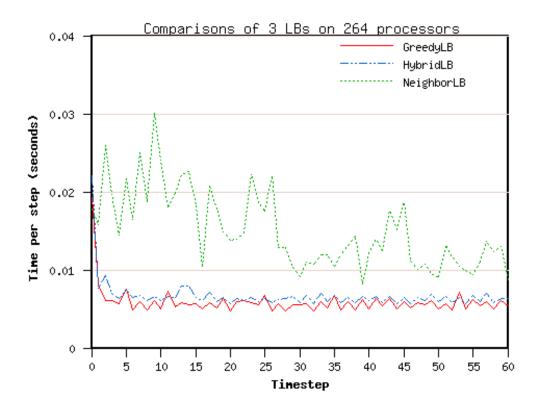

| 8.7  | Performance comparisons of three load balancers                                        | 144 |

| 8.8  | A hierarchical tree for 32K processors                                                 | 145 |

| 8.9  | A hierarchical tree for 64K processors                                                 |     |

| 8.10 |                                                                                        | 147 |

| 8.11 | Comparison of Maximum predicted load after load balancing on CentralLB HybridLB (2     |     |

|      | and 3 level) and HbmLB on 64K processors                                               | 148 |

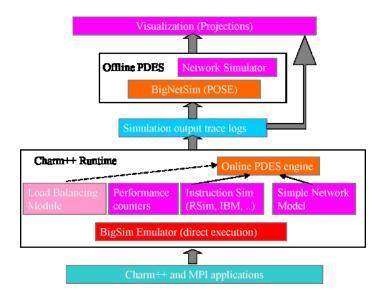

| 9.1  | The Architecture of BigSim System                                                      | 152 |

### **Chapter 1**

### Introduction

Emerging applications such as computational biology, computational cosmology, engineering design, earth-quake modeling and weather forecasting demand an unprecedented amount of compute power. Computer hardware designs have achieved incredible performance gains over the past half century, and the trend toward more powerful and cost-effective systems continues. As an example, the US Department of Energy's Advanced Simulation and Computing [3] (ASC) program has delivered a series of increasingly powerful platforms to the national laboratories, including ASC Red Storm (10K processors and 40 TFlops), Purple (12K processors and 100 TFlops), and BlueGene/L [5] (180/360 TFlops) by IBM has 64K dual-processor nodes. An earlier ambitious design from IBM, code-named Cyclops (Blue Gene/C), had over one million floating point units, fed by 8 million instruction streams supported by individual thread units, targeting 1 petaflops of peak performance. IBM has also revealed an ambitious program to further expand the horizons of supercomputing with the goal of creating a system called Blue Gene/P that can achieve one petaflop of peak performance.

### 1.1 Petaflops-class Machine Architectures

In this thesis, we focus on massively parallel machines which are capable of delivering petaflop level performance. There are two trends in the approach to building such big parallel machines. One trend is to build such machines with conventional powerful CPU chips and interconnects. The major challenges for this approach involve power, space, and monetary budgets. It would be impractical to attempt to achieve this level of parallelism using commodity personal computers, which dissipate hundreds of watts of power each, take a substantial amount of space, and cost hundreds of dollars per processor. Another trend is to

use new, low power consumption, multi-core chips with modest performance and integrated communication support. To attain petaflop performance with this approach will require an extremely large number — hundreds of thousands or even millions — of individual processors and they are likely to have relatively low memory-to-processor ratio. This will have an impact on performance and on the way the machines are programmed.

The communication hardware of peta-scale parallel machines may also differ from that of today's parallel machines. Since the large number of processors of a peta-scale machine have to be packed into 3D space, physical cabling limitations mean the machine's topology is likely to be a 3D mesh or torus. This means the cross-section bandwidth is likely to be relatively small, and the number of hops to traverse the machine relatively large. This, in turn, implies that machine topology may become an important factor in the design of parallel algorithms and their implementation, as in the academic research in early years of parallel computing [43].

IBM's Blue Gene/C [76] is an example of the class of peta-scale parallel machines. It aimed to reduce costs and the component count by fabricating several processors (25 in one design), along with their memory, onto a single chip, or *node* (so called system-on-chip technology). It also attempted to improve processor utilization by including eight hardware threads on each processor. Each node, then, has 200 hardware threads, which share only about 16 megabytes of memory. All threads in a node access the same memory, as in a conventional SMP. Communication between nodes is via explicit message passing, with nodes arranged in a 34 x 34 x 36 grid. The machine is designed with a petaflop of raw performance, a terabyte per second of cross-section bandwidth, and only half a terabyte of total memory. Although this design was not chosen for full-scale implementation, a similar design is being investigated within IBM on a smaller scale.

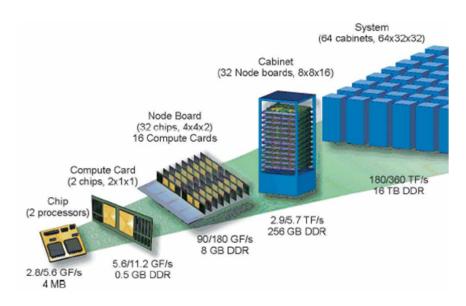

Blue Gene/L [5], another design from IBM that was implemented, is constructed based on a similar, custom system-on-chip compute node. Each compute node is a chip with 2 cores (700MHz PowerPC440), with 256MB of main memory, which is still small compared with conventional machines. The 64,000 compute nodes are organized in a 64 x 32 x 32 three-dimensional torus, packaged from compute cards, node boards, cabinets to the whole system as illustrated in Figure 1.1 <sup>1</sup>. The system can deliver 360 teraflops of peak performance.

These specifics are particular to IBM's Blue Gene machines, but the overall architecture—many multi-

<sup>&</sup>lt;sup>1</sup>taken from IBM Blue Gene website: http://www.research.ibm.com/bluegene/

Figure 1.1: Blue Gene/L architecture (taken from IBM Blue Gene website)

processor single-chip nodes connected via message passing on a packet-switched 3D mesh—is likely to be the most cost-effective way to build any very large-scale machine.

### 1.2 Software Challenges

The development of parallel applications for petaflop machines is a significant challenge. It may require qualitative changes to the way we write parallel programs in order to exploit the enormous compute power, as well as changes to the way we understand and analyze the performance.

- It is very challenging to write scalable peta-scale applications using conventional programming models such as MPI, shared memory and data parallel programming languages because of the massive parallelism involved in these applications. Many scientific applications requires tightly coupled physical components, which may lead to tremendous amount of fine-grained communication among them and make the applications difficult to scale. The conventional programming models do not focus on an intelligent run-time on how to fully utilize a peta-scale parallel system.

- Molecular dynamics simulations are one of the target applications for massively parallel machines such as Blue Gene/L. These applications have very fine-grain parallelism because each time-step only involves a few seconds of sequential computation time. In order to achieve scalability on such machines, each time step needs to be parallelized into sub-millisecond of computation and commu-

nication. This implies that no software component in the parallel program can exceed this amount of time on each processor in order to achieve the desired level of performance. This again requires an intelligent run-time for resource management such as load balancing.

- Multiple interacting factors could result in performance degradation for applications on peta-scale machines. These factors include inappropriate problem decomposition, communication latencies, operating system interference, critical paths and load imbalance. Although similar performance problems apply on existing small scaled parallel machines, they tend to be magnified on peta-scale machines. Among the degradation factors, load imbalance problems are particularly significant and are quite challenging to solve given the scale of the machines. In fact, many other performance problems such as communication latencies and OS interference can turn into load imbalance problems, making load imbalance the main symptom of all performance problems. Expecting the application programmers to deal with these issues manually will be unrealistic and unproductive. Automated support via run-time system is therefore essential.

- It is especially difficult to understand how an application will perform on a peta-scale machine when the target machine is not even operational. Parallel performance is hard to model without actually running a program. Even when a machine is operational, large-processor runs are not available as often as needed. In this scenario, a parallel performance simulator is desirable and necessary as a tool for studying application performance issues. Developing such a large scale parallel performance simulator, however, is quite challenging due to the scale of the target machines simulated.

### 1.3 Approach

In this thesis, we propose, explore, and substantiate the following hypothesis:

employing migratable objects (processor virtualization) for programming peta-scale machines supported by parallel emulation for algorithm validation, and parallel simulation for performance prediction, and using new kinds of load balancing strategies

will substantially address many of the challenges for programming petaflops class machines (described in Section 1.2).

We explore the Charm++ parallel object programming language with a data-driven execution paradigm as an alternative programming model on peta-scale parallel machines. Adaptive MPI, an MPI implementation on Charm++, enables us to apply our approach to the popular message-passing paradigm, retaining the advantage of processor virtualization.

To study how an application performs on a peta-scale machine, we adopted the simulation-based approach for performance prediction of parallel applications. We explore an optimistic synchronization approach with run-time optimization to provide a simulation based framework for studying parallel performance issues on very large parallel machines. We demonstrate that by taking advantage of user-level threads, and aggressive optimizations that reduce PDES synchronization overhead using a method that combines both language and run-time, we are able to predict parallel performance of applications on very large parallel machines with tens of thousands of processors.

With the infrastructure of the parallel simulator, we study the parallel performance of several important applications and explore dynamic load balancing techniques to improve the scalability of parallel applications in general. We develop a spectrum of sophisticated centralized load balancing strategies and achieve excellent performance for applications on modestly large parallel machines with up to several thousand processors. We further explore a category of new load balancing schemes suitable for very large scale parallel machines.

### 1.4 Contributions

This thesis aims at developing techniques and methods to facilitate the development of peta-scale applications. The main contributions of the dissertation include the following:

- Processor virtualization is a useful technique which makes it feasible for a programmer to write applications with high degree of parallelism that is often needed for programming peta-scale machines. We demonstrate it with several mini-applications with million-way parallelism. We show that Charm++ and AMPI (an extension to MPI), which embody the idea of processor virtualization, are suitable programming model for programming peta-scale machines.

- A parallel simulator: We have developed a parallel simulator that is capable of predicting parallel performance to help analysis and tuning of the parallel performance. The parallel simulator adopts

parallel discrete event simulation techniques with an optimistic synchronization protocol. Such a simulator involves very fine-grain messages leading to prohibitive communication and simulation overhead. With the idea of extensively exploiting the *inherent determinacy* in parallel applications, we are able to reduce the synchronization overhead and improve the scalability of the simulator. We demonstrate the scalability of the parallel simulator by case studies of simulating a parallel molecular dynamics simulation program on a 64K processor machine.

- An enhanced load balancing framework to address the load-balancing needs of many different types of applications. It provides automatic dynamic load balancing with little user intervention. The framework performs automatic measurement of object computation times and communication patterns including collective communication, without adding undue overhead. We optimized load balancing strategies in multiple dimensions of criteria such as load balancing for improving communication locality, sub-step load balancing, and computation phase-aware load balancing.

- We demonstrate the value of these techniques by applying our load balancing framework to several real-world applications, resulting in improved performance even for applications that were difficult to balance the load. NAMD, a production quality parallel molecular dynamics program written in CHARM++, achieved the highest reported speedup on LeMieux with 3000 processors with joint work with other group members, which won the Gordon Bell award at SC2002 for the outstanding performance.

- A load balancing strategy for very large parallel machines. This thesis presents a parallel adaptive hierarchical load balancing strategy that works effectively on very large parallel machines. Having application developers provide load information is unrealistic for such large scale applications. This hierarchial load balancing strategy builds load data from instrumenting an application at run-time on both computation and communication pattern in a fully automatic way. It also incorporates a cost function to explicit control the memory overhead of load balancing to make it easy to adapt to extremely large number of processors with even small memory footprint. Our simulation of the load balancing algorithm on a machine of 65,536 processors shows that the algorithm achieves good load balance with optimization of application communication taking into account. The results also demonstrate that the parallel load balancing algorithm runs efficiently on large machines.

### 1.5 Dissertation Outline

Chapter 2 introduces the Charm++ parallel programming language, the features that make it well suited for programming very large parallel machines, and the advantages from automatic load balancing. Chapter 3 presents the design of the BigSim parallel emulator, its performance and its utility. In Chapter 4, we present the PDES techniques we used for extending the emulator for predicting parallel performance of applications on very large parallel machines. We demonstrate the techniques used by CHARM++ to help writing applications with million-way parallelism in Chapter 5. We also present performance study via simulation of a molecular dynamics simulation program and a Finite Element Methods simulation program in the same chapter. Chapter 6 presents an overview of Charm++ load balancing framework and its load balancing methodology for dealing with dynamic load balancing problems, and Chapter 7 presents the performance optimization techniques in centralized load balancing with sophisticated load balancing strategies. Chapter 8 discusses the limitations of current centralized and distributed load balancing strategies on peta-scale parallel machines, and presents a new hybrid load balancing strategy that combines the benefits of the centralized and distributed strategies. Chapter 9 gives the conclusion of the thesis and discusses the future work.

### Chapter 2

# CHARM++/AMPI and Processor Virtualization

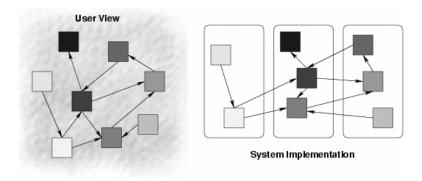

Charm++ [49] is a parallel programming and runtime system that supports processor virtualization [53, 52]. In Charm++, an application divides a problem into a large number of components (N) (implemented as C++ migratable objects or user-level threads) that will execute on P processors and act as the *virtual processors*. N is independent of P though ideally N>>P. The basic mechanism in processor virtualization that enables transparent migration of data is to provide applications a *location independent* view of the world. In a Charm++ application, the user's view of the program consists of these components and their interactions; the user need not be concerned with how the components map to processors. The underlying run-time system takes care of this and any subsequent remapping (see Figure 2.1).

Figure 2.1: Virtualization in CHARM++

In Charm++, these components are known as *chares*. Chares are C++ objects with methods that may be invoked asynchronously from other chares. Since many chares can be mapped to a single processor, Charm++ uses *message-driven execution* to determine which chare executes at a given time.

Objects or chares that carry application code are location independent. Hence chares can migrate from processor to processor freely. One application of migratable objects is load balancing. Objects can migrate from overloaded processors to underloaded processors to achieve better load balance. In order to migrate an object, one needs to pack the data of the object into a message. The message is sent to another processor where the data is unpacked and the object is restored. The Charm++ PUP framework [45] was designed to describe the in-memory layout of an object. The object migration based on the PUP framework can be extended into broader usage, such as migrating an object to disk at runtime for out-of-core execution. In the checkpointing scenario, when an object is checkpointed, it is simply packed and migrated to another location (memory or disk).

Adaptive MPI, or AMPI [42] is an MPI implementation and extension based on Charm++. AMPI implements virtual MPI processes, or VPs, using migratable user-level threads, several of which may be mapped to a single physical processor. AMPI supports adaptive load balancing by migrating MPI threads. Several schemes of fault tolerance support are implemented in Charm++ and AMPI. They range from a synchronous on-disk checkpoint/restart mechanism [41] and a scalable in-memory checkpoint scheme[94], to an automatic fault-tolerant protocol for massively parallel systems [25]. MPI is a special case of AMPI when exactly one VP is mapped to a physical processor.

### 2.1 Charm++ vs. Conventional Programming Models

Conventional models such as message passing, shared memory and data parallel programming need a lot of programmer effort to efficiently utilize a peta-scale machine due to problems with load balance, locality, and parallelism. Charm++, as a parallel object programming model, has several advantages compared to these conventional models.

Charm++'s parallel objects provide a degree of freedom to the run-time system that is very helpful for programming peta-scale machines. In this model, the programmer specifies the decomposition of the problem only in terms of interacting objects, and the run-time system handles mapping (and remapping) these objects to processors. Thus, in the programmer's view, object A invokes a method in object B, but the programmer doesn't know or care which processor object B resides on. Several different objects are often mapped to a single processor, and scheduling within a processor is accomplished via a message-driven non-preemptive scheduler. The scheduler selects a method invocation (also called a message) from the queue,

identifies the object it is intended for, and invokes the method. When the method invocation returns, the scheduler picks the next message.

Objects may even migrate from processor to processor at runtime, usually under the control of a system-supplied load balancer. Message forwarding may be required after a migration, but the system uses a routing scheme that asymptotically requires only 1 hop (i.e. no indirection) for any kind of repeated communication [65].

For a peta-scale machine, locality is extremely important because of the potentially high cost of accessing remote data (on a large diameter topology). Thus, object-based decomposition is particularly attractive because it models locality well. Objects encapsulate state, and Charm++-style objects are allowed to directly access only their own local memory. They may make direct calls to other objects guaranteed to be on the same processor, and access read-only data that is accessible to all objects. However, access to any other data (e.g. data in other objects) is only possible via asynchronous method invocation. This enforces locality in a clear manner, and the programmer is aware of the cost of accessing remote data.

The flexibility provided by this object model is a key to the high performance attained by Charm++ based applications which had been hard to parallelize otherwise, as shown with NAMD [21]. Charm++'s automatic load balancing, based on measurement of computation loads and communication patterns among objects, can lead to significant improvements in performance with very little additional effort by the programmer. This is especially true for adaptive applications, which change their computational characteristics with time. In Charm++, load balancing can be handled by the run-time system, without changing the programmer's view of his applications. Thus, only the load balancing run-time needs to be changed for a peta-scale machine, which can simultaneously improve performance and reduce programmer effort. Chapter 6 will describe the CHARM++ load balancing framework in more detail.

Load balancing on peta-scale is more difficult than load balancing conventional machines. As an example, when mapping objects to processors on machines with hundreds of processors, it is often possible to ignore the number of hops traveled by messages. This is because the latency is almost independent of the number of hops due to modern techniques such as wormhole routing, and the impact on bandwidth utilization is limited. For a machine with 40,000 nodes, where cross-processor messages require many hops, the bandwidth used in the intermediate links becomes a significant concern.

In order for load balancing run-time to work efficiently, an application needs to be decomposed into

more fine-grained tasks than the number of processors. One of the questions that arises while programming peta-scale machines is how to generate the large amount of parallelism needed to occupy the millions of processors. The object model allows a solution: since the users decompose the problem into objects, and since they decide the granularity of objects, it is easy to generate parallelism. The object model imposes no arbitrary restrictions on the decomposition, such as the requirement that the problem be decomposed into as many pieces as processors often encountered in other models. In Chapter 5, we will demonstrate the usefulness of the object model in creating an application with million-way parallelism.

### Chapter 3

# **Dealing with Very Large Parallel Machines**

Parallel machines with tremendous computation power are being built with surprising speed. However, it is very difficult to understand how an application might behave on such large machines, and it may be hard to validate the correctness of a parallel algorithm without actually running the application.

In this chapter, we explore the idea of using a parallel emulator to mimic a class of peta-scale machines and support very large scale parallelism. We then use Charm++ as an example of utilizing the emulator for supporting high level parallel programming models for peta-scale machines.

Emulating a peta-scale machine with millions of processors on a much smaller parallel machine with limited resource presents many challenges. We explore the idea of applying processor virtualization with user-level threads in CHARM++ run-time on a scalable efficient parallel emulator. The emulator we present here also represent our first step towards a parallel simulator that is capable of predicting performance of parallel applications. We will present our parallel simulator in Chapter 4.

### 3.1 Need for Emulator of Very Large Parallel Machines

An emulator, by definition, is a device, computer program, or system that accepts the same inputs and produces the same outputs as a given system. In our case, the purpose of an emulator is to emulate a parallel message passing application as if it executed on a very large parallel machine. It does not have to produce performance information about the run.

An emulator for a peta-scale machine is necessary especially when the target machine is not yet operational. Even when the machine is operational, the access to the machine may be restricted and compute time is difficult to get in order to debug parallel applications. Thus, an emulator provides a nice way to debug a parallel application and validate the algorithm offline.

### 3.2 Methodology

Emulating the execution of a parallel program on a machine with tens of thousands of processors is not trivial. Directly running an application, for example with:

#### "mpirun -np 64000 ./app"

on a small cluster certainly is infeasible due to the limitations of operating systems, such as, on the number of processes allowed to be created. In order to emulate such a machine, one processor of a host machine needs to emulate multiple target processors.

To develop such a large scale emulator, we extended the idea of *processor virtualization* into a two-level virtualization. At user level, a program computation is divided into a large number of chunks (so called virtual processors), which are mapped to simulated processors by an adaptive, intelligent runtime system. At emulation level, these simulated processors are mapped to actual physicial processors by the same runtime system. The simulated processors are represented by CHARM++ user-level migratable threads, which are treated as another level of virtualization. This approach allows us to exploit the powerful run-time system of CHARM++ to achieve high scalability of the emulation.

We designed and implemented a parallel multi-threaded emulator called **BigSim Emulator** that mimics *low level* hardware and message passing primitives to facilitate the execution of very large scale parallel applications. The low level functional API provided by the emulator is designed to be general enough for a wide variety of parallel machines. With such low level primitives, a user can write parallel applications running on the emulator. However it requires a lot of effort in writing such applications. Thus, the need for high productivity requires high level parallel programming languages. We demonstrate the use of emulator for developing high level languages using Charm++ and AMPI as examples.

### 3.3 Parallel Emulator

In order to emulate a future massively parallel machine on an existing parallel machine with only hundreds of processors, one physical processor has to emulate hundreds or even thousands of processors of the target machine. One question arises - is it feasible to emulate an application on machines with such scale in terms

of memory and CPU cost? We believe the emulation is still possible because:

- Although the overall compute power of peta-scale machines is enormous, they are likely constructed based on compute nodes with modest performance. Thus it is feasible to conduct the simulation for a short run.

- Some planned machines such as BlueGene/C have low memory-to-processor ratio. BlueGene/C was

originally designed to have about half a terabyte of total memory. However, each chip with 25 processors shares only 12MB of memory. Thus, to emulate BlueGene/C running an application which

uses the full machine will require "just" 500 processors of a traditional parallel machine with 1GB

memory per processor.

- For planned machines with high memory-to-processor ratio, no existing parallel machine has enough

memory to simulate the full machine. However, many real world applications such as molecular

dynamics simulation do not require a large amount of memory.

- For applications that do require a large amount of memory, it is still possible to use automatic out-of-core execution [73] to temporarily move the data in memory to disk when it is not needed immediately. This swapping slows down the simulation. However if the only thing we are interested in is the *predicted* running time which need not be affected by swapping time, for a few timesteps, this slowdown is still acceptable.

In order to support high degree of parallelism, we designed a low level abstraction of peta-scale machines to provide access to a machine's capabilities. In the programmer's view, each node consists of a number of hardware-supported threads with common shared memory. A runtime library call allows a thread to send a short message to a destination node. The header of each message encodes a handler function to be invoked at the destination. A designated number of threads continuously monitor the incoming buffer for arriving messages, extract them and invoke the designated handler function. We believe this low level abstraction of the peta-scale architectures is general enough to encompass a wide variety of parallel machines with different numbers of processors and co-processors on each node.

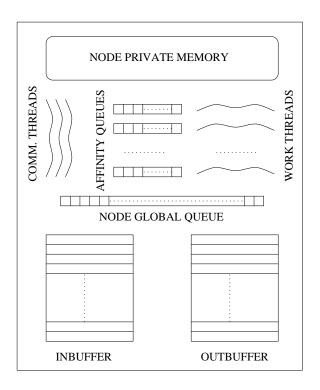

We have developed a software emulator [76] based on this low level abstraction. The emulator can be easily configured for specific target machines. Figure 3.1 describes the functional view of an emulated

Figure 3.1: Functional view of an emulated node

node. Within a node, we divide threads into worker threads and communication threads. Communication threads check incoming messages from the network and put the messages in either a worker's queue or a node global queue. Worker threads repeatedly retrieve messages from the queues and execute the handler functions associated with the messages.

The emulator provides a function API for setting up the emulated machine configurations and providing functions for message passing. The details of the API definitions are described in next section.

#### 3.3.1 Emulator Function API

Emulator API includes the following function definitions:

- *void BgNodeStart()* is called by the runtime system to initialize each node. Here, application handlers are registered, and the computation is started by creating tasks for the specified nodes.

- int BgRegisterHandler(BgHandlerFn h) is invoked to register a handler function with each node and returns a globally unique identifier associated with it.

- *void BgAddMessage(int threadID, int handlerID, int nBytes, char \*msg)* is called to schedule a message for execution on the local target node specified by the threadID.

- void BgSendPacket(int x, int y, int z, int threadID, int handlerID, WorkType type, int nBytes, char \*data) is used to send a message to a node at location [x,y,z] in the node grid. ThreadID can be used to direct a task to a thread, otherwise any thread in the node can handle the message.

- Utility functions In addition, the emulator supports several utility functions that allow access to timers, the identity of the node and the processor on which the invoking thread is running, and other housekeeping data.

The above API has the advantage of being small yet complete. Other functions, such as "send", and "receive", as well as high-level models can be built on top of this simple layer.

### 3.3.2 Emulating Hardware Processors

The number of processors of a target parallel machine typically is far larger than the size of the simulating parallel machine, thus multiple processors of target parallel machines are emulated using multiple flows of control running on a single simulating processor. A flow of control is a single sequential stream of executed instructions, including subroutine calls and returns. The performance and limitations of such flow of control mechanisms determine if the emulation of a petascale machine is feasible or not.

Many mechanisms are available for supporting multiple flows of control. We evaluated three specific mechanisms: processes, kernel-space threads and user-space threads.

#### • OS-level Processes

Process is the simplest and oldest flow of control. It wraps a complete address space around a flow of control. The drawback of using processes for emulation is that processes are considered "heavy-weight": it is expected that the substantial amount of process kernel state increases the amount of memory used by each process, increases the overhead of process creation and switching, and leads to hard limits on the number of processes that can be created in a user program.

#### • Kernel-space Threads

Kernel threads consist of a set of registers, a stack, and a few corresponding kernel data structures.

Unlike processes, threads within a process all share the same address space. All modern machines support kernel-space threads, most often via the POSIX threads interface (known as *pthreads*).

Kernel-space threads often are implemented in the kernel using several tables (each task gets a table of threads). In this case, the kernel schedules each thread within the timeslice of each process. There is a little more overhead with mode switching from user  $\rightarrow$  kernel  $\rightarrow$  user and loading of larger contexts. The advantages of kernel-space threads over processes is faster creation and context switching.

### • User-space Threads

User-space threads avoid the kernel and manage the tables themselves. Often this is called "cooperative multitasking" where the task defines a set of routines that get "switched to" by manipulating the stack pointer. Typically each thread "gives-up" the CPU by calling an explicit *yield* call, sending a signal or doing an operation that involves the switcher. User threads typically can switch faster than kernel threads. <sup>1</sup> Many implements of user-level threads exist, including Gnu Portable Threads (GNU Pth [4]), and Converse threads (*CthThreads*).

Converse threads, or CthThreads, are based on various thread packages and implementations that depend on what is available on the platform. CthThreads include QuickThreads [62] <sup>2</sup>, context threads based on *getcontext/setcontext* system calls <sup>3</sup>, Windows NT Fiber, etc.

User-space threads in general have several advantages over the other two flow of controls in the implementation the emulator for very large number of processors. First, the usage of processes and kernel-space threads is limited by various system constraints. As illustrated in Table 3.1 with some of the experiments conducted by Orion Lawlor in our group, both processes and pthreads creation are often limited by system configuration and kernel, for which a normal user often does not have control. Our experiments have shown that there is wide variation in the limitations and the performance of these methods on different machines. For example, an unmodified Linux Red Hat 9 machine can spawn no more than 256 pthreads; meanwhile the per-user process limit on an IBM SP was only 100 processes. By contrast, we could create tens of thousands of user-level threads easily on all platforms.

<sup>&</sup>lt;sup>1</sup>however, Linux kernel threads' switching is actually quite close in performance.

<sup>&</sup>lt;sup>2</sup>QuickThread was first implemented by David Keppel, it was further extended by various members of our group including myself.

<sup>&</sup>lt;sup>3</sup>Context thread based CthThreads were implemented by myself.

| Flow of control    | Limiting Factor | Linux  | Sun    | IBM SP | Alpha  | Mac OS | Itanium |

|--------------------|-----------------|--------|--------|--------|--------|--------|---------|

| Process            | ulimit/kernel   | 4000   | 5000   | 100    | 1000   | 500    | 50000+  |

| Kernel Threads     | kernel          | 250    | 3000   | 2000   | 50000+ | 7000   | 30000+  |

| User-level Threads | memory          | 50000+ | 20000+ | 10000+ | 20000+ | 15000+ | 50000+  |

Table 3.1: Approximate practical limitations (on stock systems) for various methods to implement flow of control.

Second, stack size usage of the threads or processes has a great impact on the emulation if the emulated system is very large. As the simple calculation in Table 3.2 reveals, an unnecessarily large stack size can increase the total memory footprint dramatically, especially for a small simulating cluster with only limited number of nodes available. In general, it is infeasible or non-portable to set stack size for a process or pthreads <sup>4</sup>. However, user level threads allow a user to easily control the stack size of each thread. In practice, we found that a 10KB stack size is sufficient for most emulations that do not allocate big data structure on stack.

|                       | Number of Emulated Processors |      |      |       |       |  |

|-----------------------|-------------------------------|------|------|-------|-------|--|

| Stack Size per Thread | 16K                           | 32K  | 64K  | 128K  | 256K  |  |

| 64KB                  | 1GB                           | 2GB  | 4GB  | 8GB   | 16GB  |  |

| 128KB                 | 2GB                           | 4GB  | 8GB  | 16GB  | 32GB  |  |

| 1024KB                | 16GB                          | 32GB | 64GB | 128GB | 256GB |  |

Table 3.2: Total memory needed for a number of emulated processors with various stack sizes of a control flow

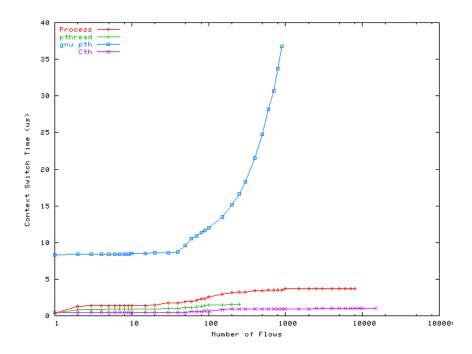

Third, the context switch overhead is an important factor in the emulator efficiency. We examined the context switch performance of three different implementations of flow of control:

- 1. Processes, created using fork() and yielding using sched\_yield().

- 2. Pthreads, created using pthread\_create() and yielding uysing sched\_yield().

- 3. Converse threads, user level threads created using CthCreate() and scheduled using CthYield().

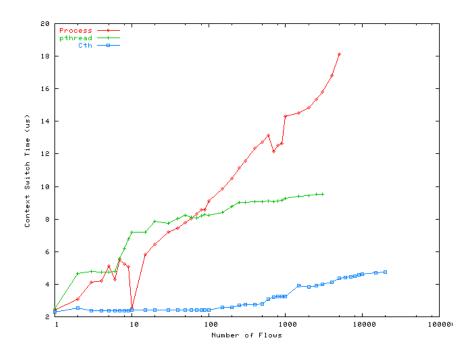

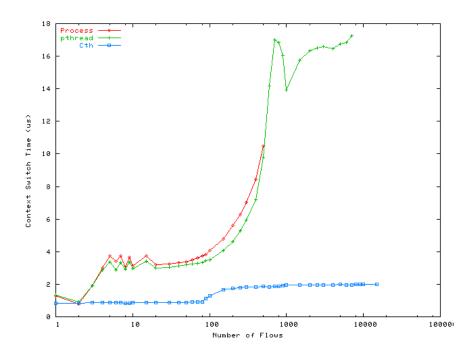

We run tests on a variety of platforms including Linux (Figure 3.2), Sun Solaris (Figure 3.3) and Mac OS (Figure 3.4). Our experiments show that our Converse user level thread implementation generally is much more efficient in context switching performance.

<sup>&</sup>lt;sup>4</sup>pthread\_attr\_setstacksize() can set pthread stack size, however it is not supported on some platforms such as the IA64

Figure 3.2: Context switching time vs. number of flows on a x86 Linux machine.

In summary, using user level threads (CthThreads) to emulate hardware processors has the following advantages over processes and kernel-space threads:

- 1. CthThreads are highly portable. Currently, they run on all popular parallel systems including Blue Gene/L and even on Windows PC.

- 2. Using CthThreads avoids potential system limitations that processes and kernel threads may have on the number of flows of control allowed to create.

- 3. Thread stack is explicitly managed in the CthThreads implementation; reducing an unnecessarily big stack size helps reducing memory usage in the emulation.

- 4. CthThreads generally have faster context switching time. This improves the emulation performance significantly because an emulation normally involves a very large number of target processors and threads emulating them.

Ideally, a standard API and a skeleton for user-level threads would be supported in the future by OS and compilers.

In [76], we demonstrated that using CthThreads our emulator enables us to model Blue Gene/C nodes

Figure 3.3: Context switching time vs. number of flows on Sun Solaris machine.

organized in a 34 x 34 x 36 grid with 200 threads per node (i.e. 8M threads) on 96 physical processors of ASCI-Red. This involves creating approximately 80,000 user-level threads per ASCI-red processor.

#### 3.3.3 Emulator Performance

In this section, we will present two case studies. The first case study is on the emulation performance using user level threads (CthThreads) compared with the kernel threads (pthreads) in emulator implementation to illustrate the advantage of using CthThreads. The second performance study demonstrates the scalability of our emulator.

### Performance Comparison between CthThreads and Pthreads

To demonstrate the performance benefit of using CthThreads, we compared the performance of emulation using Pthreads and CthThreads to emulate target processors.

We ran an emulation of a parallel Jacobi program on one physical processor of a SUN machine at CSAR [2] using CthThreads and Pthreads and compared the total time taken for the emulation. Since the number of pthreads one can create on a SUN machine is only about 3000 (given stack size of 128KB), in the experiment we only emulated target machines of up to 2000 processors.

Figure 3.4: Context switching time vs. number of flows on Mac machine.

| Number of PEs emulated | 250  | 500  | 1000  | 2000  |

|------------------------|------|------|-------|-------|

| Pthreads               | 7.73 | 9.59 | 13.95 | 30.42 |

| CthThreads             | 3.33 | 4.49 | 7.4   | 15.67 |

Table 3.3: Emulation time (in seconds) using CthThreads and Pthreads with BigSim emulator

The result is shown in Table 3.3. The emulation time shown in the table is the total time spent on the whole emulation, including the context switching time. As can be found in Figure 3.3, when there are 2000 flows of control, the CthThreads context switching time is about 3.8us, and the Pthreads context switching time is about 9.5us. The difference in context switching cost leads to significant performance improvement in emulation achieved by using CthThreads.

#### **Parallel Emulator Scalability**

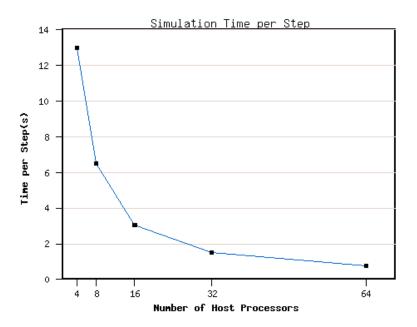

Our BigSim emulator demonstrates good scalability. We ran a molecular dynamics (MD) simulation code

— LeanMD — to emulate a Blue Gene like machine with 200,000 processor on LeMieux at PSC <sup>5</sup>. We

measured the time taken to emulate one timestep of the MD simulation using 4 to 64 LeMieux processors.

The result is shown in Figure 3.5, which demonstrates excellent scalability of the emulator in this test. In

<sup>&</sup>lt;sup>5</sup>LeMieux is 750 Quad Alphaserver ES45 node machine at Pittsburgh Supercomputing Center (PSC)

fact, there is a superlinear speedup of 67 over 64 processors (normalized by the 4 processor time). This is due to a smaller memory footprint per physical processor as the number of processors is increased, with corresponding caching effects.

Figure 3.5: Simulation Time per Step

### 3.4 Porting High Level Parallel Languages to the Emulator

We implemented the CHARM++ programming model on the BigSim emulator to enable the study of performance and scalability of a peta-scale machine [95]. In short, we call this implementation of CHARM++ as **BigSim** CHARM++. In this section, we describe some design issues involved in the implementation of CHARM++ on top of the emulator, along with some optimizations to improve the efficiency of CHARM++ and the emulator.

#### 3.4.1 Design Issues

In CHARM++, the programmers do not concern themselves with which processor an object resides on. In the implementation, however, objects have to be mapped to processors by the CHARM++ run-time system (RTS). Furthermore, CHARM++ semantics requires that two methods of an object never execute concur-

rently (method atomicity). In normal implementations, CHARM++ groups together the objects and threads that reside on the same processor. On each processor, there is one non-preemptive scheduler responsible for scheduling messages and doing method invocations associated with messages, which ensures atomicity. Even on machines with SMP nodes, the CHARM++ RTS divides the objects by processor and schedules each processor separately, rather than using one shared scheduler. This guarantees method atomicity. For CHARM++ on BigSim emulator, we considered two alternative strategies to guarantee atomicity.

- 1. Treating an entire emulated node (with many processors and possibly hundreds of threads) as a single CHARM++ processor. When a message is sent to a CHARM++ processor, the emulator's communication threads can schedule the message to any worker thread. This requires using locks on objects to ensure that two method invocations do not execute concurrently. However, no such locking is necessary during emulation, since all the threads on a peta-scale machine node are mapped to a single emulator processor, where there is no preemption.

- 2. Treating each worker thread in an emulator as a CHARM++ processor. Chare objects are anchored to individual threads. When a message arrives, it will be scheduled into the affinity queue of the worker thread specified by the message. This approach may require explicit load balancing of work among threads of a node.

Both schemes are implemented in CHARM++ on the emulator. However, the first scheme has an advantage that it needs a smaller amount of memory for per-processor data structures maintained by the CHARM++ run-time system.

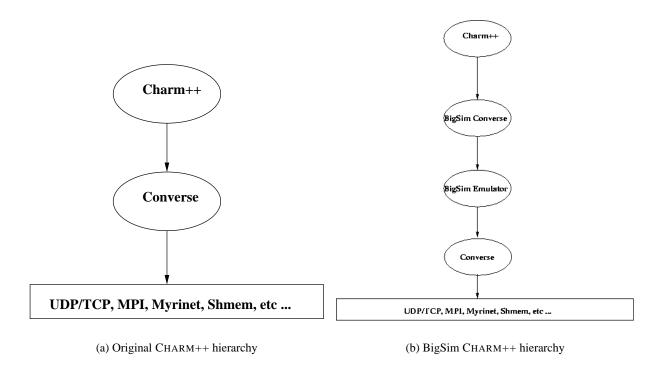

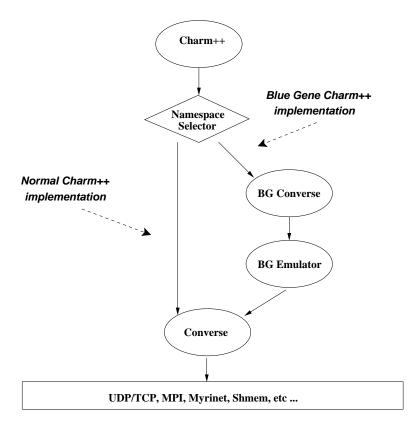

CHARM++ is implemented using the Converse layer as shown in Figure 3.6(a). The Converse run-time framework provides portable, efficient implementations of all the functions typically needed by parallel applications. For example, it provides a common interface to the machine dependent implementations of thread creation and message passing.

For BigSim CHARM++, we need a Converse layer (BigSim Converse) that is implemented on the BigSim emulator API, to provide the same functionality of the original Converse. However, the emulator that this BigSim Converse is built on is implemented itself upon the original Converse. Figure 3.6(b) illustrates the new BigSim CHARM++ hierarchy. It shows that the Converse layer is used in two contexts: in one place to represent the real machine — Converse; and in the other place to represent the virtual emulated

Figure 3.6: CHARM++ hierarchy

machine — BigSim Converse.

While the two uses of Converse share the same interface, the implementations are completely different. For example, *Processor Private Variables* in the Converse layer are private to each real physical processor, while in BigSim Converse, Processor Private Variables are private to each BigSim emulated node. This causes significant name conflict problems.

To solve these problems, we separated a component layer from Converse that consists of all Converse calls used by CHARM++ runtime. Fortunately, CHARM++ only needs a small subset of the entire Converse API. We then implemented this layer on the BigSim emulator. A similar implementation, consisting of simple wrappers, was created for normal Converse as well. Both of these were encapsulated in different *name spaces*. This layered implementation is shown in Figure 3.7. Using C++ namespaces, the CHARM++ runtime can now easily switch between the BigSim Converse and the normal Converse. This greatly simplifies the implementation while allowing two versions of CHARM++ to coexist in one system. This is an example of what a routine in the BigSim Converse version looks like:

```

namespace BGConverse {

```

Figure 3.7: Layered Implementation of Blue Gene CHARM++

With these design decisions, we created an implementation of BigSim CHARM++ that shares the code base with the rest of the CHARM++ RTS. With BigSim CHARM++, applications originally written for

CHARM++ can be easily ported to the BigSim CHARM++ running on the emulator.

#### 3.4.2 Experience with the Emulator

The emulator has shown to be very useful for discovering practical constraints such as memory or communication bottlenecks by emulating an application on a very large scale target machine using a much smaller parallel machine. It is also helpful for identifying performance bottleneck in run-times and applications during optimization.

As an example, when we simulated an FEM application on a Blue Gene like machine, we exposed a number of practical bottlenecks to execution on very large machines. These include a limitation of METIS mesh partition tool that failed to partition even a 4K element mesh, and a memory usage bottleneck in AMPI implementation. The detail of these discoveries is presented in Section 5.2.

Simulating load balancing on peta-scale machines also helps us discover a number of memory bottlenecks. For example, we found GreedyCommLB, a greedy centralized load balancer that takes communication into account, uses memory of numPes\*numObjs doubles, where numPes is the number of

processors and numObjs is the number of objects in the application. For example, load balancing an application that has 128K objects running on 32K processors requires 32GB of memory on the central node!

The solution was to avoid the matrix and use a minHeap whose size is only proportional to the numObjs.

Our experience shows that the emulator is very useful in helping developers validate the parallel algorithms in both the run-time system and applications so that they can be debugged and ready to run on a very large parallel machine even before the machine is available. As an example, with off-line debugging and tuning, CHARM++/AMPI porting to IBM Blue Gene/L was done in a day with access to the real machine.

# **Chapter 4**

# **Performance Prediction for CHARM++/AMPI Applications**

The emulator discussed in the previous chapter is useful only for studying programming models and application development issues that arise in the context of peta-scale machines. Specifically, the emulator does not provide detailed performance information.

Developing a simulator for running a large scale application on peta-scale machines can be useful in many ways. From an architecture designer's point of view, it would help to reveal how target applications might perform on large machines for certain machine parameters. If we could simulate how the application would behave on the large machine, we might be able to improve the design of the machine before it is built.